没有合适的资源?快使用搜索试试~ 我知道了~

首页intel i350网卡 reference manual

intel i350网卡 reference manual

需积分: 50 69 下载量 146 浏览量

更新于2023-03-16

评论 3

收藏 7.46MB PDF 举报

关于intel网卡i350的数据手册,适用于进行i350驱动开发的软件工程师使用

资源详情

资源评论

资源推荐

Revision 2.6

October 2017

Document # 336626-001

Intel

®

Ethernet Controller I350

Datasheet

Ethernet Networking Division (ND)

Features

External Interfaces provided:

PCIe v2.1 (2.5GT/s and 5GT/s) x4/x2/x1; called PCIe in this

document.

MDI (Copper) standard IEEE 802.3 Ethernet interface for

1000BASE-T, 100BASE-TX, and 10BASE-T applications

(802.3, 802.3u, and 802.3ab)

Serializer-Deserializer (SERDES) to support 1000BASE-SX/

LX (optical fiber - IEEE802.3)

Serializer-Deserializer (SERDES) to support 1000BASE-KX

(802.3ap) and 1000BASE-BX (PICMIG 3.1) for Gigabit

backplane applications

SGMII (Serial-GMII Specification) interface for SFP (SFP

MSA INF-8074i)/external PHY connections

NC-SI (DMTF NC-SI) or SMBus for Manageability connection

to BMC

IEEE 1149.6 JTAG

Performance Enhancements:

PCIe v2.1 TLP Process Hints (TPH)

UDP, TCP and IP Checksum offload

UDP and TCP Transmit Segmentation Offload (TSO)

SCTP receive and transmit checksum offload

Virtualization ready:

Next Generation VMDq support (8 VMs)

Support of up to 8 VMs per port (1 queue allocated to each

VM)

PCI-SIG I/O SR-IOV support (Direct assignment)

Queues per port: 8 TX and 8 RX queues

Power saving features:

Advanced Configuration and Power Interface (ACPI) power

management states and wake-up capability

Advanced Power Management (APM) wake-up functionality

Low power link-disconnect state

PCIe v2.1 LTR

DMA Coalescing for improved system power management

EEE (IEEE802.3az) for reduced power consumption during

low link utilization periods

IEEE802.1AS - Timing and Synchronization:

IEEE 1588 Precision Time Protocol support

Per-packet timestamp

Total Cost Of Ownership (TCO):

IPMI BMC pass-thru; multi-drop NC-SI

Internal BMC to OS and OS to BMC traffic support

Additional product details:

17x17 (256 Balls) or 25x25 (576 Balls) PBGA package

Estimated power: 2.8W (max) in dual port mode and 4.2W

(max) in quad port mode

Memories have Parity or ECC protection

LEGAL

LNo license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for

a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or

usage in trade.

This document contains information on products, services and/or processes in development. All information provided here is

subject to change without notice. Contact your Intel representative to obtain the latest forecast, schedule, specifications and

roadmaps.

The products and services described may contain defects or errors which may cause deviations from published specifications.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-

4725 or by visiting www.intel.com/design/literature.htm.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries.

* Other names and brands may be claimed as the property of others.

© 2017 Intel Corporation.

2

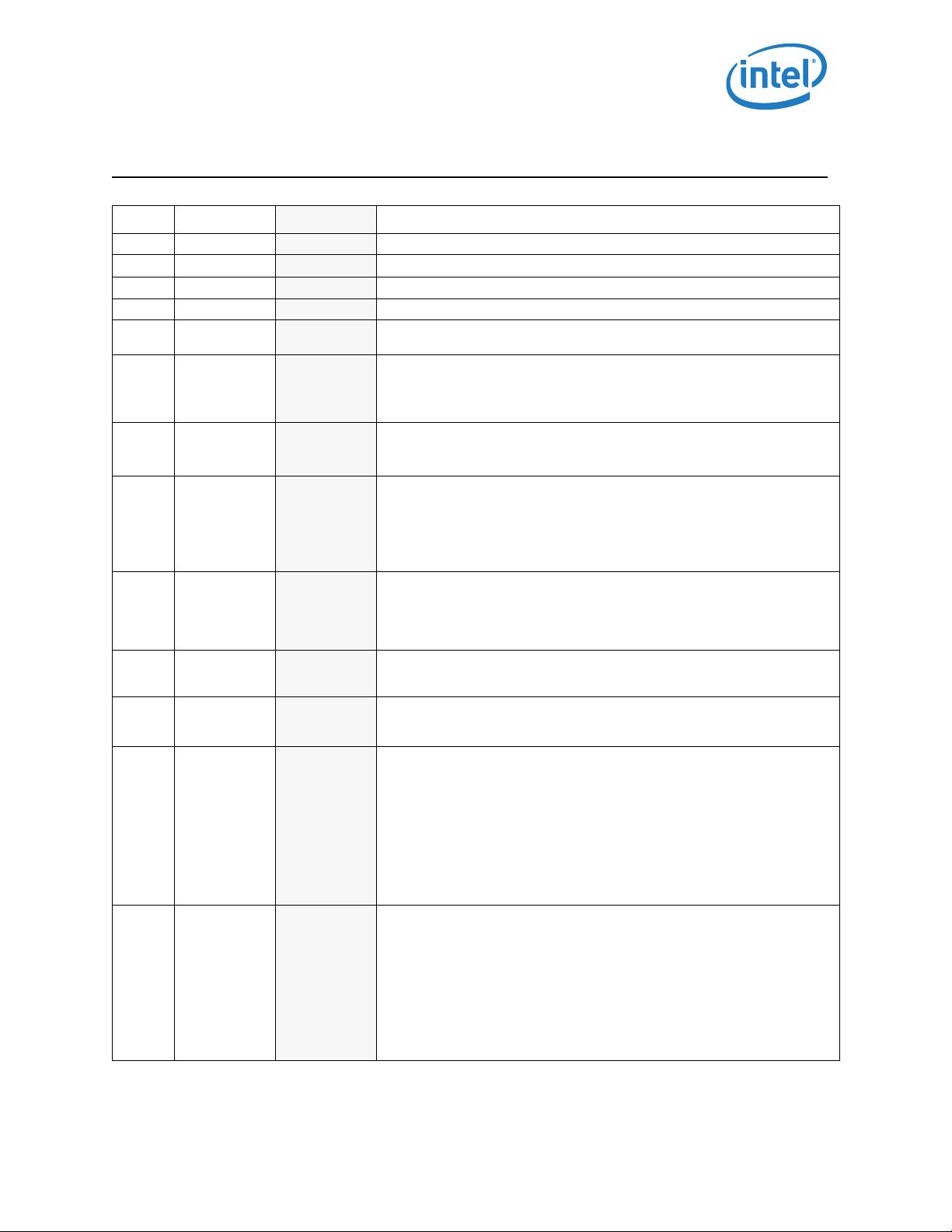

Revision History — Intel

®

Ethernet Controller I350

3

Revision History

Rev Date Comments

.3 1/8/2010

Initial public release.

.5 5/21/2010

Updated using latest internal specs.

1.0 1/7/2011

Updated using latest internal specs.

1.1 4/6/2011

Updated using latest internal specs.

1.9 4/14/2011

Updated with latest internal specs.

Version number moved to 1.9 for PRQ.

1.91 5/6/2011

Added or updated:

• Section 6.4.2, Port Identification LED blinking (Word 0x04)

• Section 13.1, Thermal Sensor and Thermal Diode

• Updated power numbers.

1.92 5/10/2011

Added (improves coverage of 2-port 17X17 package):

• Section 2.2.13, 2-Port 17x17 PBGA Package Pin List (Alphabetical)

• Section 2.2.14, 2-Port 17x17 PBGA Package No-Connect Pins

1.93 5/20/2011

Updated.

• Section 1.6, I350 Packaging Options. Updated to cover both 17x17 options.

• Section 11-5, Flash Timing Diagram. Removed meaningless line from diagram.

• Section 11.7.1.1, 17x17 PBGA Package Schematics. Corrected display issue

with diagram.

2.00 6/23/2011

SRA release.

• RSVD_TX_TCLK was expressed as 1.25MHZ (clock speed). Corrected to

125MHz in two places. See Table 2-10, Analog Pins, Table 2-23, PHY Analog

Pins.

• Section 11.7.2.1, 25x25 PBGA Package Schematics. Diagram updated.

2.01 6/24/2011

• Section 8.5.5, Flow Control Receive Threshold Low - FCRTL0 (0x2160; R/W).

Changed: “at least 1b (at least 16 bytes)” to “3b (at least 48 bytes) Diagram

updated”.

2.02 8/2/2011

• Figure 7-26, Figure 7-26 build issues corrected.

• Section 10.6.3.16, Thermal Sensor Commands. Note added (“Thermal Sensor

configuration can be done only through NC-SI channel 0.”).

2.03 8/25/2011

• Section 6.2.22, Functions Control (Word 0x21), bit 9 note; Section 9.4.11.4,

Base Address Register Fields, bit 9 description. Both contain the updated text:

“This bit should be set only on systems that do not generate prefetchable

cycles.”

• Section 8.26.1, Internal PHY Configuration - IPCNFG (0x0E38, RW) and

Section 8.26.2, PHY Power Management - PHPM (0x0E14, RW); tables

reformatted.

• Table 10-49, Driver Info Host Command, Byte 1; description updated.

• Table 11-6, Power Consumption 2 Ports, D0a - Active Link row, total power

column has been corrected.

2.04 9/16/2011

• Section 5.1.1, PCI Device Power States. Section updated. See text starting

with “The PCIe link state follows the power management state of the device...”

• Section 6.3.11, NC-SI Configuration Module (Global MNG Offset 0x0A).

Register descriptions for a number off offsets have been updated. These

include: Offsets 0x01, 0x03, 0x05, and 0x07

• Table 8-10, Usable FLASH Size and CSR Mapping Window Size. Table added to

Datasheet.

• Table 10-30, Supported NC-SI Commands. “Set Ethernet Mac Address”

corrected to “Set MAC Address”. “Clear Ethernet MAC Address” removed from

supported. This is an obsolete reference.

Intel

®

Ethernet Controller I350 — Revision History

4

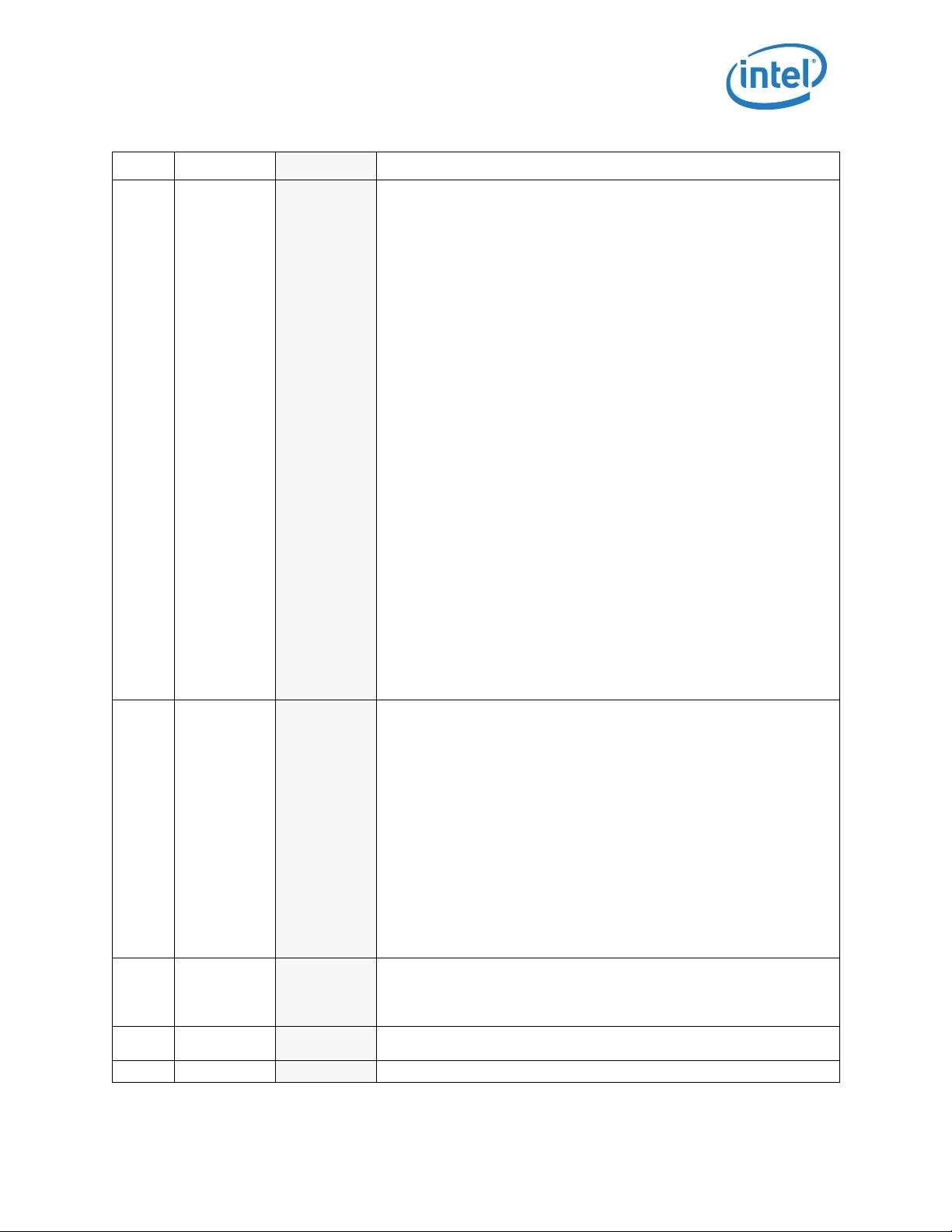

2.05 12/20/2011

• Section 6.3.12.2, Traffic Type Data - Offset 0x1. Default values of 01 added for

all traffic types.

• Section 6.4.9, Reserved/3rd Party External Thermal Sensor – (Word 0x3E).

New reserved section added. Section 8.16.28.1, Time Sync Interrupt Cause

Register - TSICR (0xB66C; RC/W1C). Note in section updated. New text:

“Once ICR.Time_Sync is set, TSICR should be read to determine the actual

interrupt cause and to enable reception of an additional ICR.Time_Sync

interrupt.”

• Figure 12-6: Updated to correct error. Section 12.5, Oscillator Support:

Contains similar update in the section’s first bullet.

2.06 4/10/2012

• Section 3.1.7.9, Completion with Completer Abort (CA). The discussion has

been corrected. The updated paragraph is: “A DMA master transaction ending

with a Completer Abort (CA) completion causes all PCIe master transactions to

stop; the PICAUSE.ABR bit is set and an interrupt is generated if the

appropriate mask bits are set. To enable PCIe master transactions following

reception of a CA completion, software issues an FLR to the right function or a

PCI reset to the device and re-initializes the function(s).”

• Section 6.3.9.17, NC-SI over MCTP Configuration - 0ffset 0x10. Phrase in bit 7

description updated. New text: “If cleared, a payload type byte is expected in

NC-SI over MCTP packets after the packet type...”

• Section 6.4.3, EEPROM Image Revision (Word 0x05). Table updated; bit

assignment descriptions changed. Changed to: 15:12 EEPROM major version;

11:8 are reserved; 7:0 EEPROM minor version. Example given in note.

• Section 9.6.6.2, LTR Capabilities (0x1C4; RW). The reserved fields (bits 15:13

and 31:29) now indicate RO, not RW.

• Figure 11-11 : Coupling cap data in figure corrected;

changed 10pf to 1000pf.

• Table 12-4, Crystal Manufacturers and Part Numbers. Footnote added to table

for 7A25000165. Text states: “This part footprint compatible with X540

designs.”

Rev Date

Comments

Revision History — Intel

®

Ethernet Controller I350

5

2.1 3/22/2013

• Section 2.3.4, NC-SI Interface Pins. Notes added. They specify pull-ups/downs

used when NC-SI is disconnected.

• Section 7.8.2.2.5, Serial ID. New text provided: “The serial ID capability is not

supported in VFs.”

• Section 8.8.10, Interrupt Cause Set Register - ICS (0x1504; WO). Time Sync

(bit 19) exposed.

• Table 11-6, Power Consumption 2 Ports. Some numbers updated. See bold

copy.

• Revised Ta ble 2-15 - 2-Port 17x17 PBGA Package Pin List (Alphabetical); SDP2

and SDP3 connections.

• Revised Section 2.3.8 (Power Supply and Ground Pins); removed C4.

• Revised Section 2.3.9 (25x25 PBGA Package Pin List (Alphabetical); C4 signal

name change.

• Revised Section 3.7.6.3.1 (Setting Powerville to Internal PHY loopback Mode);

added new bullet.

• Revised Section 4.3.5 (Registers and Logic Reset Affects); step 10.

• Revised Section 6.2.17 (PCIe Control 1 (Word 0x1B); bit 14 description.

• Revised Section 6.3.9.17 (NC-SI over MCTP Configuration - 0ffset 0x10); bit 7

description.

•Added Section 6.4.6.11 through Section 6.4.6.18 and (PXE VLAN Configuration

Pointer (0x003C) bit descriptions.

• Revised Table 8-6 - Register Summary); Management Flex UDP/TCP Ports

address.

• Revised Section 8.8.9 (Interrupt Cause Read Register - ICR (0x1500; RC/

W1C); bit 20 description.

• Revised Section 10.5.8.1 (Transmit Errors in Sequence Handling); note after

table 10-10.

• Revised Section 10.7.1.3 (Simplified MCTP Mode); removed payload type

references.

• Revised Section 10.7.4.1 (NC-SI Packets Format).

•Added Section 10.7.4.1.1 (Control Packets).

• Revised Section 10.7.4.1.2 (Command Packets); payload type and message

type.

• Revised Section 10.7.4.1.3 (Response Packets); payload type and message

type.

• Revised Section 11.3.1 (Power Supply Specification); added second footnote.

2.2 1/27/14

•Added Section 3.7.6.6, Line Loopback.

• Section 6.2.24, Initialization Control 3 (LAN Base Address + Offset 0x24) —

Updated description of Com_MDIO field.

• Section 8.1.3, Register Summary — Corrected offset value for VFMPRC in Table

8-6.

• Section 8.27.3, Register Set - CSR BAR — Corrected Virtual Address and

Physical Address Base values for VFMPRC in associated table.

• Section 8.28.43, Multicast Packets Received Count - VFMPRC (0x0F38; RO) —

Corrected address value.

• Section 10.6.2, Supported Features, Table 10-30 — Changed “Supported over

MCTP” value from No to Yes for “Select Package” and “Deselect Package”

commands.

• Figure 11-5 — Changed Output Valid symbol from T

Val

to T

V

to match

description in Table 11-15.

• Figure 11-6 — Changed Output Valid symbol from T

Val

to T

V

to match

description in Table 11-16.

• Section 13.5.4, Package Thermal Characteristics — Revised text related to

Flotherm* models.

2.3

• Updated Section 6.5.7.2.

• Updated Section 11.3.1.

• Updated Section 11.3.1.1.

• Updated Section 13.5.4.

2.4 January 2016

• Updated note under Table 2-20 (NC-SI Interface Pins; changed pull-up to pull-

down for pins NCSI_TXD[1:0]).

2.5 March 2017

• Updated Compatibility Word 3 (Added MAS bit assignments).

Rev Date

Comments

剩余993页未读,继续阅读

MSZJie

- 粉丝: 0

- 资源: 10

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

- MW全能培训汽轮机调节保安系统PPT教学课件.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0