Ordering Information

See Section 1.1

Parts in preproduction, limited

availability. For more information,

contact an NXP representative at

nxp.com.

NXP Semiconductors

Data Sheet: Advance Information

IMX8QXPAEC

Rev. 0, 11/2018

Package Information

21 x 21 mm package case outline

17 x 17 mm package case outline

© 2018 NXP B.V.

PRELIMINARY

This document contains information on a pre-production product. Specifications and

pre-production information herein are subject to change without notice.

1 Introduction

This data sheet contains specifications for the

i.MX 8QuadXPlus and 8DualXPlus processors, which,

along with the i.MX 8DualX processor, comprise the

i.MX 8X Family (for i.MX 8DualX specifications, see

i.MX 8DualX Automotive and Infotainment Processors

[IMX8DXAEC]). The i.MX 8X processors consist of

three to five ARM

®

cores (two to four ARM

Cortex

®

-A35 and one Cortex-M4F). All devices include

separate GPU and VPU subsystems as well as a

failover-ready display controller. Advanced multicore

audio processing is supported by the ARM cores and a

high performance Tensilica

®

HiFi 4 DSP for pre- and

post-audio processing as well as voice recognition. The

i.MX 8X Family supports up to three displays with

multiple display output options, including parallel,

MIPI-DSI, and LVDS. Memory interfaces for this device

include:

• LPDDR4 (no error correcting code [ECC])

• DDR3L (optional ECC)

i.MX 8QuadXPlus and

8DualXPlus Automotive

and Infotainment

Applications Processors

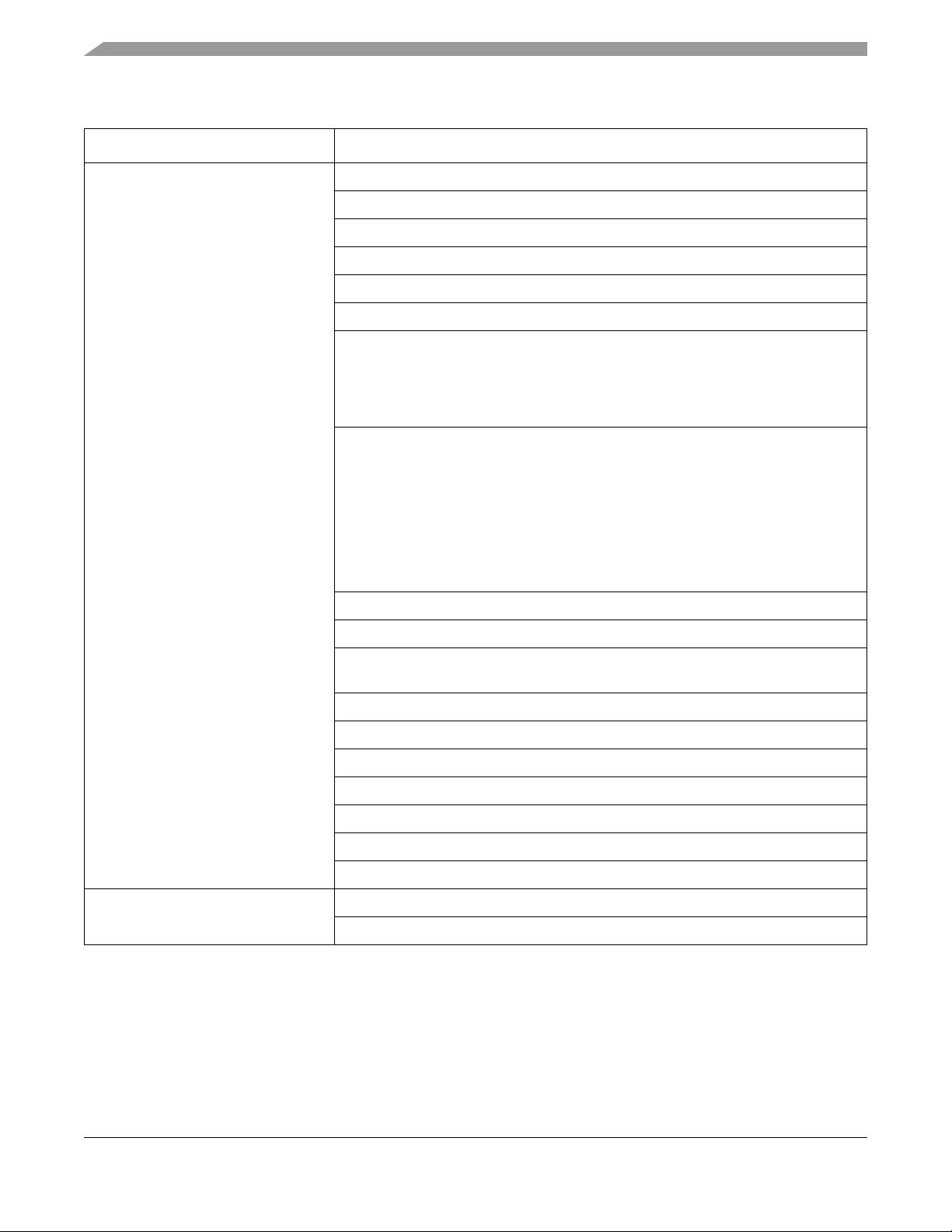

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . 5

2 Architectural Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2.1 Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3 Modules List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.1 Special Signal Considerations. . . . . . . . . . . . . . . . 13

3.2 Recommended Connections for Unused Interfaces13

4 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . 14

4.1 Chip-level conditions . . . . . . . . . . . . . . . . . . . . . . . 14

4.2 Power supplies requirements and restrictions. . . . 25

4.3 PLL electrical characteristics. . . . . . . . . . . . . . . . . 27

4.4 On-chip oscillators. . . . . . . . . . . . . . . . . . . . . . . . . 30

4.5 I/O DC Parameters . . . . . . . . . . . . . . . . . . . . . . . . 33

4.6 I/O AC Parameters . . . . . . . . . . . . . . . . . . . . . . . . 38

4.7 Output Buffer Impedance Parameters. . . . . . . . . . 39

4.8 System Modules Timing . . . . . . . . . . . . . . . . . . . . 43

4.9 General-Purpose Media Interface (GPMI) Timing. 47

4.10 External Peripheral Interface Parameters . . . . . . . 56

4.11 Analog-to-digital converter (ADC) . . . . . . . . . . . . 104

5 Boot mode configuration . . . . . . . . . . . . . . . . . . . . . . . . 107

5.1 Boot mode configuration pins . . . . . . . . . . . . . . . 107

5.2 Boot devices interfaces allocation . . . . . . . . . . . . 107

6 Package information and contact assignments. . . . . . . 109

6.1 FCPBGA, 21 x 21 mm, 0.8 mm pitch . . . . . . . . . 109

6.2 FCPBGA, 17 x 17 mm, 0.8 mm pitch . . . . . . . . . 126

7 Release notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

信息提交成功

信息提交成功

评论0