没有合适的资源?快使用搜索试试~ 我知道了~

首页PCI9052接口芯片的配置及驱动程序开发

PCI9052接口芯片的配置及驱动程序开发

12 下载量 18 浏览量

更新于2023-03-16

评论

收藏 180KB PDF 举报

0 引言 如果把PC机作为控制系统的操作平台,PCI总线作为一种先进的高性能32/64位局部总线正迅速取代原来的ISA总线的主导地位,以用于高速外设,并成为微型计算机系统的主流系统,因而也成为工程开发人员用于工业控制的首选。为了缩短开发周期,一般都采用专用的接口器件。本文就是采用PLX公司的PCI9052来把PCI总线上的操作转换为对局部总线的操作,同时通过双口RAM实现和下位机的存储转接。针对一般PCI总线开发时由于软硬件分离使开发的软硬件不能很好结合的现象,本文结合实例介绍了应用程序并给出了如何通过DriverStudio开发的PCI设备驱动程序来访问PCI设备卡硬件资源的具体程序。

资源详情

资源评论

资源推荐

PCI9052接口芯片的配置及驱动程序开发接口芯片的配置及驱动程序开发

0 引言 如果把PC机作为控制系统的操作平台,PCI总线作为一种先进的高性能32/64位局部总线正迅速取代原

来的ISA总线的主导地位,以用于高速外设,并成为微型计算机系统的主流系统,因而也成为工程开发人员用于

工业控制的首选。为了缩短开发周期,一般都采用专用的接口器件。本文就是采用PLX公司的PCI9052来把PCI

总线上的操作转换为对局部总线的操作,同时通过双口RAM实现和下位机的存储转接。针对一般PCI总线开发时

由于软硬件分离使开发的软硬件不能很好结合的现象,本文结合实例介绍了应用程序并给出了如何通过

DriverStudio开发的PCI设备驱动程序来访问PCI设备卡硬件资源的具体程序。

0 引言

如果把PC机作为控制系统的操作平台,PCI总线作为一种先进的高性能32/64位局部总线正迅速取代原来的ISA总线的主导地

位,以用于高速外设,并成为微型计算机系统的主流系统,因而也成为工程开发人员用于工业控制的首选。为了缩短开发周

期,一般都采用专用的接口器件。本文就是采用PLX公司的PCI9052来把PCI总线上的操作转换为对局部总线的操作,同时通

过双口RAM实现和下位机的存储转接。针对一般PCI总线开发时由于软硬件分离使开发的软硬件不能很好结合的现象,本文结

合实例介绍了应用程序并给出了如何通过DriverStudio开发的PCI设备驱动程序来访问PCI设备卡硬件资源的具体程序。

1 PCI的配置空间及其配置的配置空间及其配置

PCI总线支持存储器地址空间、I/O地址空间和配置空间等三个物理空间。其中,配置空间是PCI总线所特有的一个空

间,PCI总线能实现即插即用的功能,正是通过它特有的配置空间来实现的。PCI配置空间的大小为256字节,分为头标区和

设备有关区。直接影响设备特性的配置寄存器在头标区,其他部分则因设备而异。PCI总线的配置空间通常与PCI接口芯片相

关。该配置空间包括一系列的PCI配置寄存器。本文采用的PCI9052芯片的配置寄存器分为PCI配置寄存器和局部配置寄存

器,二者都可以由PCI总线和串行EEPROM访问。

在PCI配置寄存器中的设备ID、制造商ID、版本号、首区类代码、类别代码、指令寄存器和状态寄存器等寄存器在所有的PCI

设备中都必须实现,具体设置可参考文献[1]。通常情况下,操作系统可使用这些寄存器的内容来决定该PCI设备的加载其驱动

程序。

PCI总线最重要的功能之一是通过基地址寄存器和局部配置寄存器在地址空间重定位PCI设备。系统上电时,通过上层应用软

件能判断系统中存在那些设备,并建立协调的地址映射。所以,基地址寄存器和局部配置寄存器是实现驱动程序的关键。

PCI配置寄存器提供有6个基地址寄存器(BASE0~BASE5)这些基地址都是系统中的物理地址,其中BASE0和BASE1是用来访

问局部配置寄存器的基地址,BASE0是映射到内存的基地址,BASE1是映射到I/O的基地址,可用于通过内存和I/O来访问

局部配置寄存器。这两个基地址可固定用于PCI9052芯片的寄存器操作。

通过BASE2~BASE5四个空间最多可以访问局部端所接的4个芯片,实现4个局部地址空间(局部空间0~3)的PCI总线访问。

PCI总线对局部端所接芯片的局部地址映射是通过4个寄存器组(PCI基地址寄存器,局部范围寄存器,局部基地址寄存器,局

部总线区域描述符)来实现的。这个组定义了每个空间以及相应局部空间的特性。它们将局部端的芯片通过局部端地址(在局部

配置寄存器中设置)翻译成PCI总线地址,也就是将本地的芯片映射到系统的内存或I/O口。而片选信号寄存器则是用来选定这

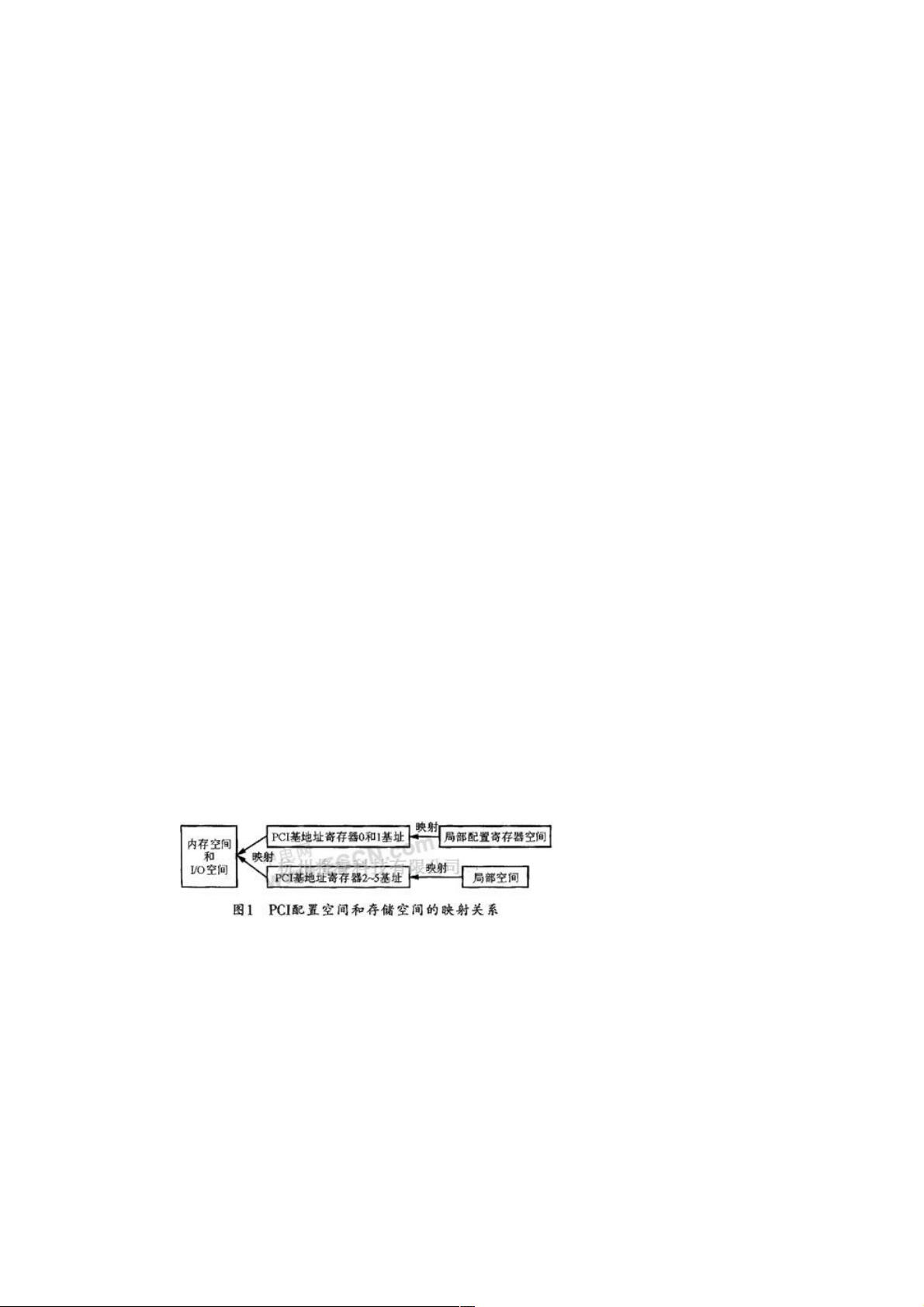

些局部端所接的芯片的。这样,用程序操作这一段内存(或I/O)实际上就是对本地芯片的操作。其映射关系如图1所示。这些

寄存器的内容必须在芯片复位时通过串行E2PROM进行加载,而正确配置E2PROM的内容则是使用PCI9052的关键。

本设计选取LAS0(Local Address Space 0)来访问局部端的双口RAM芯片中的2 KB寻址空间,与其有关的寄存器有四个:

LAS0范围寄存器、LAS0局部基址寄存器、LAS0局部总线区域描述符和片选0基址寄存器。LAS0范围寄存器规定了地址空间

的大小。由于需要2 KB的内存空间,而计算机预留了32 KB空间(即8000H),所以其寄存器值为0xFFFF8000H,而类型则是不

可预取的;LAS0局部基地址寄存器定义了设备卡资源上所占用的基地址,它的最终目的是将这个基地址重新映射到PCI地址

空间。由于基地址必须是32KB的整数倍,因此,为方便起见,可以将基地址定为00000000H,又由于位0为空间使能位,所

以,寄存器的值为00000001H;LAS0局部总线区域描述符用来定义地址空间0的具体工作特性。

该总线采用16位总线宽度,工作方式定义为不使能突发和不预取,因此,该寄存器的数值初步确定为4043A1C0H,最终的值

则需要不断测试才能确定;片选0基址寄存器使用PCI9052的CS0#作为双口RAM的片选信号,CS0#片选信号的起始地址和地

址范围由片选0基址寄存器设置,局部总线的容量是2 KB,第11位为1,基地址是该范围的16倍,一般将倍数放置在范围位之

后,所以寄存器值设置为0xO008401。当从局部空间0基址开始的2 KB空间范围落在CS0基地址寄存器所设置的范围内,CS0

端有效,这种方式可减少地址译码得到的片选逻辑。

用PLX9052可将PCI总线上的操作转换为对局部总线的操作,即通过LAD0~LAD7、RD、WR、CS等对局部端芯片访问。如

果系统分配给本卡的存储空间为FFFF0000H~FFFF7FFFFH。那么,当系统通过PCI总线访问这个区域时,PLX9052就会应

答,并将其转换为局部地址0x0000H~0x07FFH,另外,PLX9052自身也有一些内部寄存器,它们被自动映射到另一片内存

区域,可通过PCI总线直接访问。

PCI9052提供了两种类型的中断源(硬件中断和软件中断)。中断可通过PCI9052中断控制/状态寄存器来(INTCSR)允许和禁

weixin_38672794

- 粉丝: 5

- 资源: 924

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

- MW全能培训汽轮机调节保安系统PPT教学课件.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0