Device Manual

MB86H61

Multi Standard Decoder for Set-Top-Boxes

Copyright© 2010 FUJITSU Microelectronics Europe GmbH Confidential

Disclaimer: The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives

before ordering. The information and circuit diagrams in this document are presented “as is”, no license is granted by implication or otherwise.

July 2010

Edition 1.0

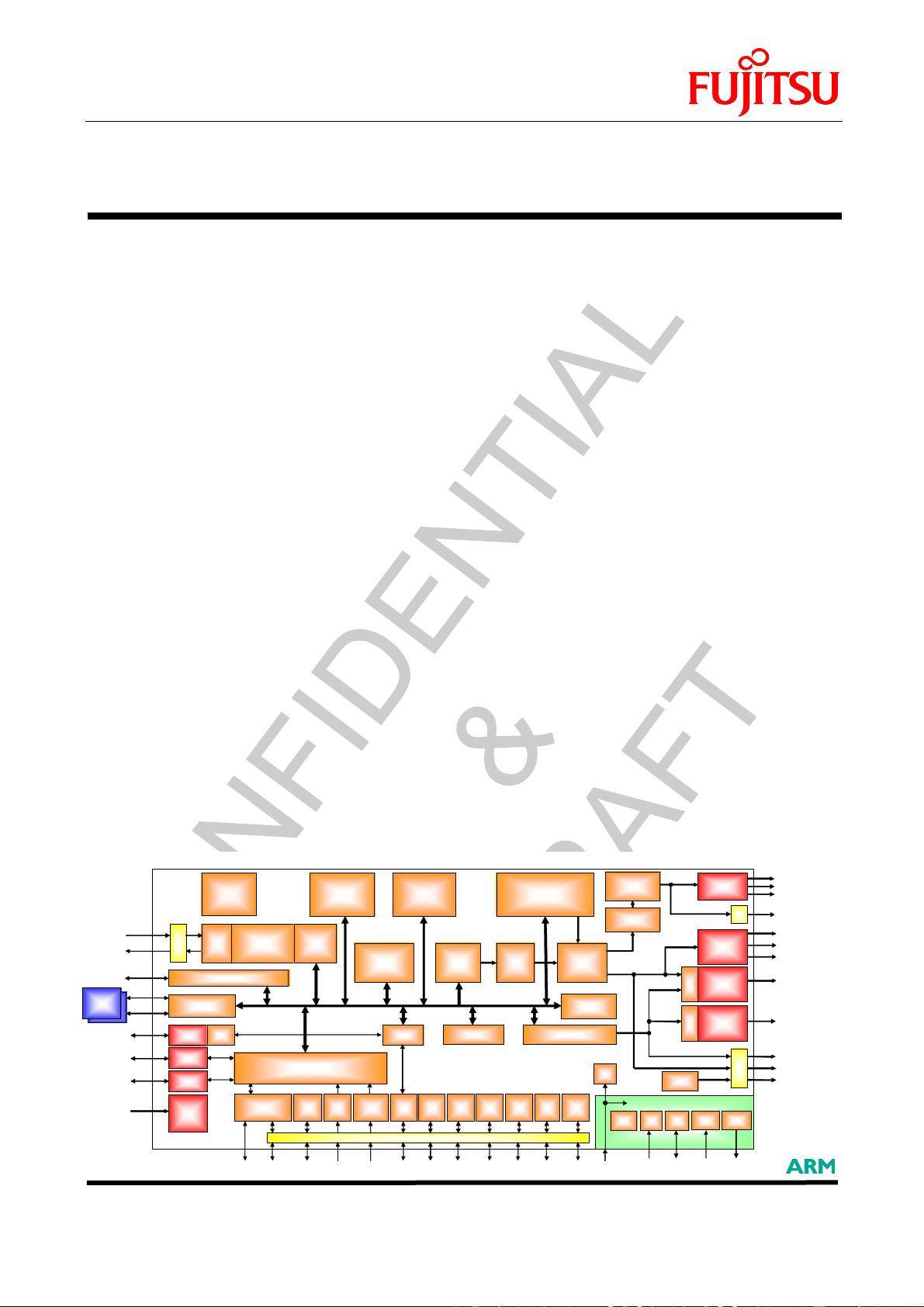

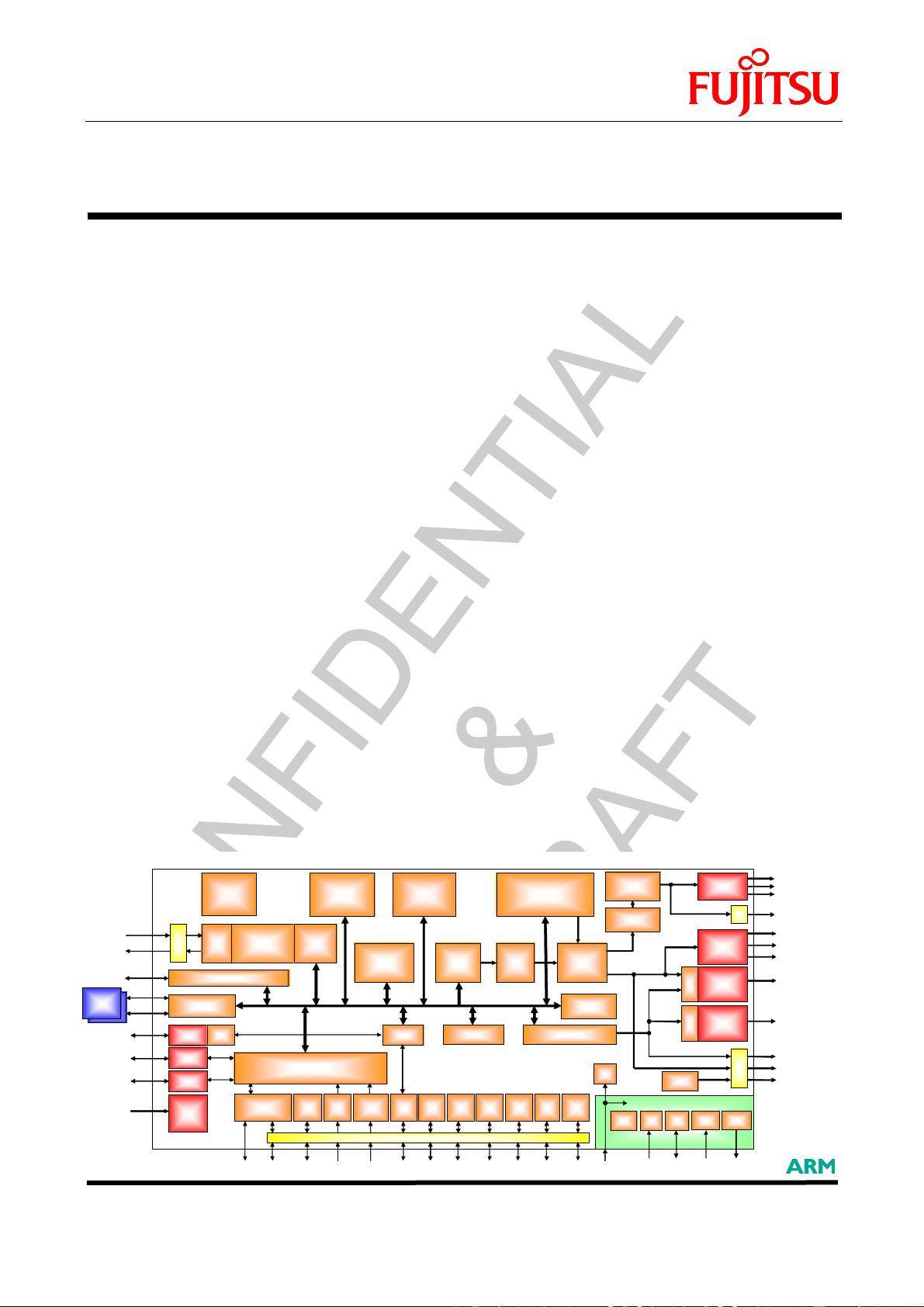

IR

PLL

Wake

up

Power

ctrl

Power Island

CEC

36/27MHz

CCIR /

SMPTE

274M

4x

I2S

UPI

GPIO

ATA

USB

PHY

USB

PHY

DMA

6 channel

Memory

controller

SATA

PHY

DMA

DDR2

800

GPIO

4 x

TSD

Descrambler

DVB CS A2.1

Multi 2

DES/AES

Buffer

Manager

Audio

Decoder

4x I2S out

SPDIF

GPIO

I/P

Converter

Video

Scaler

Display

Mixer

Scaler

(S D)

PAL / NTSC

SECAM

Encoder

Digital RGB

2D-Graphic

Accelerator

10 Bit

ADC

(four

channel)

Front

Panel

control

2x

SPI

2x ISO

7816

2x

UART

SDIO

NAND

Flash

SATA

LINK

NOR Flash

DVB-CI/CI+

SFlash

Ethernet controller

IRQ

Controller

S-Flash

MII

Timer

HDMI Link

GPIO

CVBS

Y/C

RGB

YPbPr

RGB

HDMI 1.3

Audio

L/R

USB 2.0

Host/function

SATA

eSATA

Video

Decoder

BOOT RO M /

Internal RAM

PWM

4 x OSD, Cursor

(with Scaler function)

2x

I2C

ARM1176

MUX

3 x Video

DAC SD

3 x Video

DAC HD

HDMI

(with HDCP)

Stereo

Audio

DAC

CCIR 656

INTRODUCTION

The MB86H61 is a highly integrated HD Multi-Standard Digital

Television Decoder designed to meet the needs of tomorrow’s

HD set-top-box and IDTV market featuring CI+ or embedded

CAS for advanced security. The MB86H61 is a single-chip

video decoder supporting H.264 / AVC, MPEG-2, AVS and

VC-1 video decoding up to high definition resolution with up to

1080p 50/60Hz output.

A high performance ARM 1176JZF-S

TM

CPU with more than

475DMIPS, a 16kB data and instruction caches and TCM is

included. The CPU features an integrated memory

management unit and a floating point co-processor. The chip

uses two DDR2 interfaces in shared memory architecture.

Also integrated is a 2D graphic engine to accelerate OSD.

An advanced, programmable audio processor solution offers

full flexibility. It is capable of decoding MPEG1 layer 1, 2 and 3

(MP3), HE-AAC, Dolby Digital (planning) and Dolby Digital

plus (planning). Available audio outputs are 4x I²S from 8kHz

to 192kHz, SPDIF and stereo audio DAC.

The TV or display can be connected in HD resolution analog

via component output or digital via copy protected HDMI

interface. A down-sampled SD format can be provided in

parallel. Additionally the decoded video can be output via

CCIR656 (SD) or SMPTE 296M/274M (HD).

The MB86H61 supports eSATA/SATA 3Gb/s interface for

external hard disk drives and SDIO e.g. for SDHC memory

cards. Two USB 2.0 ports configurable as host or device and

10/100 Base-T Ethernet MAC are provided for connectivity.

A deep power down mode has been added to allow a system

design with very low power consumption during standby

mode.

The MB86H61 comes with the Fujitsu Driver Application

Programming Interface (FAPI) to help customers achieving the

shortest possible development cycle. FAPI is a complete

driver set allowing fast and efficient customer software design.

FEATURES

System:

• CPU: ARM 1176JZF-S

TM

@ 475DMIPS

• Memory: 2x 16-bit DDR2-800 SDRAM interface.

• Bootdevices: Parallel NOR, NAND or serial flash supported

• Standby: Power Island for deep power down

Video/Audio:

• Transport stream decoder : 4x incl. DVB descramblers

• Cipher engine with DVB CSA 2.1, AES/DES, Multi-2, secure boot,

control word protection, OTP and memory encryption.

• Multi-standard video decoder for H.264/AVC Level 4.1 HP, MPEG-

2 MP@HL, AVS Jizhun Profile Level 6.0, VC-1 AP Level3.

• Video Output: Up to 1080p @ 50/60Hz, 7 layers with flexible order:

backplane, video, cursor, 4xOSD (up to true-color in HD resolution,

one layer scalable with flicker fixer), YCrCb/RGB color space.

• 2D graphic engine

• PAL/NTSC/SECAM encoder incl. Cross color / luminance filters /

Teletext / WSS / CC / VBID insertion

• Audiodecoder: Programmable audio decoder supporting MPEG1

layer 1, 2 and 3 (MP3), HE-AAC, Dolby Digital (planning), Dolby

Digital plus (planning) and others

Interfaces:

• HDMI Link and PHY with HDCP and CEC controller

• 16bit digital video incl. SAV/EAV: 1x Input / 1x Output (compliant to

SMPTE 296M and SMPTE 274M)

• 24bit digital output (compliant to EIA/CAE-861)

• ITU-R 656 video: 2x Input / 1x Output

• 6x analog video DACs for YPrPb/RGB, YC and CVBS

• Stereo audio DACs / I²S: 4x input and 4x output / SPDIF output for

PCM / MPEG /Dolby Digital 5.1

• 2x USB 2.0 incl. PHY (host or device)

• eSATA/SATA incl. PHY (3Gb/s)

• Ethernet 10/100 Base-T MAC (MII)

• Universal processor interface (NAND/NOR,DVB-CI/ CI+,IDE,ATA)

• Universal slave interface (CI, IDE, ATA)

• 96x Shared GPIO, 2x UART, 2x Smart Card, 2x I²C, 4x PWM, IR

Rx, 2x SPI Master/Slave, SDIO, 4x 7-segment LED, 8x Key Input

• 4 channels Analog-Digital Converter (10bit)

Package/Technology:

• PBGA484 Package / Fujitsu CMOS 90nm technology

• Voltage: 1.2V core, 3.3V I/O (5V tolerant input)

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

信息提交成功

信息提交成功

评论5