没有合适的资源?快使用搜索试试~ 我知道了~

首页xilinx最新FIFO Generator v13.2 中文版

资源详情

资源评论

资源推荐

2019/8/4 1.pdf.html

file:///F:/迅雷下载/1.pdf.html 1/92

FIFO Generator v13.2

LogiCORE IP产品指南

PG057 2017年10月4日

Vivado设计套件

2019/8/4 1.pdf.html

file:///F:/迅雷下载/1.pdf.html 2/92

知识产权事实

LogiCORE IP事实表

核心细节

支持的

用户界 面

Native,AXI4-Stream,AXI4,AXI3,AXI4-Lite

资源

提供核心

设计 文件 加密RTL

例

VHDL

约束

模拟

Verilog行为

(2)

N / A

S / W驱动程序

(4)

经过测试的设计流程

设计 入门

模拟

(3)

合成

Xilinx在Xilinx支持网页上提供

工具:发行说明指南。

www.xilinx.com

产品规 格

4

介绍

Xilinx LogiCORE™IP FIFO发生器核心是

完全验证的先进先出(FIFO)存储器需要

按顺序的应用程序的队列存储和检索。核

心提供了一个所有FIFO配置的优化解决方

案并提供最高性能(最高500 MHz)同

时利用最少的资源。通过Vivado®设计套

件交付,您可以自定义宽度,深度,状态

标志,内存类型和写/读端口纵横比。

FIFOGenerator核心支持Native接口

FIFO,AXI存储器映射接口FIFO和AXI4-

Stream接口FIFO。本地接口FIFO核心针对

缓冲,数据宽度转换和时钟域解耦应用程

序,提供有序存储和检索。

AXI存储器映射和AXI4流接口FIFO源自

Native接口FIFO。三个AXI内存映射界面

风格可供选择:AXI4,AXI3和 AXI4-精简

版。

有关每个功能的更多详细信息界面,请参

阅第1章中的功能摘要。

FIFO Generator v13.2

PG057 2017年10月4日

设备

家庭

(1)

UltraScale +™系列,

UltraScale™架构,Zynq®-7000,7系列

支持的

性能和资源利用率网页

设计

试验 台 VHDL

文件

XDC

模型

支持的

Vivado设计套件

对于其他支持的模拟器,请参见Xilinx

设计工具:发行说明指南。

Vivado综合

支持

笔记:

1.有关支持的设备的完整列表,请参阅Vivado IP

目录。

2.行为模型不模拟同步延迟。

详细信息请参见第4章中的模拟。

3.FIFO Generator内核支持UniSim仿真模型。

4.有关支 持的工具版本,请

参阅Xilinx设计

2019/8/4 1.pdf.html

file:///F:/迅雷下载/1.pdf.html 3/92

第1章

PG057 2017年10月4日

www.xilinx.com 五FIFO Generator v13.2

概观

FIFO Generator内核是一个完全验证的先进先出内存队列,可用于任何内存

应用程序需要

有序存储和检索,实现高性能和区域优化设计。该内核为所有FIFO配置提供优化的解决方案

并在使用最少资源的同时提供最高性能(最高500 MHz)。

该内核支持Native接口FIFO,AXI内存映射接口FIFO和AXI4-Stream接口FIFO。AXI存储器映

射和AXI4-Stream接口FIFO是派生自Native接口FIFO。三种AXI Memory Mapped接口样式

可用:AXI4,AXI3和AXI4-Lite。

该核心可以使用IP目录中的Vivado IP定制器作为完整定制已实施控制逻辑的解决方案,包括

读取和管理写指针和生成状态标志。

注意:存储器映射接口FIFO和AXI4-Stream接口FIFO称为“AXI” FIFO“贯穿本文档。

本机接口

FIFO

可以自定义Native接口FIFO以利用Block RAM,分布式RAM或 一些FPGA系列中可用的内置

FIFO资源,可创建高性能,区域优化的FPGA设计。

标准模式和First Word Fall Through是两种可用的操作模式 本机接口FIFO。

2019/8/4 1.pdf.html

file:///F:/迅雷下载/1.pdf.html 4/92

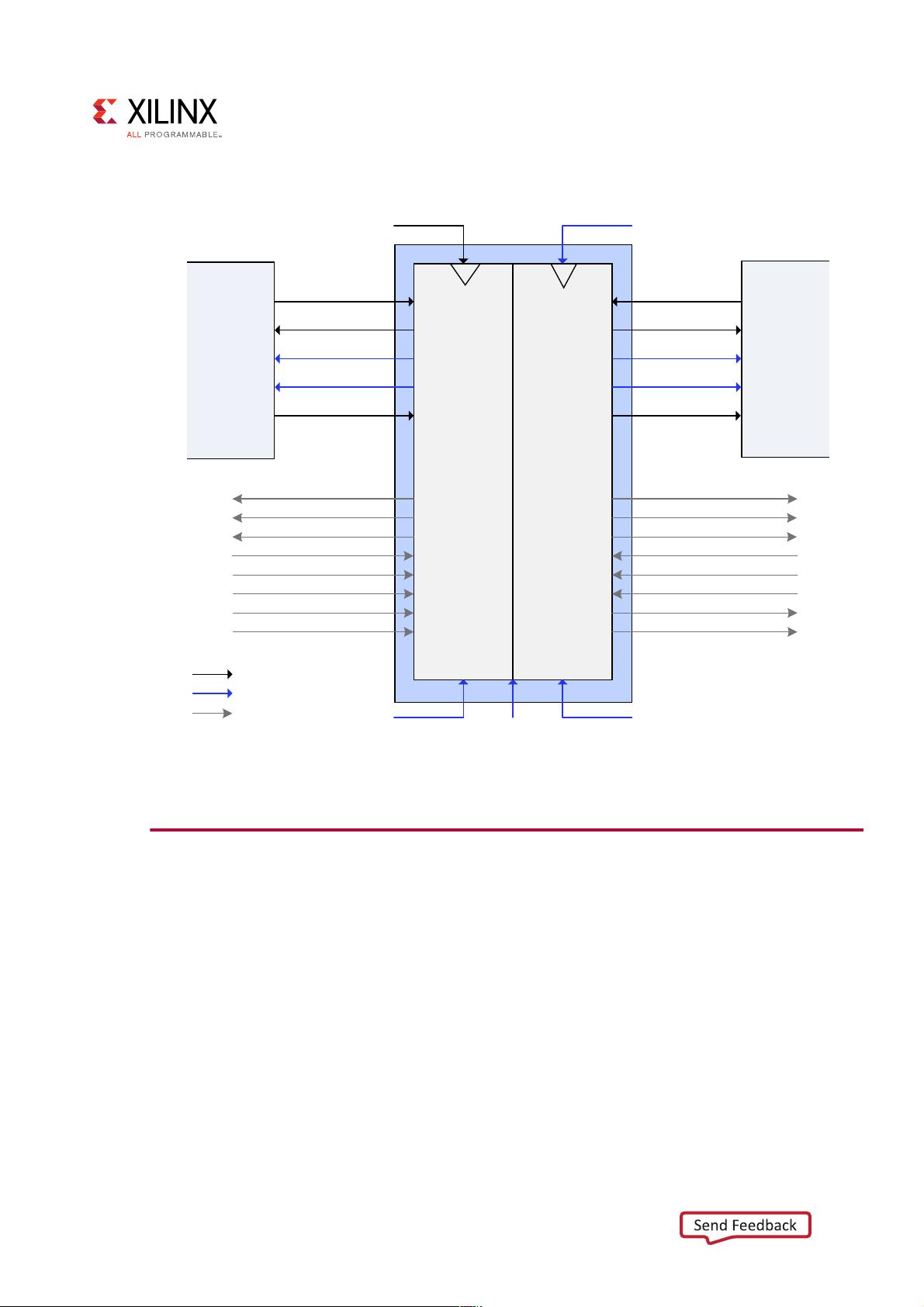

第1章:概述

WR_CLK rd_clk

RD_EN

wr_en

DOUT [M:0]

alomost_full

读代理

Prog_full

DIN [N:0]

写时钟

域

读时钟

域

prog_empty_thresh_negate

prog_empty_thresh

injectdbiterr dbiterr

可选的边带

wr_rst rd_rst

RST

图1-1:本机接口FIFO信号图

PG057 2017年10月4日

www.xilinx.com 6FIFO Generator v13.2

AXI接口

FIFO

AXI接口FIFO来自Native接口FIFO,如图1-2所示。三 提供AXI内存映射接口样式:AXI4,AXI3

和AXI4-Lite。此外 由Native接口FIFO支持的应用程序,AXI FIFO也可用于AXI 系统总线和点对

点高速应用。

AXI接口FIFO不支持内置FIFO和移位寄存器FIFO配置。

在本机接口FIFO支持的相同应用程序中使用AXI FIFO你需要连接到其他AXI功能。AXI FIFO可以

通过集成到系统中使用IP集成商。请参阅“ Vivado Design Suite用户指南:设计IP子系统” 使用

IP Integrator (UG994)[参考5] 了解更多详情。

X-Ref目标 - 图1-1

empty

full

alomost_empty

prog_empty

有效

潜流

prog_empty_thresh_assert

sbiterr

wr_ack

溢出

wr_data_count [P:0]

prog_full_thresh_assert

prog_full_thresh_negate

prog_full_thresh

injectsbiterr

可选的

强制性

写代理

rd_data_count [Q:0]

2019/8/4 1.pdf.html

file:///F:/迅雷下载/1.pdf.html 5/92

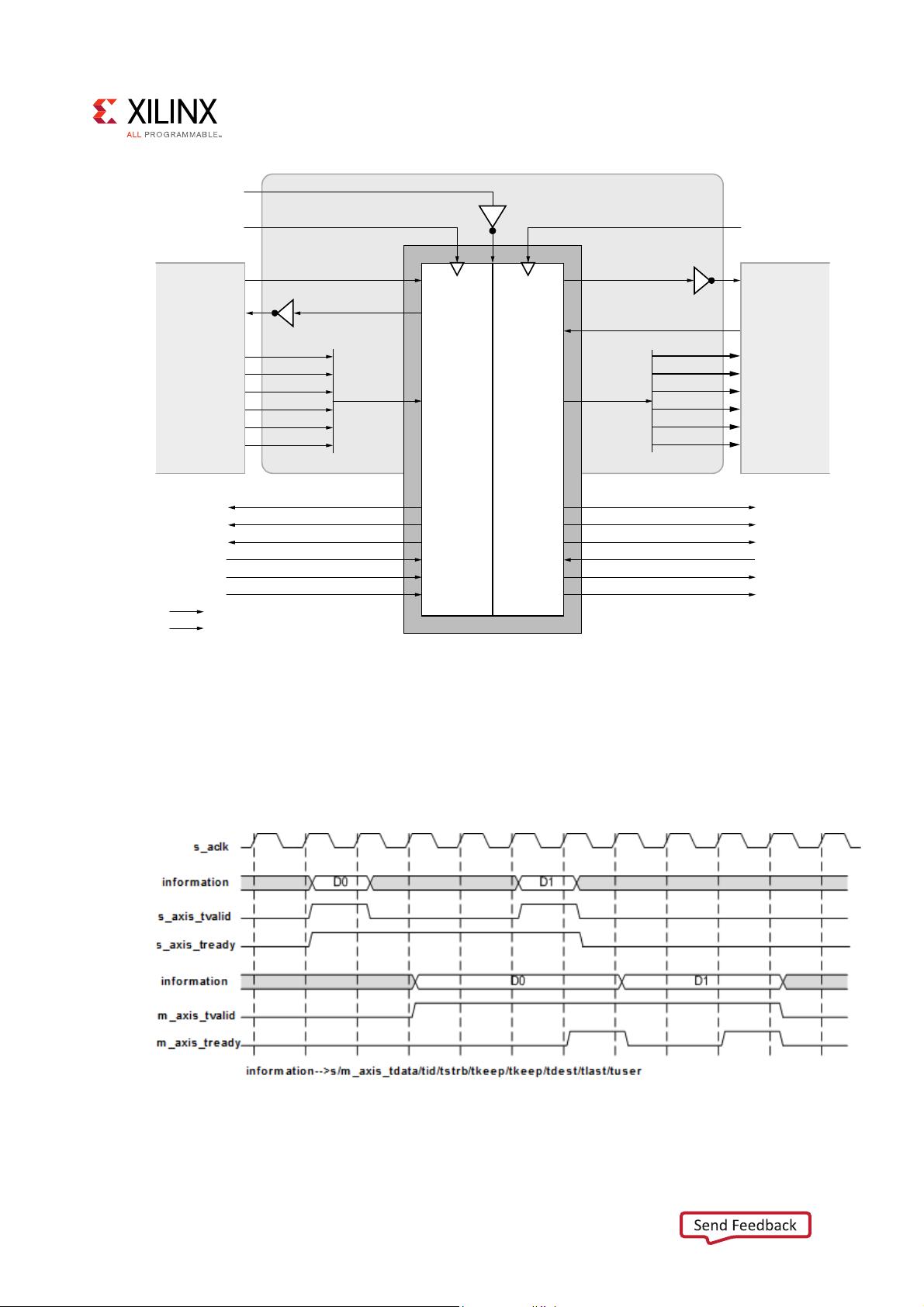

第1章:概述

s_aresetn

s_aclk

WR_CLK rd_clk

m_aclk

*有效

wr_en

充分

RD_EN

*准备

*准备

*频闪

*用户

域

域

DIN [N:0] DOUT [N:0]

---

AXI4 MASTER AXI4 SLAVE AXI4 MASTER AXI4 SLAVE

injectdbiterr dbiterr

X12629

图1-3:AXI4-Stream FIFO时序图

www.xilinx.com 7

PG057 2017年10月4日

FIFO Generator v13.2

X-Ref目标 - 图1-2

图1-2:AXI FIFO推导

AXI接口协议使用双向valid和就绪握手机制。该信息源使用valid 信号来显示有效数据或

控制信息 的时间可在频道上找到。信息目的地使用就绪信号来显示何时它可以接受数据。

图

1-3 显示了写入和读取的示例时序图对AXI4-Stream FIFO的操作,以及图1-4给出了一个

示例时序图 写入和读取操作到AXI存储器映射接口FIFO。

RST

* v a l i d

空

*数据

*频闪

*持续

*用户

*ID

*数据

*持续

*ID

---

写时钟 读时钟

wr_data_count [P:0]

溢出

injectsbiterr

prog_full_thresh

rd_data_count [Q:0]

潜流

sbiterr

prog_empty_thresh

prog_full prog_empty

强制性

可选的边带

剩余218页未读,继续阅读

J_Hang

- 粉丝: 15

- 资源: 15

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

- MW全能培训汽轮机调节保安系统PPT教学课件.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0