没有合适的资源?快使用搜索试试~ 我知道了~

首页100G QSFP28 SR4 光模块数据手册

资源详情

资源评论

资源推荐

AFBR-89CDDZ

QSFP28 Pluggable, Parallel Fiber-Optics Module

100 Gigabit Ethernet Applications

850nm SR4, MMF, MPO Connector

Data Sheet

Description

The Avago Technologies AFBR-89CDDZ is a Four-Channel,

Pluggable, Multi-mode, Fiber-Optic QSFP28 transceiver

for 100 Gigabit Ethernet Applications. This transceiver is

a high performance module for short-range multi-lane

data communication and interconnect applications. It

integrates four data lanes in each direction with each

lane operating at 25.78125 Gbps, giving an aggregated

bandwidth of 103.125 Gbps. It allows optical interoper-

ability up to 100m over an 8- ber (or 12- ber) MPO opti-

cal multi-mode OM4 cable. The push-pull tab facilitates

the insertion and extraction of these transceivers in high

density environment. Each electrical lane operates at

25.78125 Gbps and conforms to the 100GE CAUI4 inter-

face with 802.3 Clause 91 RS-FEC.

Per channel transmitter and receiver retimers, con gured

for 4x25G operation, can be bypassed to enable alterna-

tive data rate transmission.

These modules are designed to operate over multimode

ber systems using a nominal wavelength of 850nm. The

electrical interface uses a 38 contact QSFP28 edge type

connector. The optical interface uses a conventional 8- -

ber (or 12- ber) MPO connector. This module incorpo-

rates Avago Technologies proven integrated circuit and

VCSEL technology to provide reliable long life, high per-

formance, and consistent service.

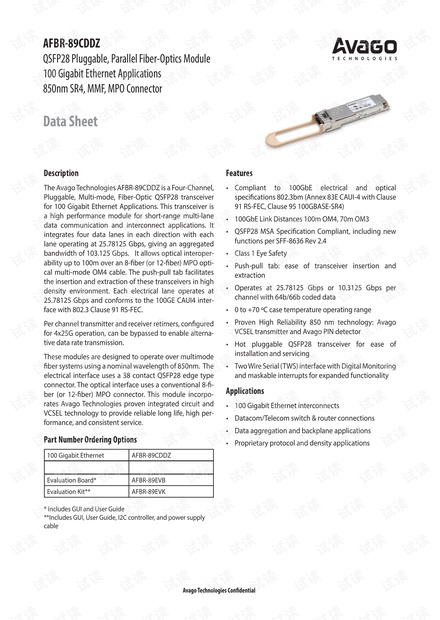

Part Number Ordering Options

100 Gigabit Ethernet AFBR-89CDDZ

Evaluation Board* AFBR-89EVB

Evaluation Kit** AFBR-89EVK

* Includes GUI and User Guide

**Includes GUI, User Guide, I2C controller, and power supply

cable

Features

• Compliant to 100GbE electrical and optical

speci cations 802.3bm (Annex 83E CAUI-4 with Clause

91 RS-FEC, Clause 95 100GBASE-SR4)

• 100GbE Link Distances 100m OM4, 70m OM3

• QSFP28 MSA Speci cation Compliant, including new

functions per SFF-8636 Rev 2.4

• Class 1 Eye Safety

• Push-pull tab: ease of transceiver insertion and

extraction

• Operates at 25.78125 Gbps or 10.3125 Gbps per

channel with 64b/66b coded data

• 0 to +70 ºC case temperature operating range

• Proven High Reliability 850 nm technology: Avago

VCSEL transmitter and Avago PIN detector

• Hot pluggable QSFP28 transceiver for ease of

installation and servicing

• Two Wire Serial (TWS) interface with Digital Monitoring

and maskable interrupts for expanded functionality

Applications

• 100 Gigabit Ethernet interconnects

• Datacom/Telecom switch & router connections

• Data aggregation and backplane applications

• Proprietary protocol and density applications

Avago Technologies Con dential

2

QSFP28 Relevant Speci cations per SFF-8024 (rev 3.3)

Steering

Document

Low Speed, Connector and

Electrical Requirements

Common Management

Spec / Memory Map

Form factor / Module

Mechanical

Cage / Connector Solution

SFF-8665 SFF-8679 SFF-8636 SFF-8661 SFF-8662 and SFF-8663 Style A

SFF-8672 and SFF-8683 Style B

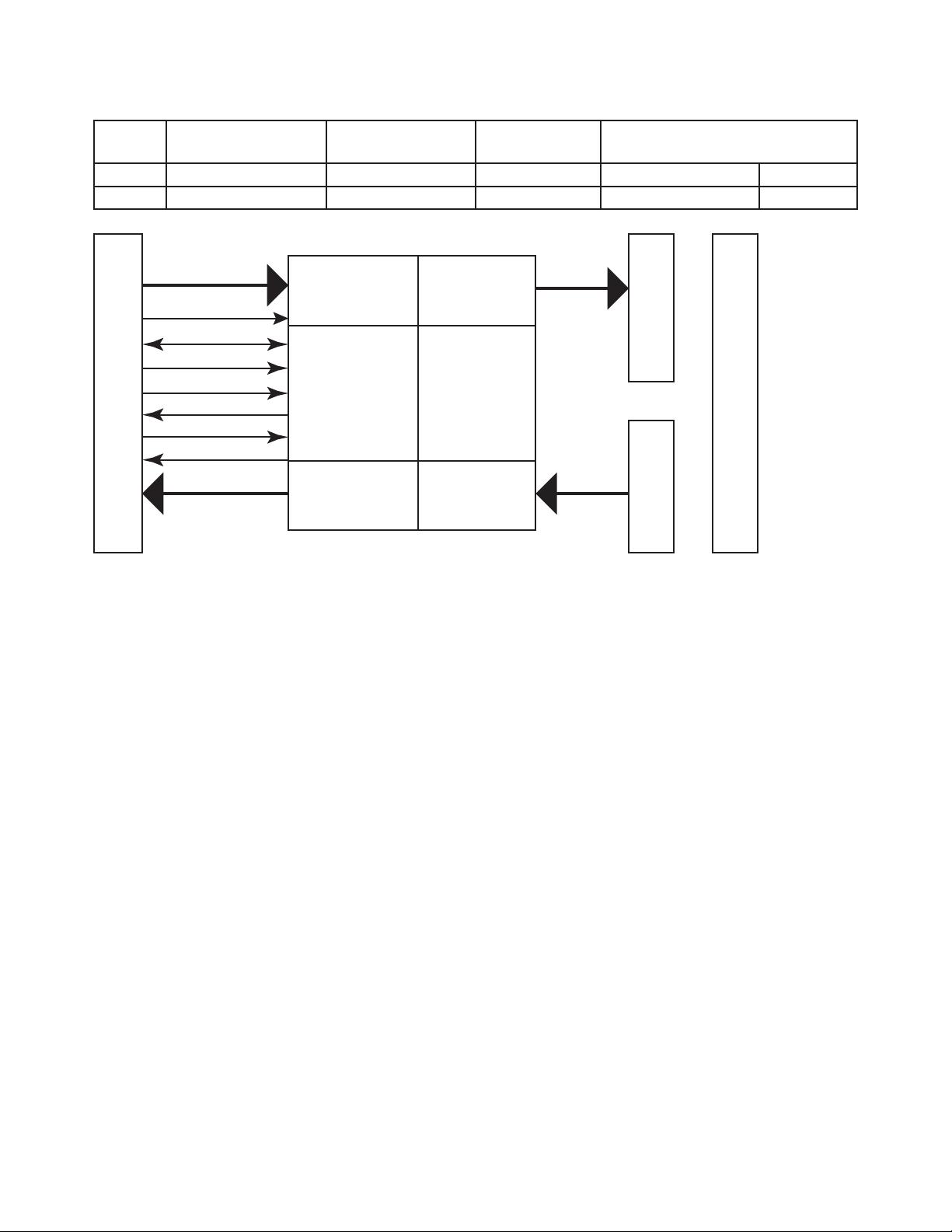

TX EQ & CDRs

4 Channels

Laser Driver

4 Channels

Diagnostic

Monitors

TIA

4 Channels

Control

RX Emph & CDRs

4 Channels

Optical Interface

1×4 VCSEL Array

1×4 PIN Array

Electrical Interface

Din[3:0][p/n] (8)

Dout[3:0][p/n] (8)

SCL

SDA

Mod Sel

LPMode

ModPresL

ResetL

IntL

Figure 1: Transceiver Block Diagram

Transmitter

The optical transmitter portion of the transceiver (see

Figure 1) incorporates a 4-channel VCSEL (Vertical Cav-

ity Surface Emitting Laser) array, a 4-channel Equalization

(EQ) block with integrated CDR and laser driver, diagnos-

tic monitors, control and bias blocks. The transmitter is

designed for IEC-60825 and CDRH eye safety compliance;

Class 1 out of the module. The Tx Input Bu er provides

CML compatible di erential inputs presenting a nominal

di erential input impedance of 100 Ohms. AC coupling

capacitors are located inside the QSFP28 module and are

not required on the host board. For module control and

interrogation, the control interface (LVTTL compatible) in-

corporates a Two Wire Serial (TWS) interface of clock and

data signals. Diagnostic monitors for VCSEL bias, temper-

ature, and power supply voltage are implemented and

results are available through the TWS interface.

Alarm and warning thresholds are established for the

monitored attributes. Flags are set and interrupts gener-

ated when the attributes are outside the thresholds. Flags

are also set and interrupts generated for loss of input sig-

nal (LOS) and transmitter fault conditions. All ags are

latched and will remain set even if the condition initiating

the latch clears and operation resumes. All interrupts can

Avago Technologies Con dential

be masked and ags are reset by reading the appropri-

ate ag register. The optical output will squelch for loss

of input signal unless squelch is disabled. Fault detection

or channel deactivation through the TWS interface will

disable the channel. Status, alarm/warning and fault in-

formation are available via the TWS interface. To reduce

the need for polling, the hardware interrupt signal is pro-

vided to inform hosts of an assertion of alarm, warning,

LOS and/or Tx fault.

Receiver

The optical receiver portion of the transceiver (see Fig-

ure 1) incorporates a 4-channel PIN photodiode array, a

4-channel TIA array, and a 4 channel line driver with in-

tegral CDR, diagnostic monitors, control and bias blocks.

The Rx Output Bu er provides CML compatible di eren-

tial outputs for the high speed electrical interface pre-

senting nominal single-ended output impedances of 100

Ohms di erentially that should be di erentially terminat-

ed with 100 Ohms. AC coupling capacitors are located in-

side the QSFP28 module and are not required on the host

board. Diagnostic monitors for optical input power are

implemented and results are available through the TWS

interface.

3 Avago Technologies Con dential

Alarm and warning thresholds are established for the

monitored attributes. Flags are set and interrupts gener-

ated when the attributes are outside the thresholds. Flags

are also set and interrupts generated for loss of optical in-

put signal (LOS). All ags are latched and will remain set

even if the condition initiating the ag clears and opera-

tion resumes. All interrupts can be masked and ags are

reset upon reading the appropriate ag register. The elec-

trical output will squelch for loss of input signal (unless

squelch is disabled) and channel de-activation through

TWS interface. Status and alarm/warning information

are available via the TWS interface. To reduce the need

for polling, the hardware interrupt signal is provided to

inform hosts of an assertion of alarm, warning and/or LOS.

High Speed Electrical Signal Interface

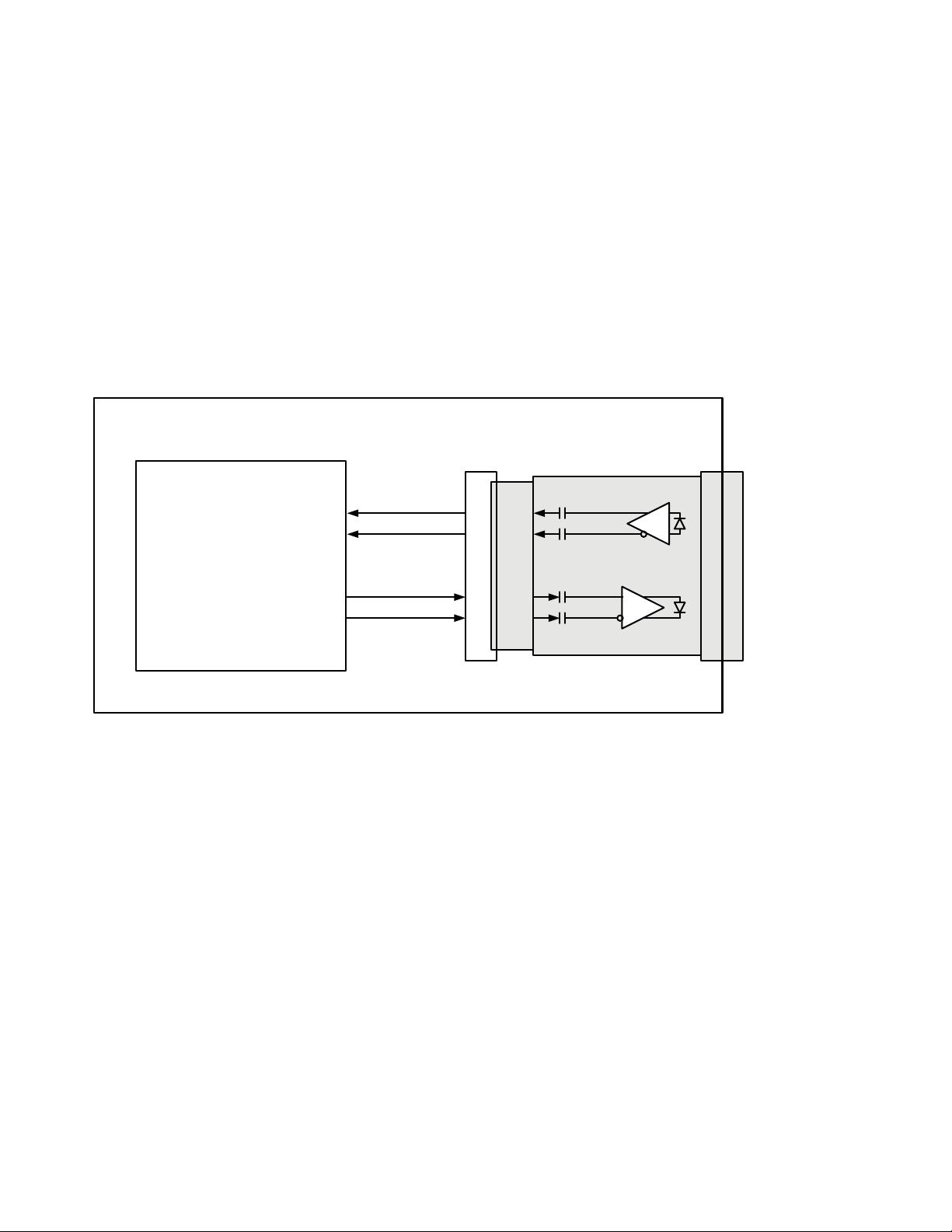

Figure 2 shows the interface between an ASIC/SerDes

and the QSFP28 module. For simplicity, only one chan-

nel is shown. The high speed signal lines are AC-coupled

100 Ohm di erential lines. The AC coupling is inside the

QSFP28 module and not required on the host board. The

100 Ohm di erential terminations are inside the QSFP28

module for the transmitter lines and at the host ASIC/

SerDes for the Receiver lines.

ASIC (SerDes)

Rx 1

Rx 2

Rx 3

Rx 4

Tx 4

Tx 3

Tx 2

Tx 1

Module Card Edge

(Host Interface)

Optical Connector/Port

(Optical Interface)

Tx In p

Tx In n

Rx Out p

Rx Out n

Host Board

(Only one channel shown for simplicity)

QSFP28 Module

Rx

Tx

Host Edge Card Connector

Figure 2: Application Reference Diagram

4

Avago Technologies Con dential

Control Signal Interface

The module has the following low speed signals for con-

trol and status: ModSelL, LPMode, ResetL, ModPrsL, IntL.

In addition, there is an industry standard two wire serial

interface scaled for 3.3 volt LVTTL. It is implemented as a

slave device. Signal and timing characteristics are further

de ned in the Control Characteristics and Control Inter-

face & Memory Map sections.

The registers of the serial interface memory are de ned in

the Control Interface & Memory Map section.

Digital Diagnostic Monitoring

The information provides opportunity for predictive fail-

ure identi cation, compliance prediction, fault isolation

and component monitoring.

Predictive Failure Identi cation – The diagnostic infor-

mation allows the host system to identify potential link

problems. Once identi ed, a “failover” technique can be

used to isolate and replace suspect devices before system

uptime is impacted.

Compliance Prediction – The real-time diagnostic pa-

rameters can be monitored to alert the system when op-

erating limits are exceeded and compliance cannot be

ensured. As an example, the real time average receiver

optical power can be used to assess the compliance of the

cable plant and remote transmitter.

Fault Isolation – The diagnostic information can allow

the host to pinpoint the location of a link problem and ac-

celerate system servicing and minimize downtime.

Component Monitoring – As part of host system quali-

cation and veri cation, real time transceiver diagnostic

information can be combined with system level monitor-

ing to ensure performance and operating environment

are meeting application requirements.

Digital diagnostic monitoring for the following attributes

is implemented.

Transceiver module temperature

Represents the module case temperature (lower page 0

bytes 22-23)

Transceiver module power supply

Reports the module +3.3V supply voltage (lower page 0

bytes 26-27)

Transmitter output power

Reports the average output optical power for each trans-

mitter channel (lower page 0 bytes 50-51 for ch.1, bytes

52-53 for ch.2, bytes 54-55 for ch.3, bytes 56-57 for ch.4)

Transmitter laser bias current

Reports the DC laser bias current for each transmitter

channel (lower page 0 bytes 42-43 for ch.1, bytes 44-45 for

ch.2, bytes 46-47 for ch.3, bytes 48-49 for ch.4)

Receiver input power

Reports the average input optical power for each receiver

channel (lower page 0 bytes 34-35 for ch.1, bytes 36-37 for

ch.2, bytes 38-39 for ch.3, bytes 40-41 for ch.4)

All diagnostic monitor attributes are two-byte elds. To

maintain coherency, the host must access these with sin-

gle two-byte read sequences.

For each monitored attribute, alarm and warning thresh-

olds are established. Flags are set and interrupts gener-

ated when the attributes are outside the thresholds. All

ags are latched and will remain set even if the condition

initiating the ag clears. A mask bit that can be set to pre-

vent assertion of interrupt for each individual attribute ex-

ists for every monitor ag. Entries in the mask elds are

volatile.

5

Avago Technologies Con dential

Package Outline

The module is designed to meet the package outline de-

ned in the QSFP28 SFF-8661 speci cation. See the pack-

age outline for details.

Handling and Cleaning

The transceiver module can be damaged by exposure to

current surges and over voltage events. Care should be

taken to restrict exposure to the conditions de ned in

the Absolute Maximum Ratings. Wave soldering, re ow

soldering and/or aqueous wash process with the mod-

ules on board are not recommended. Normal handling

precautions for electrostatic discharge sensitive devices

should be observed.

Each module is supplied with an inserted port plug for

protection of the optical ports. This plug should always

be in place whenever a ber cable is not inserted.

The optical connector includes recessed elements that

are exposed whenever a cable or port plug is not inserted.

Prior to insertion of a ber optic cable, it is recommended

that the cable end be cleaned to avoid contamination from

the cable plug. The port plug ensures the optics remains

clean and no additional cleaning should be needed. In

the event of contamination, dry nitrogen or clean dry air

at less than 20 psi can be used to dislodge the contamina-

tion. The optical port features (e.g. guide pins) preclude

use of a solid instrument. Liquids are also not advised.

剩余39页未读,继续阅读

hyde8410

- 粉丝: 0

- 资源: 4

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 27页智慧街道信息化建设综合解决方案.pptx

- 计算机二级Ms-Office选择题汇总.doc

- 单链表的插入和删除实验报告 (2).docx

- 单链表的插入和删除实验报告.pdf

- 物联网智能终端项目设备管理方案.pdf

- 如何打造品牌的模式.doc

- 样式控制与页面布局.pdf

- 武汉理工Java实验报告(二).docx

- 2021线上新品消费趋势报告.pdf

- 第3章 Matlab中的矩阵及其运算.docx

- 基于Web的人力资源管理系统的必要性和可行性.doc

- 基于一阶倒立摆的matlab仿真实验.doc

- 速运公司物流管理模式研究教材

- 大数据与管理.pptx

- 单片机课程设计之步进电机.doc

- 大数据与数据挖掘.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0