没有合适的资源?快使用搜索试试~ 我知道了~

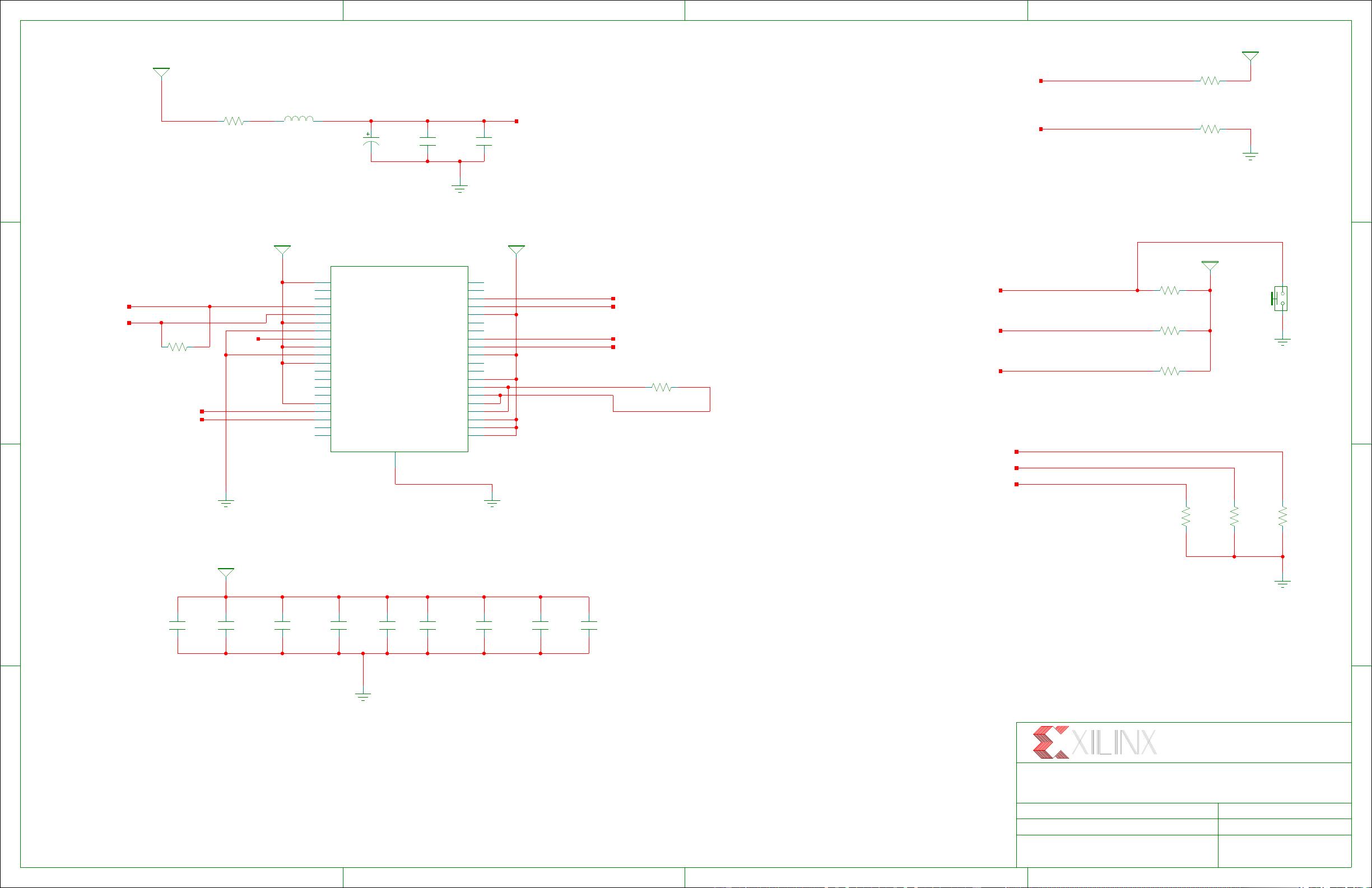

首页Xilinx Virtex-4 ML410开发板 原理图 强烈推荐

资源详情

资源评论

资源推荐

SCH P/N

Sheet

Date:

Title:

Ver:

A

B

C

D

1234

D

C

B

A

4 3 2 1

Sheet Size: B Rev:

Drawn Byof

ART P/N

FAB P/N

0531499

1280372

0381203

NOSTUFF ITEMS ARE NOT POPULATED ON THE PCB.

NOSTUFF DISCRETES AND COMPONENTS.

NOTE: PLEASE REVIEW THE ML410 BOM FOR ITEMS DESIGNATED AS "NOSTUFF".

PCB ARTWORK

XILINX PART NUMBERS

SCHEMATICS

PCB FABRICATION

THE ML410 BOM CONTAINS THE MOST ACCURATE INFORMATION ABOUT

0531499

1280372

0381203

03

E

TABLE OF CONTENTS

72

8-22-2006_9:53

1

SS

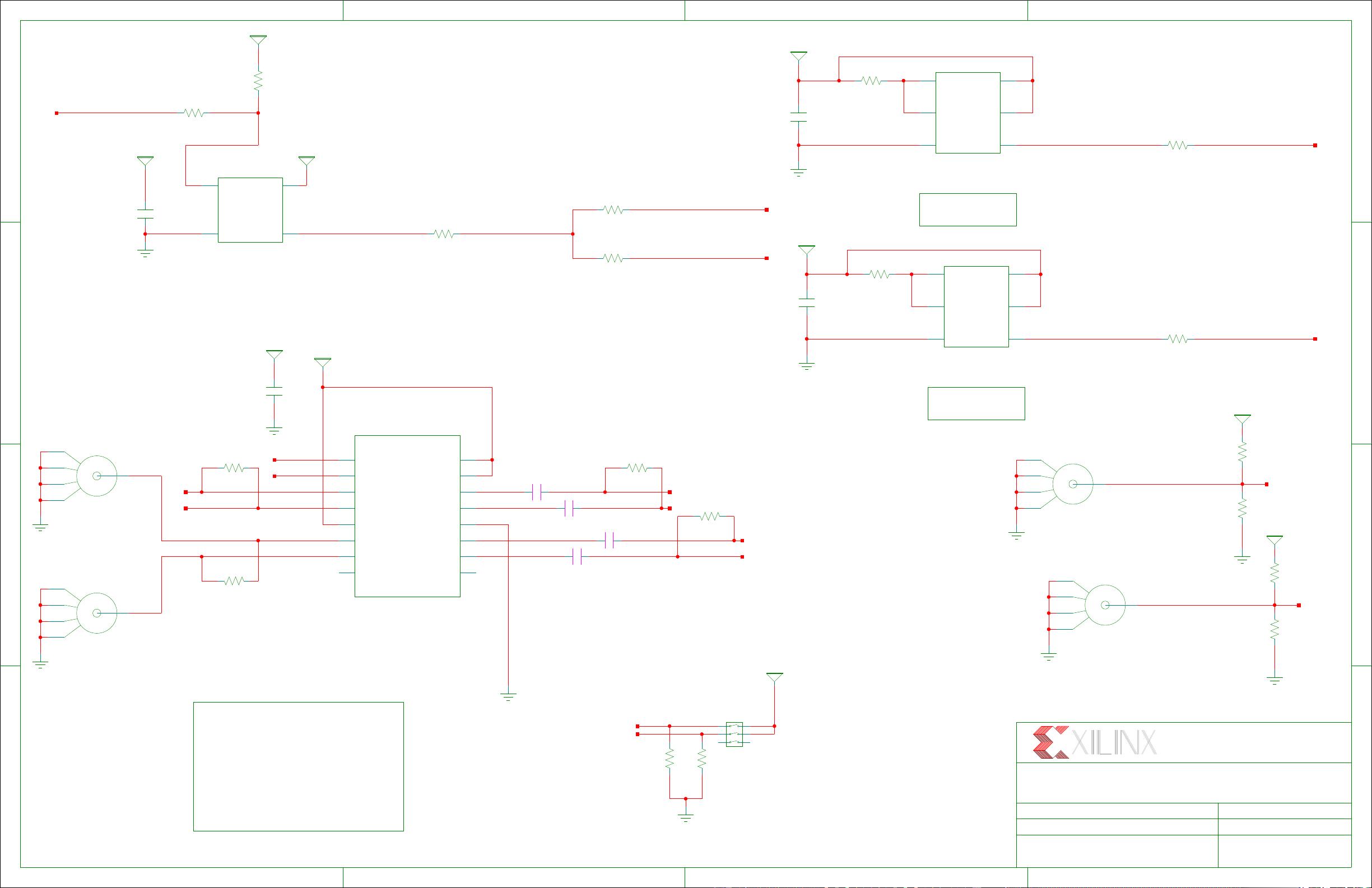

SCHEM, ROHS COMPLIANT, ML410 VIRTEX-4 EVAL PLAFTORM

CON_SMA_ST

VCC3V3

VCC2V5

SOCKETED

14-PIN DIP

VCC2V5

VCC2V5 VCC2V5

SOCKETED

14-PIN DIP

CON_SMA_ST

CON_SMA_ST

CON_SMA_ST

VCC2V5

OE

GND OUT

VCC

33.0000MHZ

SG-636PDE

OSC

PKG_TYPE=TSSOP-16

DEVICE=DS90CP22

OUT1-

OUT1+

GND

OUT0-

OUT0+

EN1

EN0

IN1-

IN1+

VCC

IN0-

IN0+

SEL0

SEL1

NC1NC

VCC3V3

VCC3V3

VCC3V3

VCC2V5

VCC2OE2

VCC1

GND OUT

OE1

SG-531PCW

OSC

XXXMHZ

GND OUT

VCC1

VCC2OE2

OE1

MB2100H

OSC

100MHZ

SCH P/N

Sheet

Date:

Title:

Ver:

A

B

C

D

1234

D

C

B

A

4 3 2 1

Sheet Size: B Rev:

Drawn Byof

ART P/N

FAB P/N

0531499

1280372

0381203SEL0 SEL1 Q0 Q1

0 1 IN0 IN1

1 0 IN1 IN0

1 1 IN1 IN1

0 0 IN0 IN0

Place R53,R54 close to U37

E

03

2

8-22-2006_9:53

72

SS

CLKS: USR,MGT,SYSACE

SCHEM, ROHS COMPLIANT, ML410 VIRTEX-4 EVAL PLAFTORM

7 8

14

114

1

X6

NOSTUFF

114

14

7 8

1

X10

CLK_SEL0

CLK_SEL1

SGMIICLK_NQO

SGMIICLK_QO

R53

100-DNP

R54

100-DNP

1

2

0.01UF

C591

1

2

0.01UF

C526

1

2

0.01UF

C525

9

10

11

12

13

14

15

16

8

7

6

5

4

3

2

1

U6

1

2

0.01UF

C590

R411

34.0

1

2 3

4

X8

CLK_SEL1

CLK_SEL0

R29

4.7K

R28

80.6

5

4

3

2

1

J21

5

4

3

2

1

J20

5

4

3

2

1

J17

130

R407

0.1UF

C193

1

2

3 4

5

6

SW6

R30

4.7K

XS10

R448

4.75K

R447

24.9

0.1UF

C581

6

USER_CLK2USER_CLK2_R

R410

34.0

18.2

R412

0.1UF

C542

0

R422

R421

4.75K

SYSACE_FPGA_CLK

9

SYSACE_CLK_R

SYSACE_CLK_OE

5

20

SYSACE_CLK

5

USER_SMA_CLK_P

XS6

24.9

R366

C446

0.1UF

R367

4.75K

10

USER_CLKSYSUSER_CLKSYS_R

SYSACE_CLK_OSC

MGTCLK_P_110

MGTCLK_N_110

R200

100

CLK125_NQO

CLK125_QO

R282

100

MGT_SMA_CLK_P

MGT_SMA_CLK_N

R375

80.6

5

4

3

2

1

J36

130

R297

USER_SMA_CLK_N

5

VCC2V5

LT1763CS8

BYP

GND3

GND6

GND7

IN OUT

ADJ

SHDN

VCC3_PCI

VCC5V

SCH P/N

Sheet

Date:

Title:

Ver:

A

B

C

D

1234

D

C

B

A

4 3 2 1

Sheet Size: B Rev:

Drawn Byof

ART P/N

FAB P/N

0531499

1280372

0381203

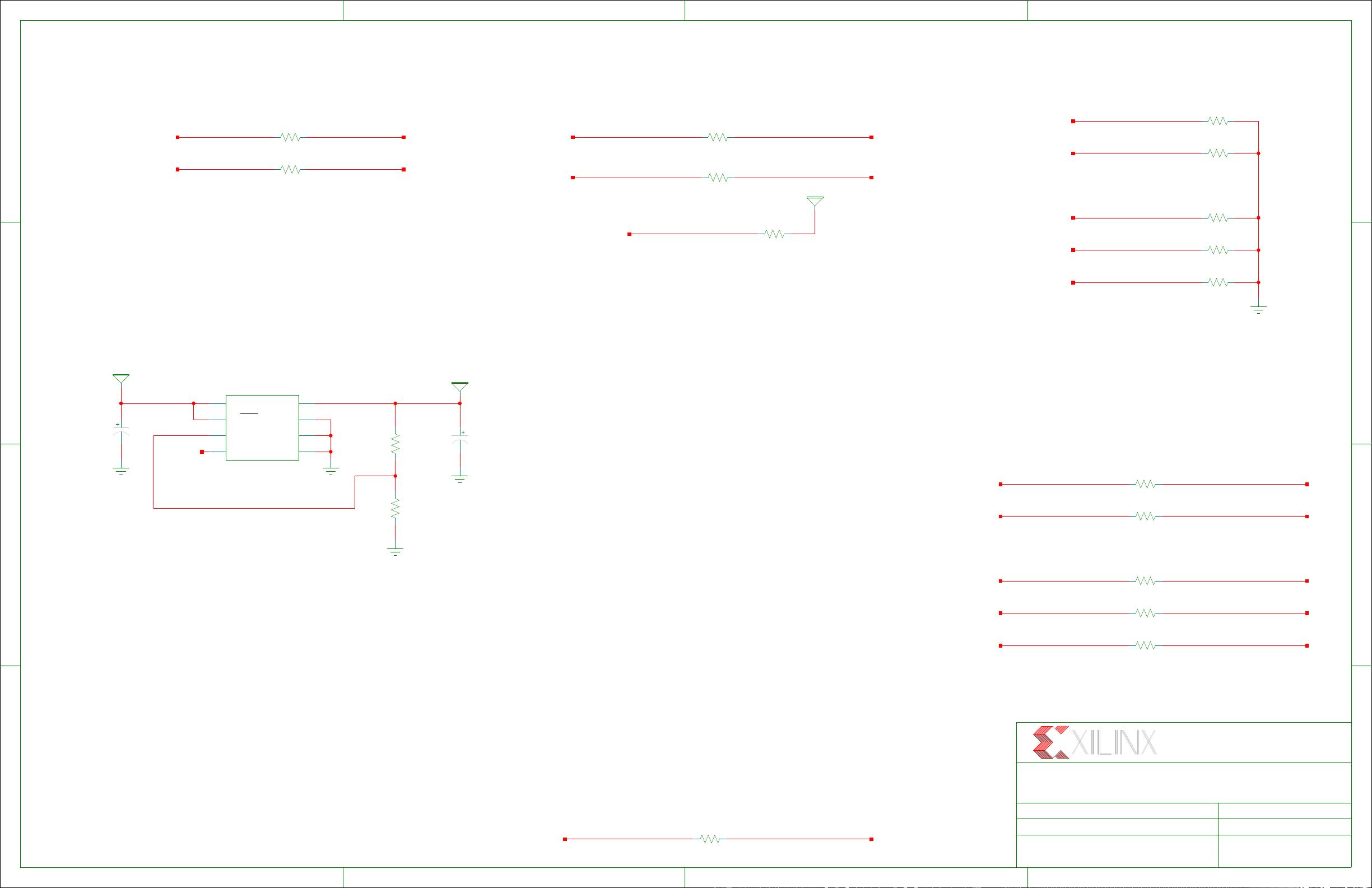

NOTE: TRC_CLK RESISTOR ALLOWS CLOCK TERMINATION

TO BE ADJUSTED INDEPENDENTLY OF OTHER I/O.

THE VALUES ARE UNUSUAL RELATIVE TO THE LT1763 DATASHEET.

FROM XAPP653. THIS DESIGN IS INTENDED TO SINK CURRENT

1206 1206

THROUGH THE 1206 RESISTORS WHEN THE CLAMP DIODES ON

THE FPGA ARE CONDUCTING DURING OVERSHOOT. THIS IS WHY

NOTE: THE COMPONENT VALUES FOR THIS REGULATOR ARE TAKEN

CLOCKS BE PULLED LOW WHEN THE

NOTE: THE PCI SPEC RECOMMENDS THAT

BUS IS NOT ACTIVELY CLOCKED.

NOTE: PCI_CLK RESISTORS ALLOW CLOCK TERMINATION

TO BE ADJUSTED INDEPENDENTLY OF OTHER I/O.

E

03

SS

72

8-22-2006_9:53

3

PCI_SUPPLY ........

SCHEM, ROHS COMPLIANT, ML410 VIRTEX-4 EVAL PLAFTORM

R2

4.75K

R438

24.9

PCI_P_CLK4_R

7

7

PCI_P_CLK5_R

7,25

PCI_P_CLK4

PCI_P_CLK5

6,7

R435

0

PCI_FPGA_IDSEL

7

PCI_P_AD24

7,25,27,29,31,33

R437

24.9

R434

24.9

PCI_P_CLK3_R PCI_P_CLK3

7,33

R49

24.9

PCI_P_CLK1_R PCI_P_CLK1

7,29

R50

24.9

PCI_P_CLK0_R

7,27

PCI_P_CLK0

R382

4.75K

R439

4.75K

R164

4.75K

R1

4.75K

7,25

PCI_P_CLK4

PCI_P_CLK5

6,7

PCI_P_CLK3

7,33

PCI_P_CLK1

7,29

7,27

PCI_P_CLK0

R427

0

R426

0

FPGA_SCL

6

IIC_SCL

IIC_SDA FPGA_SDA

6

26.1

R454

38.3

R455

2

1

C237

3.3UF

6.3V

22UF

C236

10V

4

3

6

7

8 1

2

5

U41

NC

24.9

R31

R440

4.75K

9,19,20,46

FPGA_INIT

TRC_CLK

19

TRC_CLK_R

9

24.9

R545

19

ATCB_CLK

9

ATCB_CLK_R

VCC3V3

VCC2V5

VCC2V5

VCC2V5

VCC3V3

SCH P/N

Sheet

Date:

Title:

Ver:

A

B

C

D

1234

D

C

B

A

4 3 2 1

Sheet Size: B Rev:

Drawn Byof

ART P/N

FAB P/N

0531499

1280372

0381203

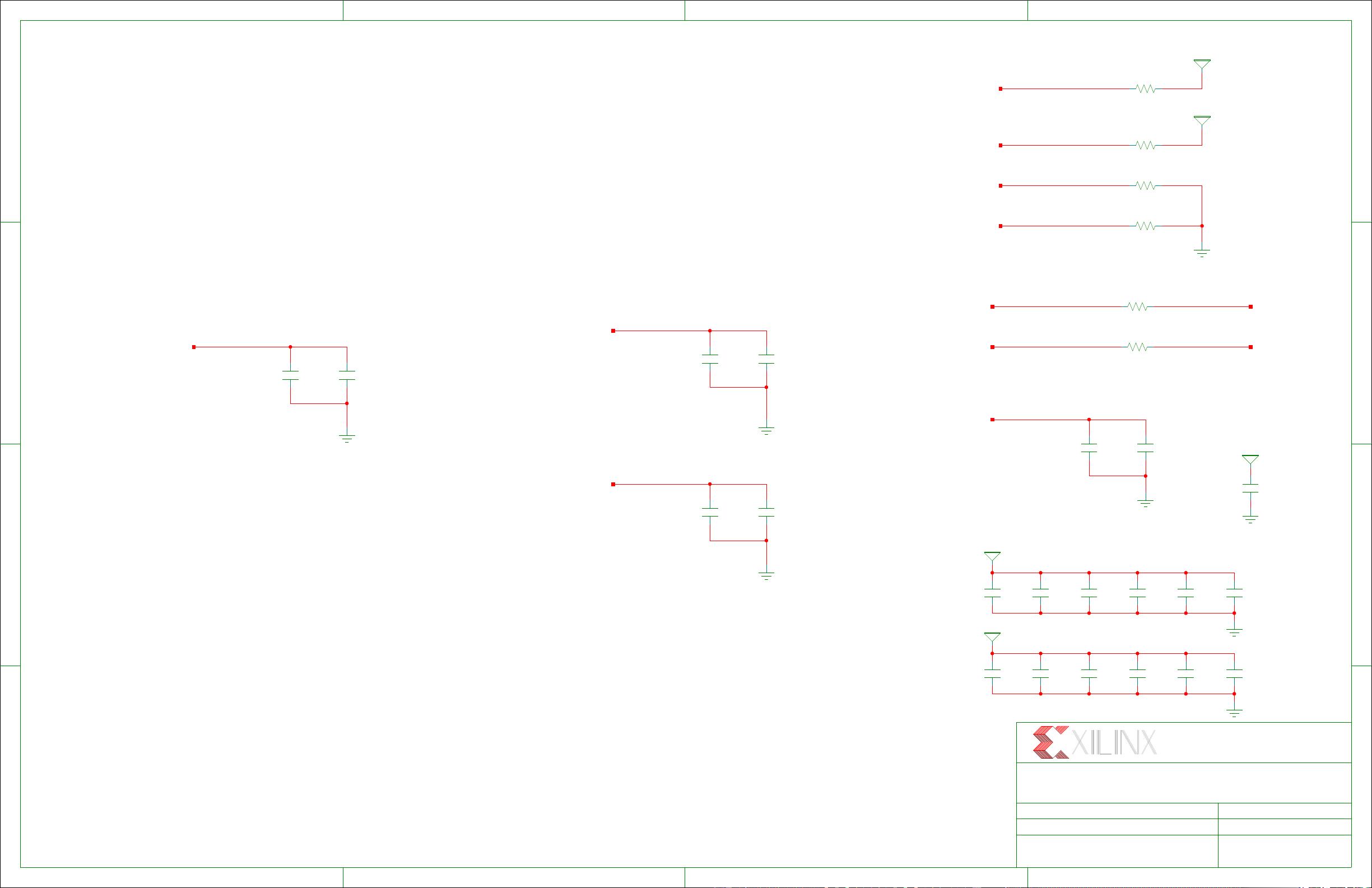

I2C ADDR2 = 0xA8

SIGNALS IS INTENDED TO ALLOW THE

NOTE: THE PINOUT OF THE DDR2 DQ AND DQS

USE OF LOCAL CLOCKING RESOURCES

AS DESCRIBED IN XAPP609.

E

03

DDR2 DECOUPLING

SS

72

8-22-2006_9:53

4

SCHEM, ROHS COMPLIANT, ML410 VIRTEX-4 EVAL PLAFTORM

0.01UF

C159

0.1UF

C158

VREF_DDR2

10,11,12,21,23

0.01UF

C156

0.1UF

C157

10,11,12,21,23

VREF_DDR2

0.01UF

C190

0.1UF

C179

10,11,12,21,23

VREF_DDR2

R23

0

0.01UF

C139

4.75K

R21

R22

0

R20

4.75K

4.75K

R19

C144

0.1UF0.1UF

C147

0.1UF

C143C148

0.1UF

C150

0.1UF0.1UF

C151

0.1UF

C146

0.1UF

C142C149

0.1UF

C140

0.1UF0.1UF

C145C141

0.1UF

4.75K

R16

0.1UF

C138

0.1UF

C152

21

DDR2_SA0

10,11,12,21,23

VREF_DDR2

DDR2_SDA

21

DDR2_SCL

21

6,35,45

IIC_SDA

6,35,45

IIC_SCL

DDR2_RST_N

21

DDR2_SA2

21

DDR2_SA1

21

MPZXX

VCC1V8

VCC2V5

VCC2V5

VCC1V8

VCC1V8VCC1V8

DEVICE=ICS97U877K

OS

OE

VDDQ9

FB_OUTT

FB_OUTC

FB_INC

FB_INT

VDDQ8

CLKT7

CLKC7

VDDQ7

CLKC6

CLKT6

CLKT5

CLKC5

VDDQ6

CLKC0

CLKT0

CLKT1

CLKC1

CLKC3

CLKC4

CLKT4

VDDQ5

CLKT9

CLKC9

CLKC8

CLKT8

VDDQ4

GND

VDDQ3

AVDD

AGND

VDDQ2

CLK_INC

CLK_INT

CLKT2

CLKC2

VDDQ

CLKT3

41

THERMPAD

SCH P/N

Sheet

Date:

Title:

Ver:

A

B

C

D

1234

D

C

B

A

4 3 2 1

Sheet Size: B Rev:

Drawn Byof

ART P/N

FAB P/N

0531499

1280372

0381203

NOTE: MODE BITS HAVE INTERNAL PULLUPS AND DEFAULT

TO SLAVE-SERIAL MODE. THERE MAY BE SOME

HOWEVER SLAVE-SERIAL MODE IS KNOWN TO WORK.

CONFLCITS BETWEEN THE JTAG MODES AND ICAP

All DDR2_CK* to be length matched

DDR2_PLL_FB* to be length matched to DDR2_CK*

E

03

SS

72

8-22-2006_9:53

5

FPGA CONFIG AND MISC I/O

SCHEM, ROHS COMPLIANT, ML410 VIRTEX-4 EVAL PLAFTORM

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

11

12

13

14

15

16

17

18

19

20

10

9

8

7

6

5

4

3

2

1

U26

AVDD_PLL

AVDD_PLL

1

2

0.1UF

C804

12

100

R480

DDR2_CK0_N

DDR2_CK0

12

100

R481

DDR2_CK1_N

DDR2_CK2_N

DDR2_CK1

DDR2_CK2

2

1

C808

0.01UF

2

1

C807

0.01UF

4.75K

R403

NOSTUFF

R395

4.75K

NOSTUFF

4.75K

R397

NOSTUFF

13

FPGA_MODE_2

FPGA_MODE_1

13

FPGA_MODE_0

13

FPGA_HSWAP

13

4.75K

R384

0

R449

FPGA_PWRDWN_B

13

4.75K

R452

FPGA_DONE

4.75K

R389

4.75K

R413

FPGA_CCLK

21

SW4

FPGA_PROG_B

2

1

C805

0.01UF

2

1

C806

0.01UF

2

1

C809

0.01UF

DDR2_PLL_CLKIN

DDR2_PLL_CLKIN_N

2

1

C803

10UF

DDR2_PLL_FB_N

DDR2_PLL_FB

2

1

C607

0.01UF

2

1

C606

0.01UF

2

1

C605

0.01UF

2

1

C604

0.01UF

1 2

FB1

12

1

R386

1

2

2200PF

C608

剩余71页未读,继续阅读

drjiachen

- 粉丝: 168

- 资源: 2144

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 2023年中国辣条食品行业创新及消费需求洞察报告.pptx

- 2023年半导体行业20强品牌.pptx

- 2023年全球电力行业评论.pptx

- 2023年全球网络安全现状-劳动力资源和网络运营的全球发展新态势.pptx

- 毕业设计-基于单片机的液体密度检测系统设计.doc

- 家用清扫机器人设计.doc

- 基于VB+数据库SQL的教师信息管理系统设计与实现 计算机专业设计范文模板参考资料.pdf

- 官塘驿林场林防火(资源监管)“空天地人”四位一体监测系统方案.doc

- 基于专利语义表征的技术预见方法及其应用.docx

- 浅谈电子商务的现状及发展趋势学习总结.doc

- 基于单片机的智能仓库温湿度控制系统 (2).pdf

- 基于SSM框架知识产权管理系统 (2).pdf

- 9年终工作总结新年计划PPT模板.pptx

- Hytera海能达CH04L01 说明书.pdf

- 数据中心运维操作标准及流程.pdf

- 报告模板 -成本分析与报告培训之三.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0