没有合适的资源?快使用搜索试试~ 我知道了~

首页Physical-Design-Complete.pdf

Physical-Design-Complete.pdf

需积分: 50 27 下载量 65 浏览量

更新于2023-03-16

评论 1

收藏 2.23MB PDF 举报

Contents 1. Inputs and outputs of Physical Design 2. Checks and care about before starting the Design 3. Floorplanning 4. Power planning 5. Placement 6. Clocktree synthesis - CTS 7. Clocktree Optimization - CTO 8. Routing 9. Design Rule check - DRC 10. LVS 11. Parasitic Extraction 12. Power Analysis 13. Crosstalk Analysis 14. Electron Migration 15. Timing Analysis 16. Chip Finishing (DFM or DFY) 17. Low-power Techniques 18. Designs Executed (Projects) 19. Multi-Voltage Design 20. Physical Design objective type questions and answers 21. ASIC Design check list 22. Companies interview questions

资源详情

资源评论

资源推荐

Physical Design Concepts

1

Contents

1. Inputs and outputs of Physical Design

2. Checks and care about before starting the Design

3. Floorplanning

4. Power planning

5. Placement

6. Clocktree synthesis - CTS

7. Clocktree Optimization - CTO

8. Routing

9. Design Rule check - DRC

10. LVS

11. Parasitic Extraction

12. Power Analysis

13. Crosstalk Analysis

14.

Electron Migration

15. Timing Analysis

16. Chip Finishing (DFM or DFY)

17. Low-power Techniques

18. Designs Executed (Projects)

19. Multi-Voltage Design

20. Physical Design objective type questions and answers

21. ASIC Design check list

22. Companies interview questions

Physical Design Concepts

2

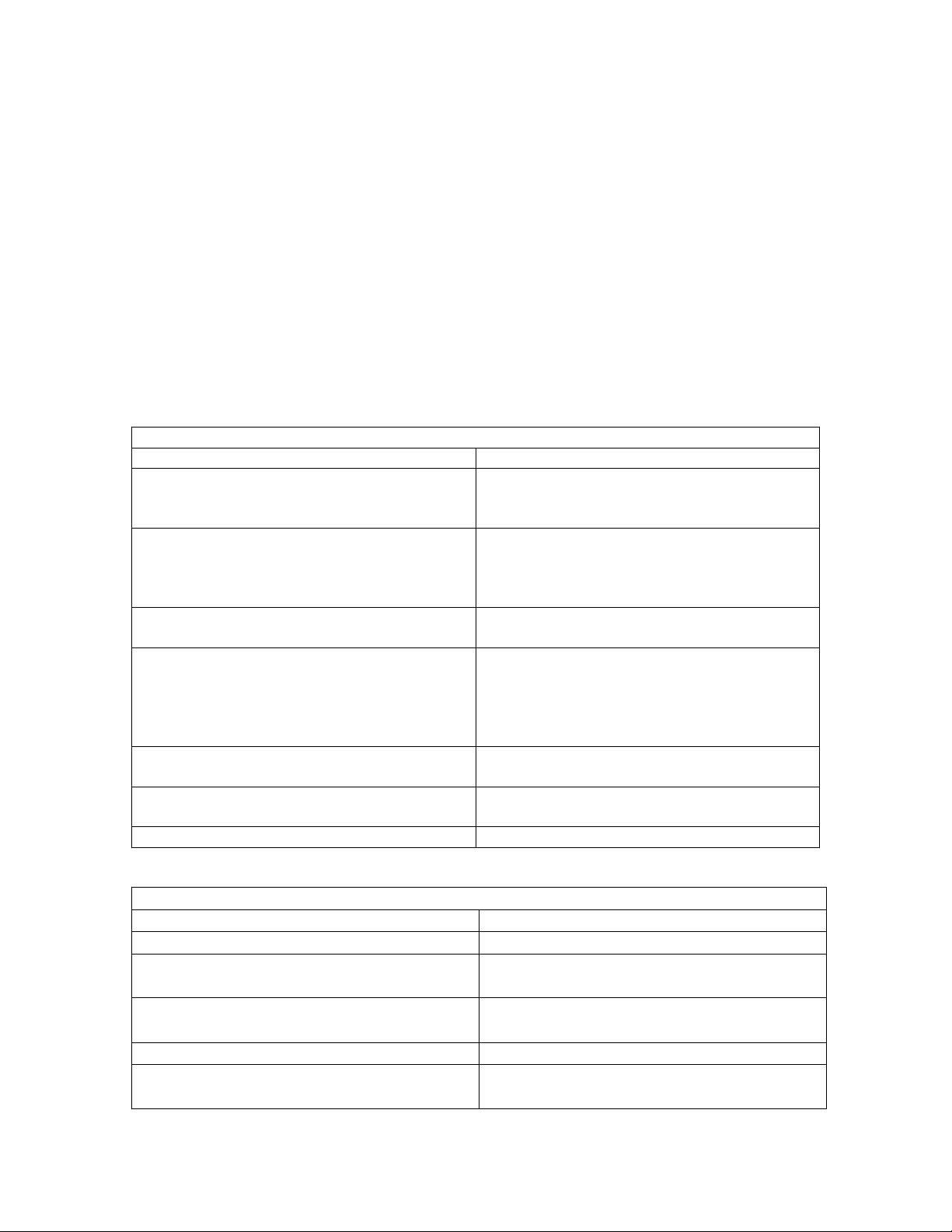

1. Inputs and outputs of physical design implementation

The inputs required for any physical design tool is summarized in Table (1) and the outputs

generated from the same are listed in Table (2).

Data Input Requirements for Physical Design Tool

Input data Required for Physical Design

File Format File Content

Technology file (.tf in synopsys format and

.techlef in cadence format)

It describes the units, drawing patterns, layers

design rules, vias, and parasitics resistance and

capacitance of the manufacturing process

Physical Libraries (In general Lef of GDS file

for all design elements like macro, std Cell, IO

pads etc., and in synopsys format .CEL,

.FRAM views for the above)

Contains complete layout information and

Abstract model for placement and routing like

pin accessibility, blockages etc.,

Timing, Logical and Power Libraries (.lib or

LM view -.db for all design elements)

Contains Timing and Power info

TDF file (.tdf or .io) Contains pad or pin arrangements like order

and location of the same. For full chip the

instantiation of VDD and VSS pads Power Cut

diode etc., (Whichever is not available in

verilog netlist)

Constraints (.sdc) Contain all design related constraints like Area,

power, timing

Physical Design Exchange Format –PDEF

(optional)

Contains, row, cell placement locations etc.,

Design Exchange Format –DEF (optional) Contains, row, cell placement locations etc.,

Output data from Physical Design Tool

File Format File Content

Standard delay format (.sdf) Timing Details (Except load info)

Parasitic format (.spef, .dspf) Resistance and Capacitance info of cells and

nets

Post routed Netlist (.v) Can be of flattened or

hierarchical

Contains connectivity info of all cells

Physical Layout (.gds) Physical Layout info

Design Excahnge format (.def) Contains, row, cell, net placement locations

etc.,

Physical Design Concepts

3

Libraries in Physical Design

Technology libraries are integral part of the ASIC backend EDA tools. Important two libraries are

briefly explained below.

Technology File Libraries

Technology file defines basic characteristic of cell library pertaining to a particular technology

node. They are units used in the design, graphical characteristics like colors, stipple patterns, line

styles, physical parameters of metal layers, coupling capacitances, capacitance models, dielectric

values, device characteristics, design rules. These specifications are divided into technology file

sections.

Units for power, voltage, current etc are defined in technology section.

The color section defines primary and display colors that a tool uses to display designs in the

library. Stipple pattern are defined in stipple sections. Different layer definitions like its current

density, width etc are defined in layer section. Fringe capacitances generated by crossing of

interconnects are defined in fringe cap section.

Similarly several other specifications like metal density, design rules that apply to design in

library, place and route (P&R) rules, slot rule, resistance model are defined in their respective

sections.

Standard Cell Libraries, I/O Cell Libraries, Special Cell Libraries

A standard cell library is a collection of pre designed layout of basic logic gates like inverters,

buffers, ANDs, ORs, NANDs etc.

All the cells in the library have same standard height and have varied width. These standard cell

libraries are known as reference libraries in Astro.

These reference libraries are technology specific and are generally provided by ASIC vendor like

TSMC, Artisan, IBM etc. Standard cell height for 130 TSMC process is 3.65 µM.

In addition to standard cell libraries, reference libraries contain I/O and Power/Ground pad cell

libraries. It also contain IP libraries for reusable IP like RAMs, ROMs and other pre-designed,

standard, complex blocks.

The TSMC universal I/O libraries include several power/ground cells that supply different

voltages to the core, pre-drivers and post drivers. Internal pull-up or pull-down is provided to

some cells in I/O libraries.

Physical Design Concepts

4

2. Checks and Care About Before Starting the Design

The goal of the HandOff environment is to provide early checking capabilities to ensure that once

the design is routed and has converged in timing on the optimization environments, the SignOff

of the design will produce no surprises. Among surprises that are safeguarded by the HandOff

environment are:

- Naming issues among the different SignOff environments tools: extraction, DRC, LVS.

- LVS issues with respect to power/ground proper definition.- Bad clock implementation

planning.

In case latency are not budgeted properly, it is common to ends-up re implementing the design

from scratch with updated latency/clock definitions.If lucky, it’s only a matter of redoing CTS

and all the routing phase.

In the worst condition, the design is hacked with ECOs on the clock trees to fix timing using large

skews with potential silicon failure.

- Bad optimization through constraints checking. Same consequence as above if not done

properly.

- Bad interpretation of High Fanout nets requirements.

Note:

Failure to budget high fan-out nets(HFN) and clocks can cause full placement re-spin

because of incorrect pre-cts optimization.

In this flow the following information are obtained by the users and validated:

•Inter clock relation ship of the clocks must be aligned together

•Basic checking of constraints in the Zero WLM

• defines all clock roots

• defines all high fanout nets

• budgets all clock latencies and insertion delays of high fanout nets(HFN). The min insertion

delay must be equal to the max insertion delay (known problem).

• if a scan chain description is available, user validate that the budgeted latencies does not cause

too large skews on the scan chains

• user validate that all “create_clocks” have an equivalent clock root in , user validate that all high

fanout nets are defined

• user export pre-cts clock latencies.

•In Unix, user updates the uncertainty definitions of pre/post cts files.

•It is recommended

Note:

Physical Design Concepts

5

Failure to budget high-fanout nets and clocks can cause full placement re-spin because of

incorrect pre-cts optimization.

Multi Voltage design

Definition: A multi voltage design is a hierarchical design with some blocks being supplied with

a different voltage than the top level. The flow today only support a single voltage per place and

route partitions, but by combining the partitions together, to have indeed multiple configuration.

Check:

As buffers are connected to the periphery of the circuit, it is a good design practice to put them at

the top level.

A net with more than one driver is reported.

A driver is an input top port or an output pin.

A top level port of a block cannot be left unconnected

A top level port of a top design pad cell cannot be left unconnected.

A pass output of a cell having a input pad must be connected only with cells of celltype interface.

Every unbuffered package (with a pass output) pad input must be buffered (of celltype interface).

ClockTree Check:

Vth Consistency:

The clock tree must use cells from the allowed Vth list. Today, that list of Vth correspond to all

Vths available and there is no limitation set.

The clock tree must be using the same Vth or oxide thickness. The check report only the first

instance with a different Vth. This is to ensure different branches of the clock are seeing the same

variation with respect to average power supply, temperature, process.

Max Drive:

It is not allowed to have cells which have a too large drive. There is 2 reasons for this. First

reason is to limit electromigration risks. Second reason is to limit the configuration with large

miller capacitances.

It is not allowed to have cells that are too weak. This is to limit the amount of variations.

It is not allowed to have delay cells in the clock tree. Delay cells have very particular layout and

there is a risk of large pulses being filtered by the delay cell.

It is not allowed to have a too long string of cells with a fanout of 1. If this is the case, it is

possible that the CTS engine compensated wire delays with cells delays. In such case, you can

activate cross corner signoff to ensure signoff is still valid and ignore the error.

difference in cell depth between two branches of the clocktree

It is not allowed to have a very long clock tree branch and a very short one in the same clock

tree, or between different clock roots. This error is reported for branch belonging to the same

clock root. If this is the case, the skew computed during delay calculation or timing analysis is not

剩余302页未读,继续阅读

drjiachen

- 粉丝: 168

- 资源: 2144

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 数据结构1800题含完整答案详解.doc

- 医疗企业薪酬系统设计与管理方案.pptx

- 界面与表面技术界面理论与表面技术要点PPT学习教案.pptx

- Java集合排序及java集合类详解(Collection、List、Map、Set)讲解.pdf

- 网页浏览器的开发 (2).pdf

- 路由器原理与设计讲稿6-交换网络.pptx

- 火电厂锅炉过热汽温控制系统设计.doc

- 企业识别CIS系统手册[收集].pdf

- 物业管理基础知识.pptx

- 第4章财务预测.pptx

- 《集成电路工艺设计及器件特性分析》——实验教学计算机仿真系.pptx

- 局域网内共享文件提示没有访问权限的问题借鉴.pdf

- 第5章网络营销策略.pptx

- 固井质量测井原理PPT教案.pptx

- 毕业实习总结6篇.doc

- UGNX建模基础篇草图模块PPT学习教案.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0