没有合适的资源?快使用搜索试试~ 我知道了~

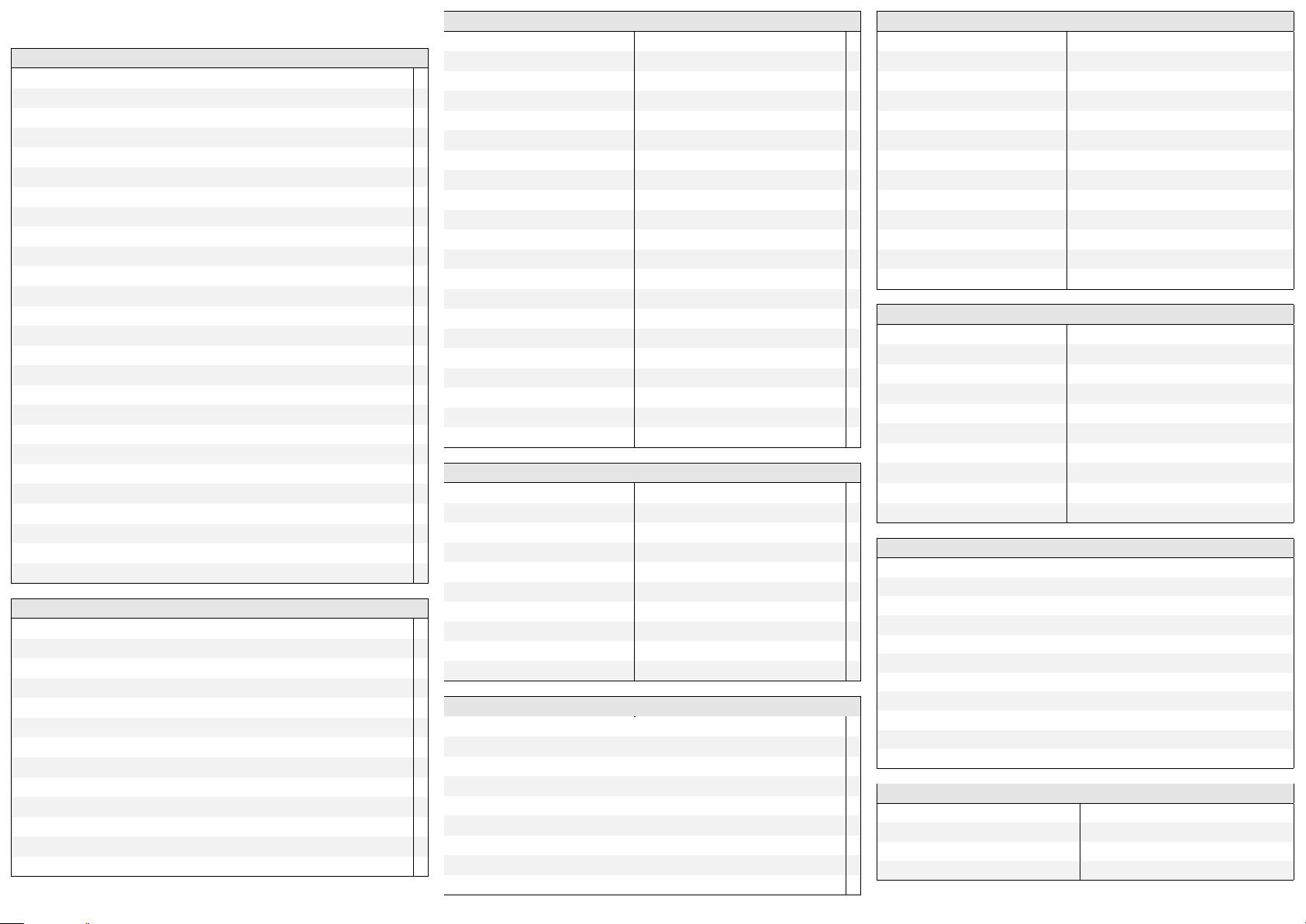

首页ARMv8 arm64 指令集速览表(打印版)

ARMv8 arm64 指令集速览表(打印版)

ARMv8 arm64 指令集速览表(打印版)。包含了全部汇编指令,两页pdf,适合速查,可以打印在A4纸上方便编程。

资源详情

资源评论

资源推荐

ARM64 version 2 page 1

ARMv8 A64 Quick Reference

Arithmetic Instructions

ADC{S} rd, rn, rm

rd = rn + rm + C

ADD{S} rd, rn, op2

rd = rn + op2

S

ADR Xd, ±rel

21

Xd = PC + rel

±

ADRP Xd, ±rel

33

Xd = PC

63:12

:0

12

+ rel

±

33:12

:0

12

CMN rd, op2

rd + op2

S

CMP rd, op2

rd − op2

S

MADD rd, rn, rm, ra

rd = ra + rn × rm

MNEG rd, rn, rm

rd = − rn × rm

MSUB rd, rn, rm, ra

rd = ra − rn × rm

MUL rd, rn, rm

rd = rn × rm

NEG{S} rd, op2

rd = −op2

NGC{S} rd, rm

rd = −rm − ∼C

SBC{S} rd, rn, rm

rd = rn − rm − ∼C

SDIV rd, rn, rm

rd = rn

¯

÷ rm

SMADDL Xd, Wn, Wm, Xa

Xd = Xa + Wn

¯

× Wm

SMNEGL Xd, Wn, Wm

Xd = − Wn

¯

× Wm

SMSUBL Xd, Wn, Wm, Xa

Xd = Xa − Wn

¯

× Wm

SMULH Xd, Xn, Xm

Xd = (Xn

¯

× Xm)

127:64

SMULL Xd, Wn, Wm

Xd = Wn

¯

× Wm

SUB{S} rd, rn, op2

rd = rn - op2

S

UDIV rd, rn, rm

rd = rn ÷ rm

UMADDL Xd, Wn, Wm, Xa

Xd = Xa + Wn × Wm

UMNEGL Xd, Wn, Wm

Xd = − Wn × Wm

UMSUBL Xd, Wn, Wm, Xa

Xd = Xa − Wn × Wm

UMULH Xd, Xn, Xm

Xd = (Xn × Xm)

127:64

UMULL Xd, Wn, Wm

Xd = Wn × Wm

Bit Manipulation Instructions

BFI rd, rn, #p, #n

rd

p+n−1:p

= rn

n−1:0

BFXIL rd, rn, #p, #n

rd

n−1:0

= rn

p+n−1:p

CLS rd, rn

rd = CountLeadingOnes(rn)

CLZ rd, rn

rd = CountLeadingZeros(rn)

EXTR rd, rn, rm, #p

rd = rn

p−1:0

:rm

N0

RBIT rd, rn

rd = ReverseBits(rn)

REV rd, rn

rd = BSwap(rn)

REV16 rd, rn

for(n=0..1|3) rd

Hn

=BSwap(rn

Hn

)

REV32 Xd, Xn

Xd=BSwap(Xn

63:32

):BSwap(Xn

31:0

)

{S,U}BFIZ rd, rn, #p, #n

rd = rn

?

n−1:0

p

{S,U}BFX rd, rn, #p, #n

rd = rn

?

p+n−1:p

{S,U}XT{B,H} rd, Wn

rd = Wn

?

N0

SXTW Xd, Wn

Xd = Wn

±

Logical and Move Instructions

AND{S} rd, rn, op2

rd = rn & op2

ASR rd, rn, rm

rd = rn

¯

rm

ASR rd, rn, #i

6

rd = rn

¯

i

BIC{S} rd, rn, op2

rd = rn & ∼op2

EON rd, rn, op2

rd = rn ⊕ ∼op2

EOR rd, rn, op2

rd = rn ⊕ op2

LSL rd, rn, rm

rd = rn rm

LSL rd, rn, #i

6

rd = rn i

LSR rd, rn, rm

rd = rn rm

LSR rd, rn, #i

6

rd = rn i

MOV rd, rn

rd = rn

S

MOV rd, #i

rd = i

MOVK rd,#i

16

{, sh}

rd

sh+15:sh

= i

MOVN rd,#i

16

{, sh}

rd = ∼(i

∅

sh)

MOVZ rd,#i

16

{, sh}

rd = i

∅

sh

MVN rd, op2

rd = ∼op2

ORN rd, rn, op2

rd = rn | ∼op2

ORR rd, rn, op2

rd = rn | op2

ROR rd, rn, #i

6

rd = rn ≫ i

ROR rd, rn, rm

rd = rn ≫ rm

TST rn, op2

rn & op2

Branch Instructions

B rel

28

PC = PC + rel

±

27:2

:0

2

Bcc rel

21

if(cc) PC = PC + rel

±

20:2

:0

2

BL rel

28

X30 = PC + 4; PC += rel

±

27:2

:0

2

BLR Xn

X30 = PC + 4; PC = Xn

BR Xn

PC = Xn

CBNZ rn, rel

21

if(rn 6= 0) PC += rel

∅

21:2

:0

2

CBZ rn, rel

21

if(rn = 0) PC += rel

∅

21:2

:0

2

RET {Xn}

PC = Xn

TBNZ rn, #i, rel

16

if(rn

i

6= 0) PC += rel

±

15:2

:0

2

TBZ rn, #i, rel

16

if(rn

i

= 0) PC += rel

±

15:2

:0

2

Atomic Instructions

CAS{A}{L} rs, rt, [Xn]

if (rs = [Xn]

N

) [Xn]

N

= rt

1

CAS{A}{L}{B,H} Ws, Wt, [Xn] if (Ws

N0

= [Xn]

N

) [Xn]

N

= Wt

N0

1

CAS{A}{L}P rs,rs2,rt,rt2,[Xn]

if (rs2:rs = [Xn]

2N

) [Xn]

2N

= rt2:rt

1

LDao{A}{L}{B,H} Ws, Wt, [Xn] Wt=[Xn]

∅

N

; [Xn]

N

=ao([Xn]

N

,Ws

N0

)

1

LDao{A}{L} rs, rt, [Xn]

rt = [Xn]

N

; [Xn]

N

= ao([Xn]

N

, rs)

1

STao{A}{L}{B,H} Ws, [Xn] [Xn]

N

= ao([Xn]

N

, Ws

N0

)

1

STao{A}{L} rs, [Xn]

[Xn]

N

= ao([Xn]

N

, rs)

1

SWP{A}{L}{B,H} Ws, Wt, [Xn] Wt = [Xn]

∅

N

; [Xn]

N

= Ws

N0

1

SWP{A}{L} rs, rt, [Xn]

rt = [Xn]

N

; [Xn]

N

= rs

1

Conditional Instructions

CCMN rn, #i

5

, #f

4

, cc

if(cc) rn + i; else N:Z:C:V = f

CCMN rn, rm, #f

4

, cc

if(cc) rn + rm; else N:Z:C:V = f

CCMP rn, #i

5

, #f

4

, cc

if(cc) rn − i; else N:Z:C:V = f

CCMP rn, rm, #f

4

, cc

if(cc) rn − rm; else N:Z:C:V = f

CINC rd, rn, cc

if(cc) rd = rn + 1; else rd = rn

CINV rd, rn, cc

if(cc) rd = ∼rn; else rd = rn

CNEG rd, rn, cc

if(cc) rd = −rn; else rd = rn

CSEL rd, rn, rm, cc

if(cc) rd = rn; else rd = rm

CSET rd, cc

if(cc) rd = 1; else rd = 0

CSETM rd, cc

if(cc) rd = ∼0; else rd = 0

CSINC rd, rn, rm, cc

if(cc) rd = rn; else rd = rm + 1

CSINV rd, rn, rm, cc

if(cc) rd = rn; else rd = ∼rm

CSNEG rd, rn, rm, cc

if(cc) rd = rn; else rd = −rm

Load and Store Instructions

LDP rt, rt2, [addr]

rt2:rt = [addr]

2N

LDPSW Xt, Xt2, [addr]

Xt = [addr]

±

32

; Xt2 = [addr+4]

±

32

LD{U}R rt, [addr]

rt = [addr]

N

LD{U}R{B,H} Wt, [addr]

Wt = [addr]

∅

N

LD{U}RS{B,H} rt, [addr] rt = [addr]

±

N

LD{U}RSW Xt, [addr]

Xt = [addr]

±

32

PRFM prfop, addr

Prefetch(addr, prfop)

STP rt, rt2, [addr]

[addr]

2N

= rt2:rt

ST{U}R rt, [addr]

[addr]

N

= rt

ST{U}R{B,H} Wt, [addr]

[addr]

N

= Wt

N0

Addressing Modes (addr)

xxP,LDPSW [Xn{, #i

7+s

}] addr = Xn + i

±

6+s:s

:0

s

xxP,LDPSW [Xn], #i

7+s

addr=Xn; Xn+=i

±

6+s:s

:0

s

xxP,LDPSW [Xn, #i

7+s

]! Xn+=i

±

6+s:s

:0

s

; addr=Xn

xxR*,PRFM [Xn{, #i

12+s

}] addr = Xn + i

∅

11+s:s

:0

s

xxR* [Xn], #i

9

addr = Xn; Xn += i

±

xxR* [Xn, #i

9

]! Xn += i

±

; addr = Xn

xxR*,PRFM [Xn,Xm{, LSL #0|s}] addr = Xn + Xm s

xxR*,PRFM [Xn,Wm,{S,U}XTW{ #0|s}] addr = Xn + Wm

?

s

xxR*,PRFM [Xn,Xm,SXTX{ #0|s}] addr = Xn + Xm

±

s

xxUR*,PRFM [Xn{, #i

9

}] addr = Xn += i

±

LDR{SW},PRFM ±rel

21

addr = PC + rel

±

20:2

:0

2

Atomic Operations (ao)

ADD [Xn] + rs SMAX [Xn]

¯

> rs ? [Xn] : rs

CLR [Xn] & ∼rs SMIN [Xn]

¯

< rs ? [Xn] : rs

EOR [Xn] ⊕ rs UMAX [Xn] > rs ? [Xn] : rs

SET [Xn] | rs UMIN [Xn] < rs ? [Xn] : rs

1

srrwlkblu

- 粉丝: 3

- 资源: 7

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 27页智慧街道信息化建设综合解决方案.pptx

- 计算机二级Ms-Office选择题汇总.doc

- 单链表的插入和删除实验报告 (2).docx

- 单链表的插入和删除实验报告.pdf

- 物联网智能终端项目设备管理方案.pdf

- 如何打造品牌的模式.doc

- 样式控制与页面布局.pdf

- 武汉理工Java实验报告(二).docx

- 2021线上新品消费趋势报告.pdf

- 第3章 Matlab中的矩阵及其运算.docx

- 基于Web的人力资源管理系统的必要性和可行性.doc

- 基于一阶倒立摆的matlab仿真实验.doc

- 速运公司物流管理模式研究教材

- 大数据与管理.pptx

- 单片机课程设计之步进电机.doc

- 大数据与数据挖掘.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论3