没有合适的资源?快使用搜索试试~ 我知道了~

首页verilog和vhdl Testbench编程指南

verilog和vhdl Testbench编程指南

需积分: 33 26 下载量 84 浏览量

更新于2023-03-16

评论 4

收藏 965KB PDF 举报

verilog和vhdl Testbench编程指南,详细讲解了VHDL和Verilog的Testbench的编写,测试信号的编写等

资源详情

资源评论

资源推荐

Testbench 编程指南 Jason.chen@weikeng.com.cn

1

TestBench 编程指南

如今数字设计的规模变得越来越庞大,设计的复杂程度也越来越

高,这就使得设计的验证变得越来越困难,而且费时费力。为了应对这

种挑战,验证工程师依靠各种验证工具和方法。对于大型设计,如几

百万门的设计,通常采用一整套正式的验证工具。然而,对于小一些

的设计,设计工程师发现往往采用带 TestBench 的 HDL 仿真工具是最

好的途径。

TestBench 已经变成验证高级语言设计的一种标准的方法。通常,

TestBench 执行以下任务:

z 例化设计,使其可测试(DUT-design under test);

z 通过将测试向量应用到模型来仿真例化后的可测试的设计;

z 将结果输出到终端,或者输出波形窗口;

z 将真实的结果和期望的结果进行比较;

一般,TestBench 采用工业标准的 VHDL 或者 Verilog 硬件描述语

言来编写。TestBench 调用功能设计,然后仿真。复杂的测试文件执

行附加功能――例如,他们包含逻辑以决定合适的设计激励或者比较

真实的结果和期望的结果。

以下章节将讨论一个组织良好的测试文件的组成,以及例举了一

个带有自检的测试文件(自动将真实的结果和预期的结果进行比较)。

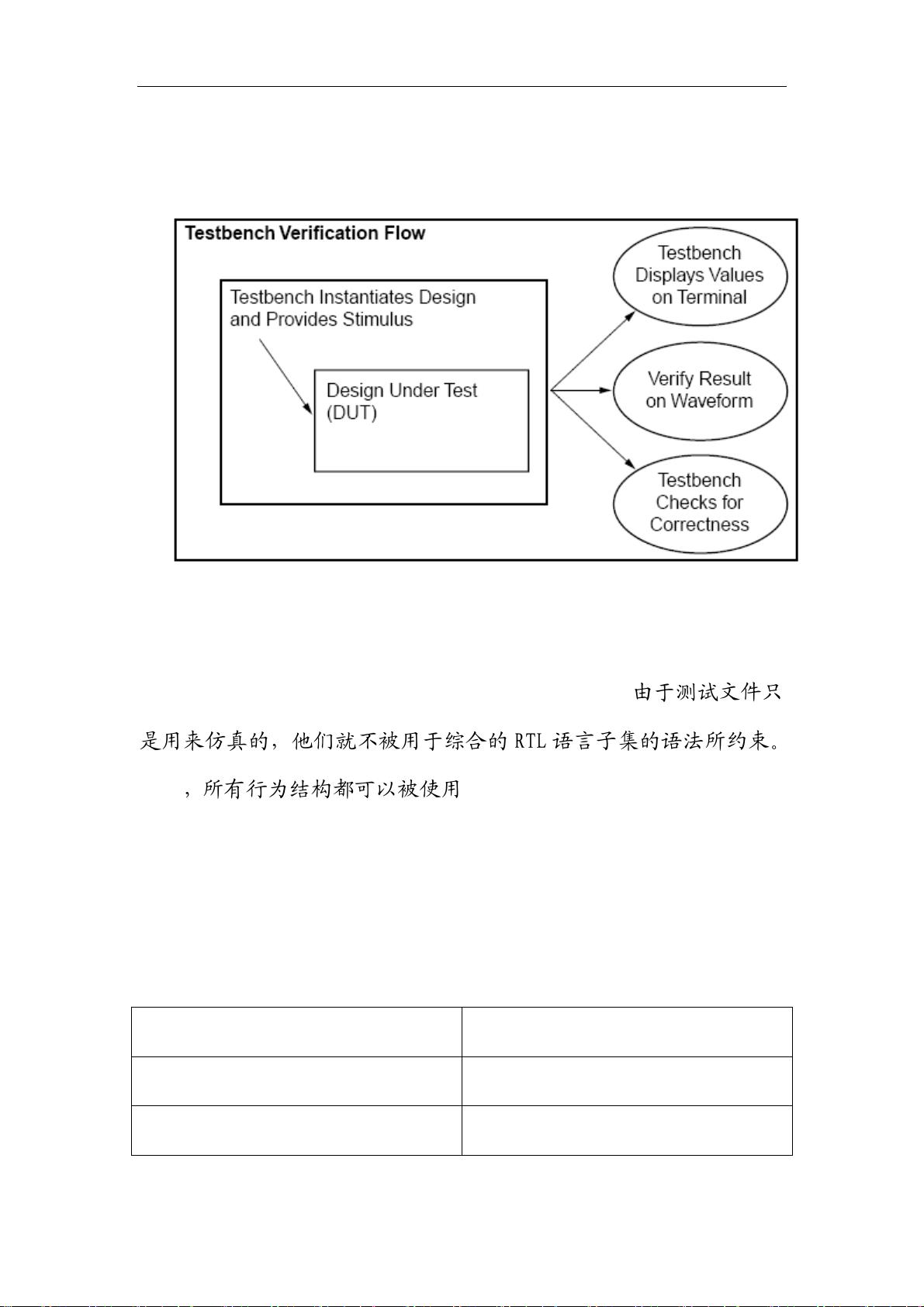

下图是一个标准的 HDL 验证的流程。自从测试文件可以用 VHDL 或者

Verilog 编写以来,测试验证流程就可以在平台和供应商的工具交叉

Testbench 编程指南 Jason.chen@weikeng.com.cn

2

进行。同时,由于 VHDL 和 Verilog 都是标准的公用的语言,所以用

VHDL 或者是 Verilog 描述的验证可以很简单的被再使用。

图 1. HDL 验证流程

测试文件构成:

测试文件可以采用 VHDL 或者 Verilog 语言编写。由于测试文件只

是用来仿真的,他们就不被用于综合的 RTL 语言子集的语法所约束。

相反,所有行为结构都可以被使用。这样,测试文件可以被写的更通

用,更易于维护。

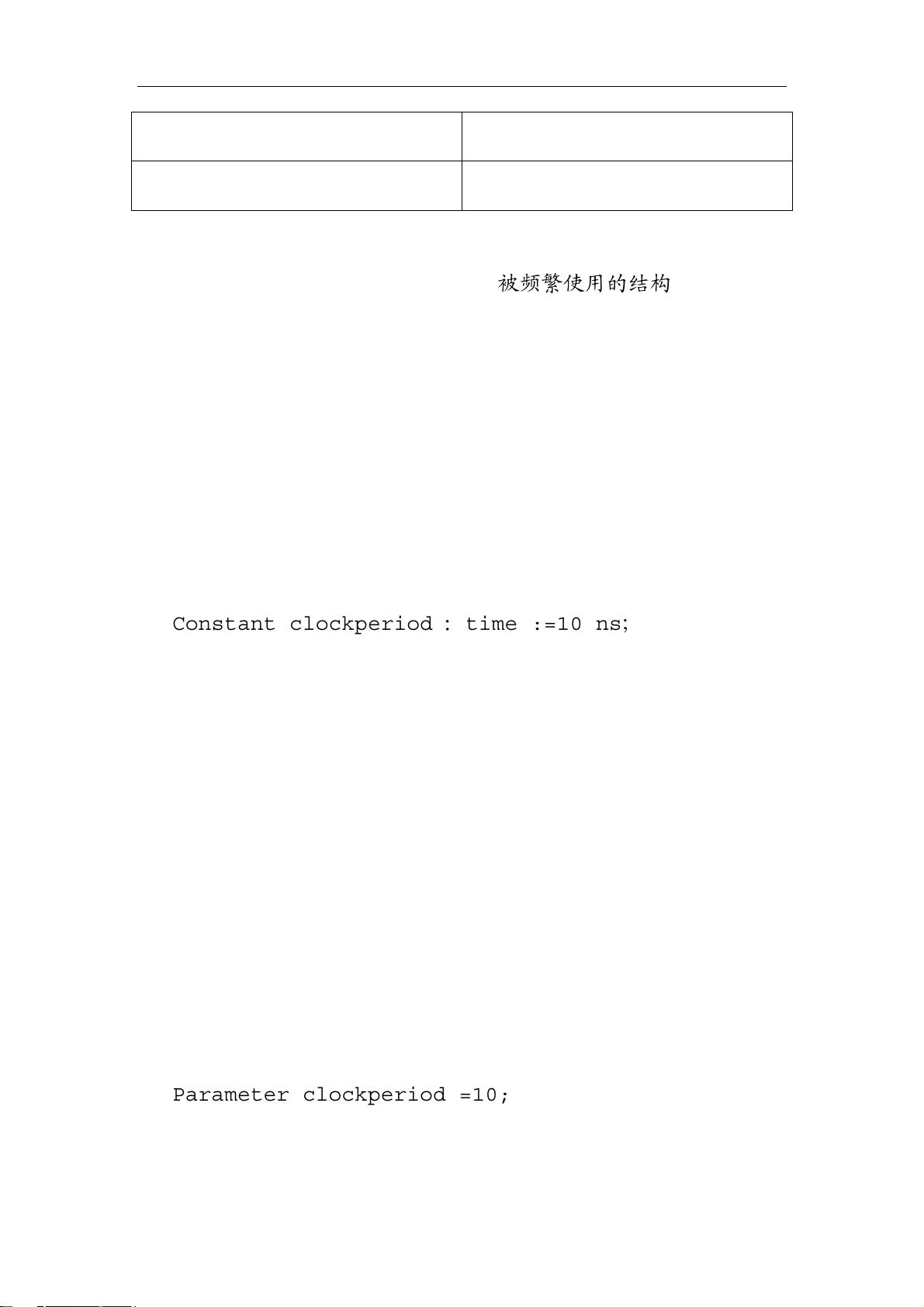

所有的测试文件都包含以下基本内容,如表 1。如上所属,测试

文件经常同时包含附加功能,如结果的可视化显示和内建错误检测。

表1

VHDL Verilog

实体和结构体申明 模块申明

信号申明 信号申明

Testbench 编程指南 Jason.chen@weikeng.com.cn

3

顶层设计实例化 顶层设计实例化

提供激励 提供激励

以下例子展示了一些在测试文件中被频繁使用的结构。

时钟信号发生:

采用系统时钟时序化逻辑的设计需要产生一个时钟。重复时钟在

VHDL 或者 Verilog 源码中可以很简单的发生。以下就是在 VHDL 和

Verilog 中的时钟发生例子:

VHDL:

--申明时钟周期常量

Constant clockperiod :time :=10 ns;

--时钟发生方法之一:

Clock<=not clock after clockperiod/2;

--时钟发生方法之二:

Generate clock : process

Begin

Wait for (clockperiod/2);

Clock<=’1’;

Wait for (clockperiod/2);

Clock<=’0’;

End process;

Verilog:

//时钟周期定义

Parameter clockperiod =10;

//方法 1

Initial begin

Testbench 编程指南 Jason.chen@weikeng.com.cn

4

Forever clock=#(clockperiod/2) ~clock;

End

//方法 2

Initial begin

Always #(clockperiod/2) clock=~clock;

End

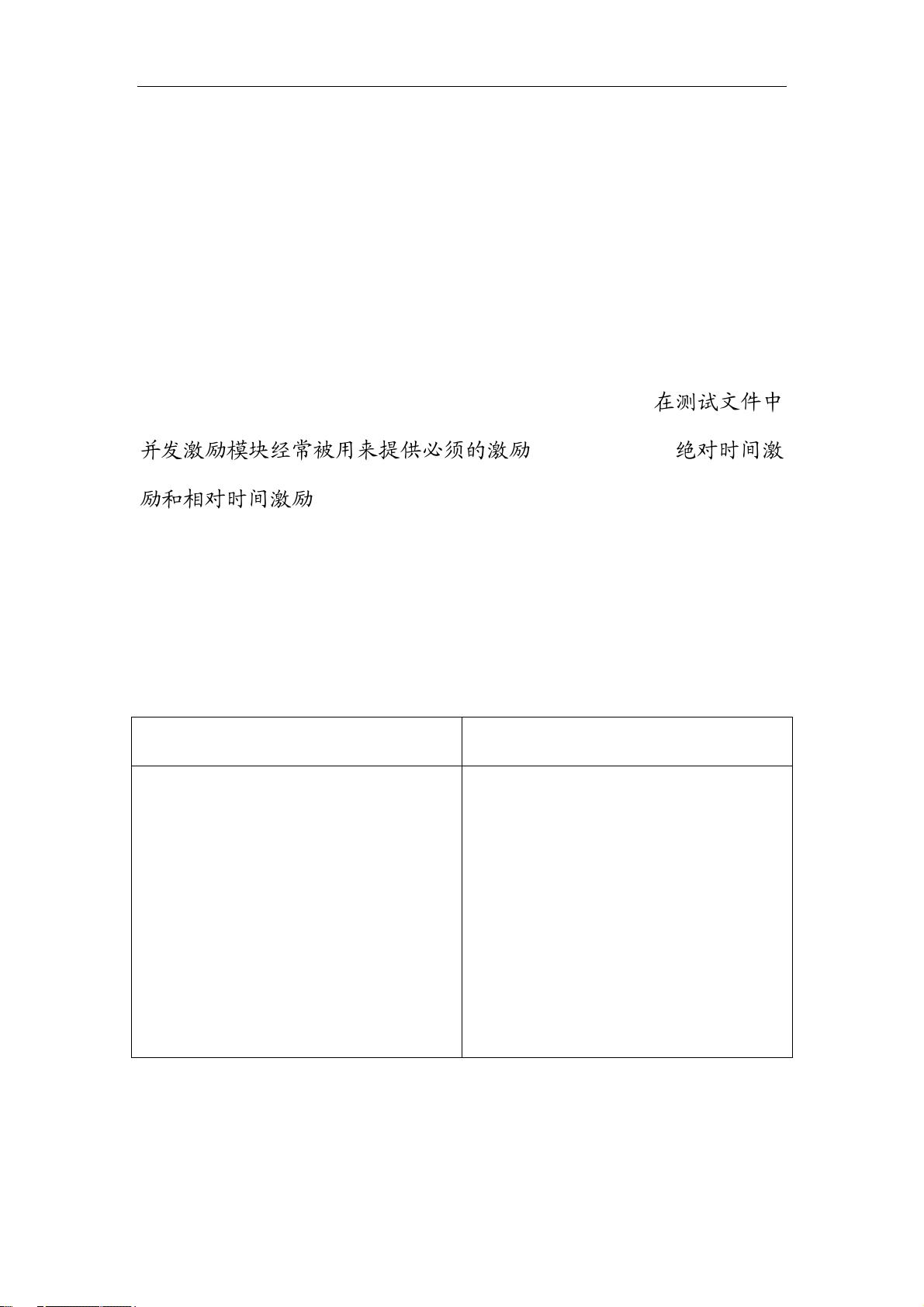

激励产生:

要得到测试验证结果,必须给 DUT 提供激励信号。在测试文件中

并发激励模块经常被用来提供必须的激励。有两种方式:绝对时间激

励和相对时间激励。在第一种方式中仿真值的描述是相对于仿真时间

为零的。相比,相对时间激励提供初始值,然后等待再次触发激励前

的事件的发生。两种方法根据设计者的需求可以在同一个测试文件中

使用。表 2,表 3 是上述两种方法的 VHDL 以及 Verilog 的例子。

表 2 :绝对时间激励

VHDL-绝对时间激励方式 Verilog-绝对时间激励方式

Mainstimulus : process

Begin

Reset<=’1’;

Load<=’0’;

Count_updn<=’0’;

Wait for 100 ns;

Reset<=’0’;

Wait for 20 ns;

Load<=’1’;

Wait for 20 ns;

Count_updn<=’1’;

End process;

Initial begin

Reset=1;

Load=0;

Count_updn=0;

#100 reset=0;

#20 load=1;

#20 count_updn=1;

end

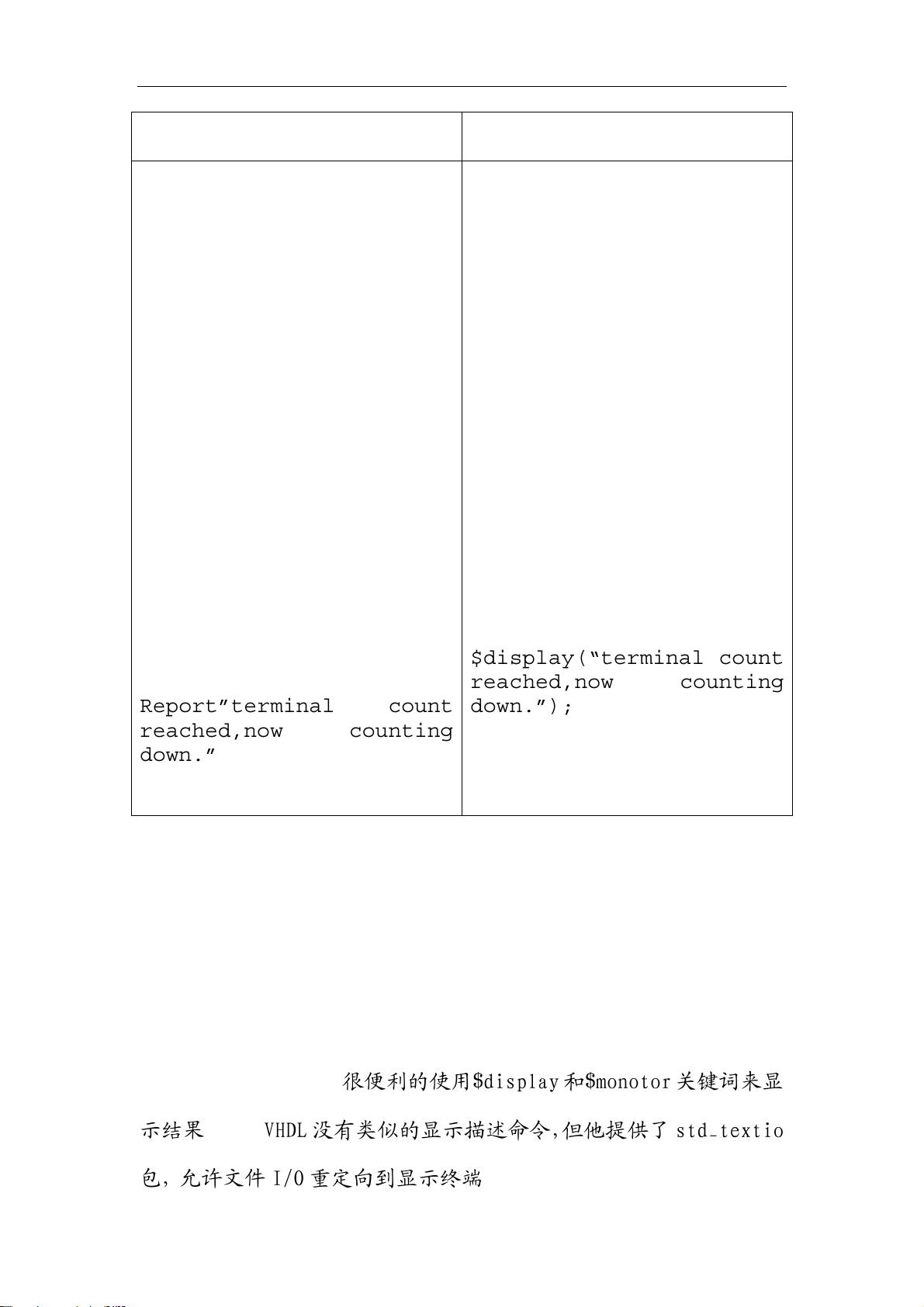

表 3 :相对时间激励

Testbench 编程指南 Jason.chen@weikeng.com.cn

5

VHDL Verilog

First : Process(clock)

Begin

If risin

g

ed

g

e(clock)

then

Tb_count<=tb_count+1;

End if;

End process;

Second : Process

Begin

If tb_count<=5 then

Reset<=’1’;

Load<=’0’;

Count_updn<=’0’;

Else

Reset<=’0’;

Load<=’1’;

Count_updn<=’1’;

End process;

Final :Process

Begin

If count=”1100” then

Count_updn<=’0’;

Re

p

ort”terminal count

reached,now countin

g

down.”

End if;

End process;

always@(posedge clock)

tb_count<=tb_count+1;

initial begin

if(tb_count<=5)

begin

reset=1;

load<=0;

count_updn=0;

end

else

begin

reset=0;

load=1;

count_updn=1;

end

end

initial begin

if(count==1100) begin

count_updn<=0;

$dis

p

la

y

(“terminal count

reached,now countin

g

down.”);

End

End

VHDL 进程以及 Verilog 初始化模块与测试文件中的其他进程或者

初始化模块是同时被执行的。然而,在每个(进程或者初始的)模块

中,事件都是按照书写顺序依次执行的。将一个复杂的激励序列用多

个模块来简化,以增加易读性和易维护性。

结果显示:

在 Verilog 中可以很便利的使用$display 和$monotor 关键词来显

示结果。虽然 VHDL 没有类似的显示描述命令,但他提供了 std_textio

包,允许文件 I/O 重定向到显示终端(这一技术的使用例子详见下面

剩余38页未读,继续阅读

Captain_船长

- 粉丝: 10

- 资源: 20

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- stc12c5a60s2 例程

- Android通过全局变量传递数据

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0