没有合适的资源?快使用搜索试试~ 我知道了~

首页H9TQ64A8GTCCUR数据手册

H9TQ64A8GTCCUR数据手册

需积分: 50 29 下载量 110 浏览量

更新于2023-03-16

评论 2

收藏 4.1MB PDF 举报

LG的MCP:H9TQ64A8GTCCUR 8GB eMMC (x8) / LPDDR3 8Gb(x32)

资源详情

资源评论

资源推荐

This document is a general product description and is subject to change without notice. SK hynix does not assume any responsibility

for use of circuits described. No patent licenses are implied.

Rev 0.1 / Jul. 2016 1

eMCP Specification

8GB eMMC (x8)

+ 8Gb LPDDR3 (x32)

Rev 0.1 / Jul. 2016 2

Preliminary

H9TQ64A8GTCCUR

8GB eMMC (x8) / LPDDR3 8Gb(x32)

Document Title

eMCP

8GB eMMC(x8) Flash / 8Gb (x32) LPDDR3

Revision History

Revision No. History Draft Date Remark

0.1 - Initial version Jul. 2016 Preliminary

Rev 0.1 / Jul. 2016 3

Preliminary

H9TQ64A8GTCCUR

8GB eMMC (x8) / LPDDR3 8Gb(x32)

FEATURES

[ eMCP ]

● Operation Temperature

- (-25)

o

C ~ 85

o

C

● Package

- 221-ball FBGA

- 11.5x13.0mm

2

, 1.0t, 0.5mm pitch

- Lead & Halogen Free

[ eMMC ]

• eMMC5.1 compatible

(Backward compatible to eMMC4.5&eMMC5.0)

• Bus mode

- Data bus width : 1 bit(default), 4 bits, 8 bits

- Data transfer rate: up to 400MB/s (HS400)

- MMC I/F Clock frequency : 0~200MHz

- MMC I/F Boot frequency : 0~52MHz

• Operating voltage range

-

V

cc

(NAND) : 2.7 - 3.6V

-

V

ccq

(Controller) : 1.7 - 1.95V / 2.7 - 3.6V

• Temperature

- Operation (-25

℃ ~ +85℃)

- Storage without operation (-40

℃ ~ +85℃)

• Others

- This product is compliance with the RoHS

directive

• Supported features

- HS400, HS200

- HPI, BKOPS, BKOP operation control

- Packed CMD, CMD queuing

- Cache, Cache barrier, Cache flushing

report

- Partitioning, RPMB, RPMB throughput improve

- Discard, Trim, Erase, Sanitize

- Write protect, Secure write protection

- Lock/Unlock

- PON, Sleep/Awake

- Reliable Write

- Boot feature, Boot partition

- HW/SW Reset

- Field Firmware Update

- Configurable driver strength

- Health(Smart) report

- Production state awareness

- Secure removal type

- Data Strobe pin, Enhanced data strobe

(Bold features are added in eMMC5.1)

[ LPDDR3 ]

• VDD1 = 1.8V (1.7V to 1.95V)

• VDD2 and VDDQ = 1.2V (1.14V to 1.30)

• HSUL_12 interface (High Speed Unterminated Logic 1.2V)

• Double data rate architecture for command, address and

data Bus;

- all control and address except CS_n, CKE latched at both

rising and falling edge of the clock

- CS_n, CKE latched at rising edge of the clock

- two data accesses per clock cycle

• Differential clock inputs (CK_t, CK_c)

• Bi-directional differential data strobe (DQS_t, DQS_c)

- Source synchronous data transaction aligned to bi-direc-

tional differential data strobe (DQS_t, DQS_c)

- Data outputs aligned to the edge of the data strobe

(DQS_t, DQS_c) when READ operation

- Data inputs aligned to the center of the data strobe

(DQS_t, DQS_c) when WRITE operation

• DM masks write data at the both rising and falling edge of

the data strobe

• Programmable RL (Read Latency) and WL (Write Latency)

• Programmable burst length: 8

• Auto refresh and self refresh supported

• All bank auto refresh and per bank auto refresh supported

• Auto TCSR (Temperature Compensated Self Refresh)

• PASR (Partial Array Self Refresh) by Bank Mask and Segment

Mask

• DS (Drive Strength)

• ZQ (Calibration)

• ODT (On Die Termination)

Rev 0.1 / Jul. 2016 4

Preliminary

H9TQ64A8GTCCUR

8GB eMMC (x8) / LPDDR3 8Gb(x32)

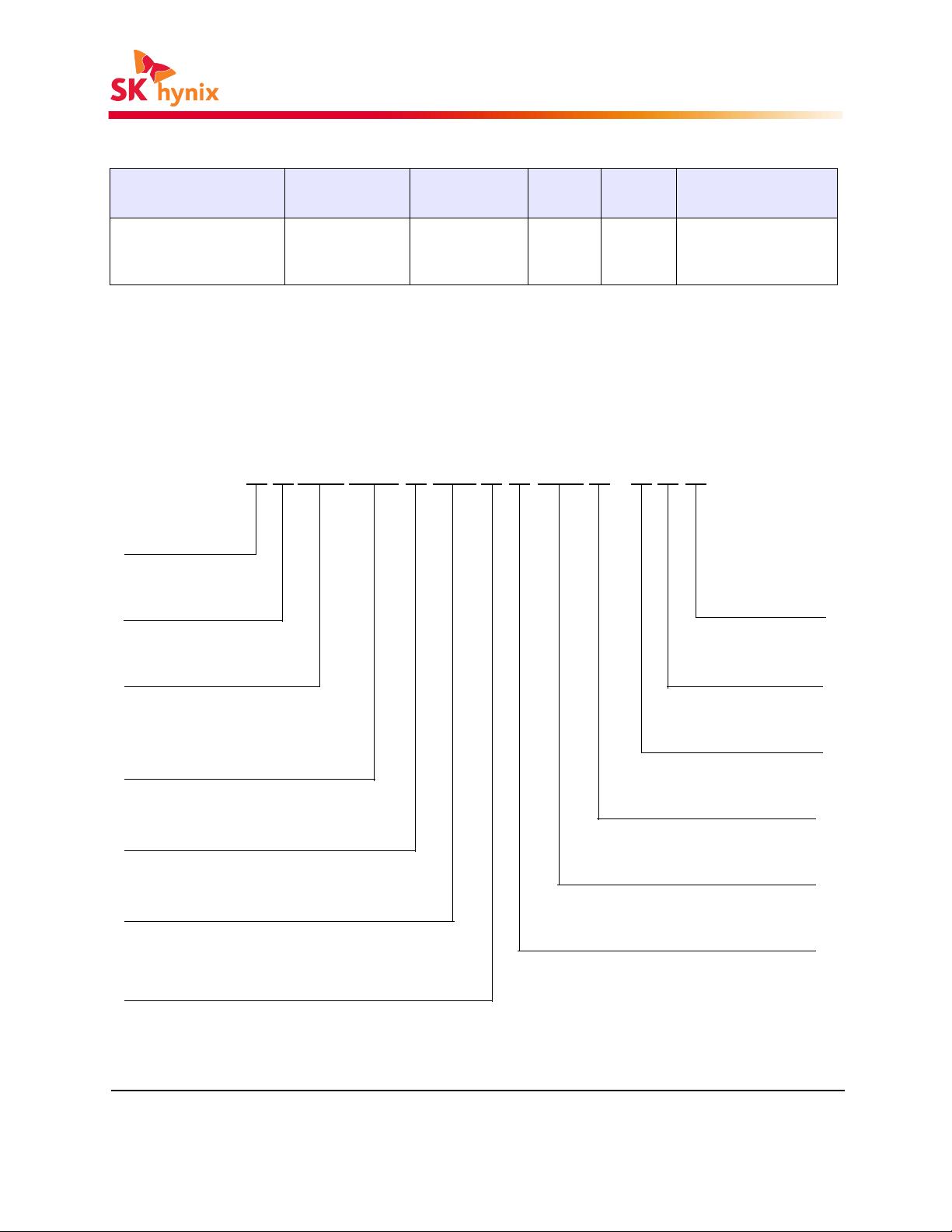

Functional Block Diagram

MultiMediaCard

Interface

e-NAND

MMC Controller

NAND Flash

Data In/Out

Control

eMMC Block Diagram

CK_t, CK_c

ZQ

DQ0~DQ31

CS0, CKE0

8Gb x32 device

CA0 ~ CA9

DM0~DM3,

VDD1, VDD2, VDDQ, Vref(CA/DQ)

VSS, VSSCA, VSSQ

(256M x 32)

Note

1. Total current consumption is dependent to user operating conditions. AC and DC Characteristics shown in

this specification are based on a single die. See the section of “DC Parameters and Operating Conditions”

DQS0_t~DQS3_t,

DQS0_c~DQS3_c,

DRAM Block Diagram

Rev 0.1 / Jul. 2016 5

Preliminary

H9TQ64A8GTCCUR

8GB eMMC (x8) / LPDDR3 8Gb(x32)

ORDERING INFORMATION

Part Number

Memory

Combination

Operation

Voltage

Density Speed Package

H9TQ64A8GTBCCUR-KUM

eMMC

LPDDR3

3.3V

1.8V/1.2/1.2/1.2

8GB (x8)

8Gb (x32)

200MHz

DDR3 1866

221Ball FBGA

(Lead & Halogen Free)

H 9 T Q 6 4 A 8 G T C C U R - K U M

MCP/PoP

Product Mode :

Density, Stack, Block Size

Voltage & I/O for NVM :

Voltage, I/O & Option for DRAM :

3.3V, x8

eMCP NAND DDR3

Density, Stack, CH & CS for DRAM :

eMMC Speed : 200Mhz

Package Material :

Lead & Halogen Free

Package Type :

Generation : 4th

& Page Buffer for NVM

:

64Gb, SDP, LB, MLC

8Gb, SDP

1.2v, x32, LPDDR3

FBGA 221 Ball 11.5x13

Temperature :

Standard (-25~85’C)

SK Hynix Memory

DRAM Speed :

1866Mbps

剩余199页未读,继续阅读

wicy

- 粉丝: 0

- 资源: 5

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 数据结构1800题含完整答案详解.doc

- 医疗企业薪酬系统设计与管理方案.pptx

- 界面与表面技术界面理论与表面技术要点PPT学习教案.pptx

- Java集合排序及java集合类详解(Collection、List、Map、Set)讲解.pdf

- 网页浏览器的开发 (2).pdf

- 路由器原理与设计讲稿6-交换网络.pptx

- 火电厂锅炉过热汽温控制系统设计.doc

- 企业识别CIS系统手册[收集].pdf

- 物业管理基础知识.pptx

- 第4章财务预测.pptx

- 《集成电路工艺设计及器件特性分析》——实验教学计算机仿真系.pptx

- 局域网内共享文件提示没有访问权限的问题借鉴.pdf

- 第5章网络营销策略.pptx

- 固井质量测井原理PPT教案.pptx

- 毕业实习总结6篇.doc

- UGNX建模基础篇草图模块PPT学习教案.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0