MSP430F149微控制器技术详解

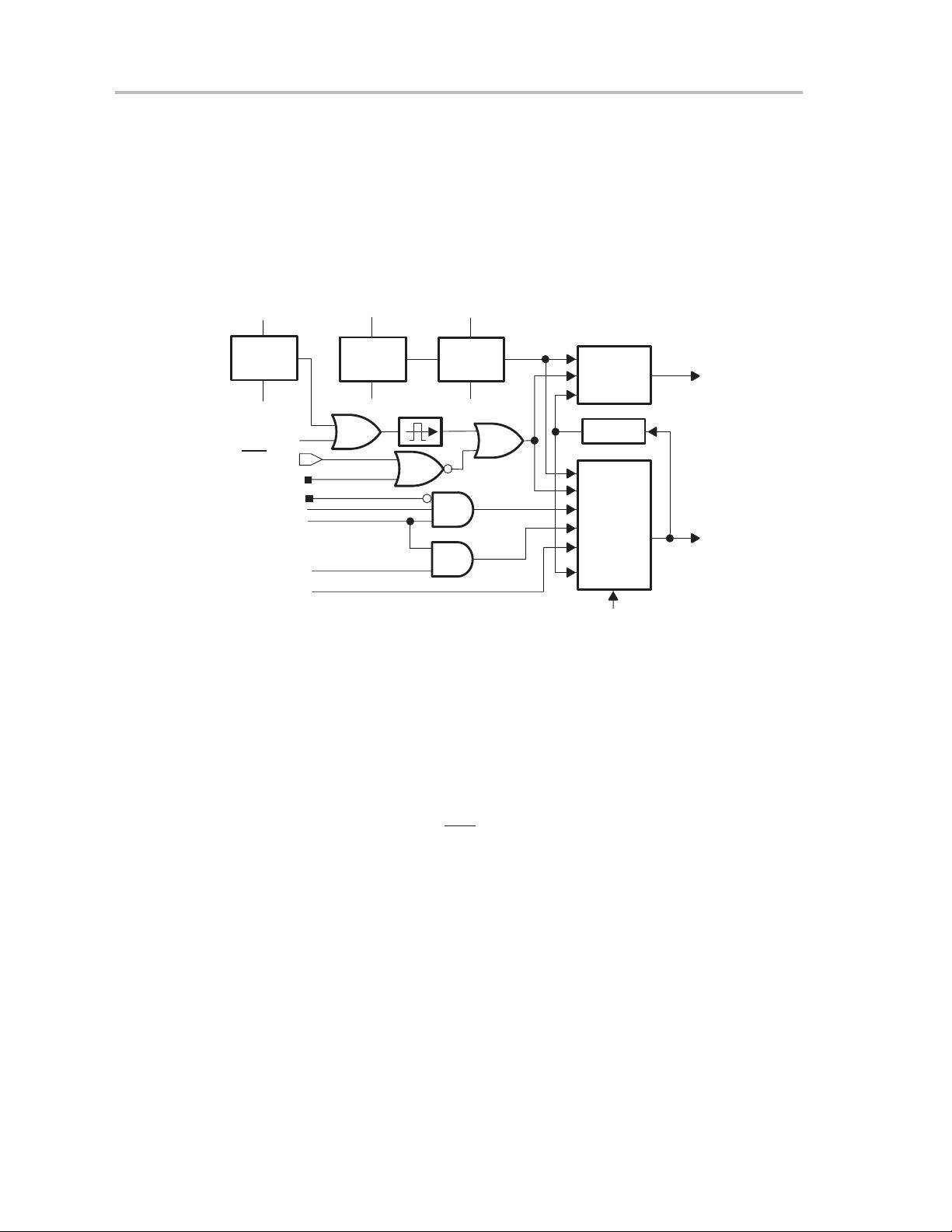

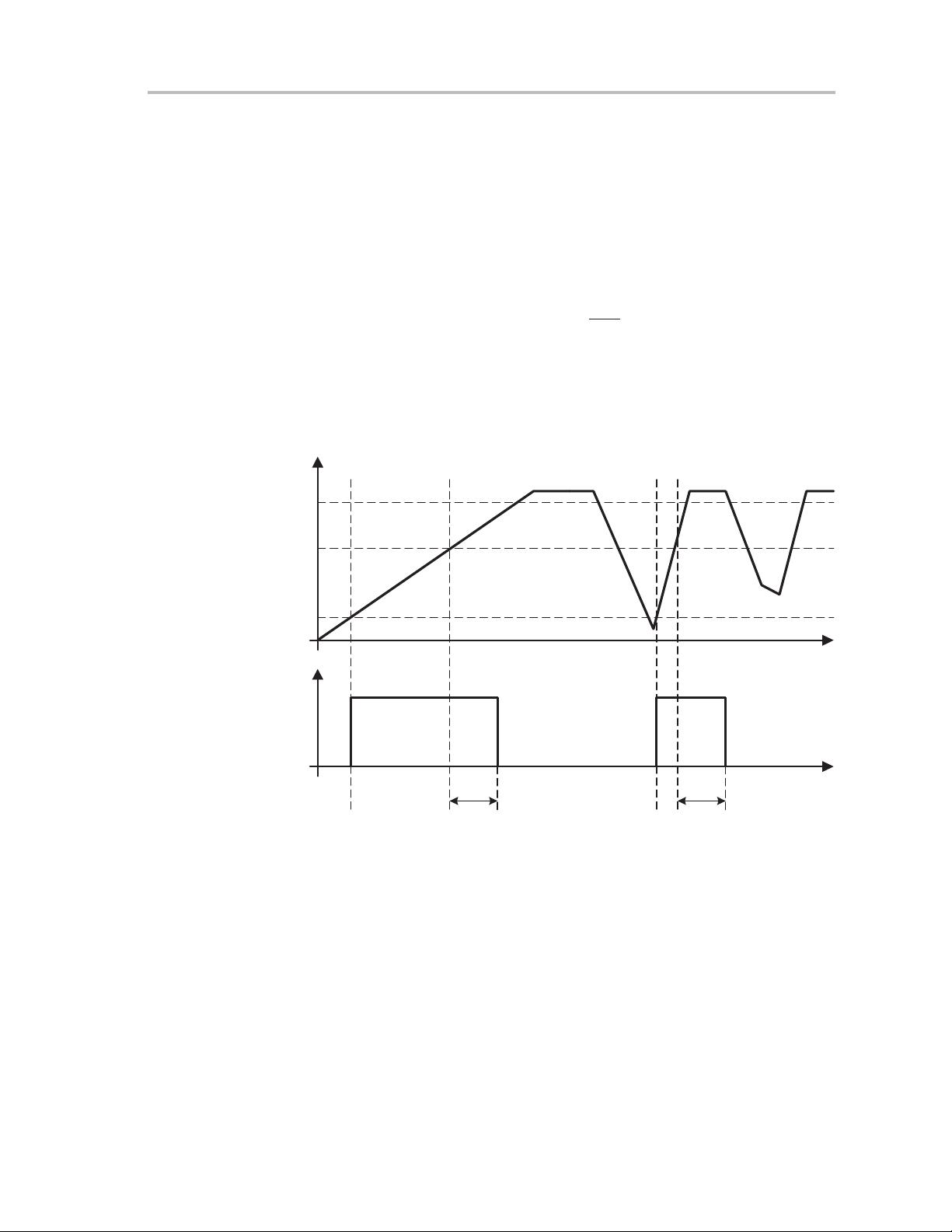

"MSP430F149数据手册提供了关于MSP430F149微控制器的详细信息,包括其模块和外围设备的功能。该手册旨在概述MSP430x1xx系列器件的一般特性,但并非所有功能在所有器件上都存在。用户需要参考具体设备的数据表获取详细信息。此外,手册警告该设备适用于实验室测试环境,可能产生和辐射射频能量,未针对计算设备的FCC标准进行合规性测试。" MSP430F149是德州仪器(Texas Instruments)推出的一款超低功耗微控制器,属于MSP430系列。这个系列的器件以高效能和低能耗著称,广泛应用于各种嵌入式系统,如便携式测量设备、传感器网络和实时控制应用。 手册的前言部分指出,该文档主要介绍了MSP430x1xx家族的模块和外围设备,但请注意,不是每个模块或外设都在所有器件上完全实现。它们在不同设备家族之间可能存在实现上的差异,或者在个别设备上可能不完全实现。因此,为了获取关于MSP430F149的确切引脚功能、内部信号连接和操作参数等详细信息,用户需要查阅特定设备的数据表。 手册还提到了相关的德州仪器文档资源,用户可以在官方网站http://www.ti.com/msp430找到更多与MSP430系列相关的文档。这可能包括应用笔记、开发工具文档、软件库和其他支持材料,这些资源对于开发者来说是非常宝贵的,可以帮助他们更好地理解和利用MSP430F149的潜力。 关于FCC警告,手册强调该设备设计用于实验室测试环境,它能够生成、使用并可能辐射射频能量。然而,该设备并没有按照适用于计算机设备的联邦通信委员会(FCC)规定进行合规性测试。这意味着在实际部署时,用户需要确保其使用场景符合相关的电磁兼容(EMC)和射频法规要求。 MSP430F149数据手册是了解和使用这款微控制器的基础资料,涵盖了基本架构、功能特性和操作指南,同时提醒用户注意合规性和设备的具体适用范围。对于开发人员来说,深入研究这份手册是掌握MSP430F149的关键,以便在项目中充分利用其低功耗和高性能的优势。

剩余415页未读,继续阅读

- 粉丝: 128

- 资源: 20

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- VMP技术解析:Handle块优化与壳模板初始化

- C++ Primer 第四版更新:现代编程风格与标准库

- 计算机系统基础实验:缓冲区溢出攻击(Lab3)

- 中国结算网上业务平台:证券登记操作详解与常见问题

- FPGA驱动的五子棋博弈系统:加速与创新娱乐体验

- 多旋翼飞行器定点位置控制器设计实验

- 基于流量预测与潮汐效应的动态载频优化策略

- SQL练习:查询分析与高级操作

- 海底数据中心散热优化:从MATLAB到动态模拟

- 移动应用作业:MyDiaryBook - Google Material Design 日记APP

- Linux提权技术详解:从内核漏洞到Sudo配置错误

- 93分钟快速入门 LaTeX:从入门到实践

- 5G测试新挑战与罗德与施瓦茨解决方案

- EAS系统性能优化与故障诊断指南

- Java并发编程:JUC核心概念解析与应用

- 数据结构实验报告:基于不同存储结构的线性表和树实现

信息提交成功

信息提交成功