一个系统只有一个 P-Bank 已经不能满足容量的需要。所以,芯片组开 始可以支持多个 P-

Bank,一次选择一个 P-Bank 工作,这就有了芯片组支持多少(物理)Bank 的说法。而在 Intel

的 定义中,则称 P-Bank 为行(Row),比如 845G 芯片组支持 4 个行,也就是说它支持 4 个

P-Bank。另外,在一些文档中 ,也把 P-Bank 称为 Rank(列)。

回到开头的话题,DIMM 是 SDRAM 集合形式的最终体现,每个 DIMM 至少包含一个 P-Bank

的芯片集合。在目前的 DIMM 标准中,每个模组最多可以包含两个 P-Bank 的内存芯片集合,

虽然理论上完全可以在一个 DIMM 上支持多个 P-Bank,比如 SDRAM DIMM 就有 4 个芯片选

择信号,理论上可以控制 4 个 P-Bank 的芯片集合。只是由于某种原因而没有这么去做。比如

设计难度、 制造成本、芯片组的配合等。至于 DIMM 的面数与 P-Bank 数量的关系,在 2001

年 2 月的专题中已经明确了,面数≠P-Ba nk 数,只有在知道芯片位宽的情况下,才能确定 P-

Bank 的数量,大度 256MB 内存就是明显一例,而这种情况在 Regist ered 模组中非常普遍。有

关内存模组的设计,将在后面的相关章节中继续探讨。

二、 SDRAM 内存芯片的内部结构

1、逻辑 Bank 与芯片位宽

讲完 SDRAM 的外在形式,就该深入了解 SDRAM 的内部结构了。这里主要的概念就是逻辑

Bank。简单地说,SDRAM 的内部 是一个存储阵列。因为如果是管道式存储(就如排队买

票),就很难做到随机访问了。

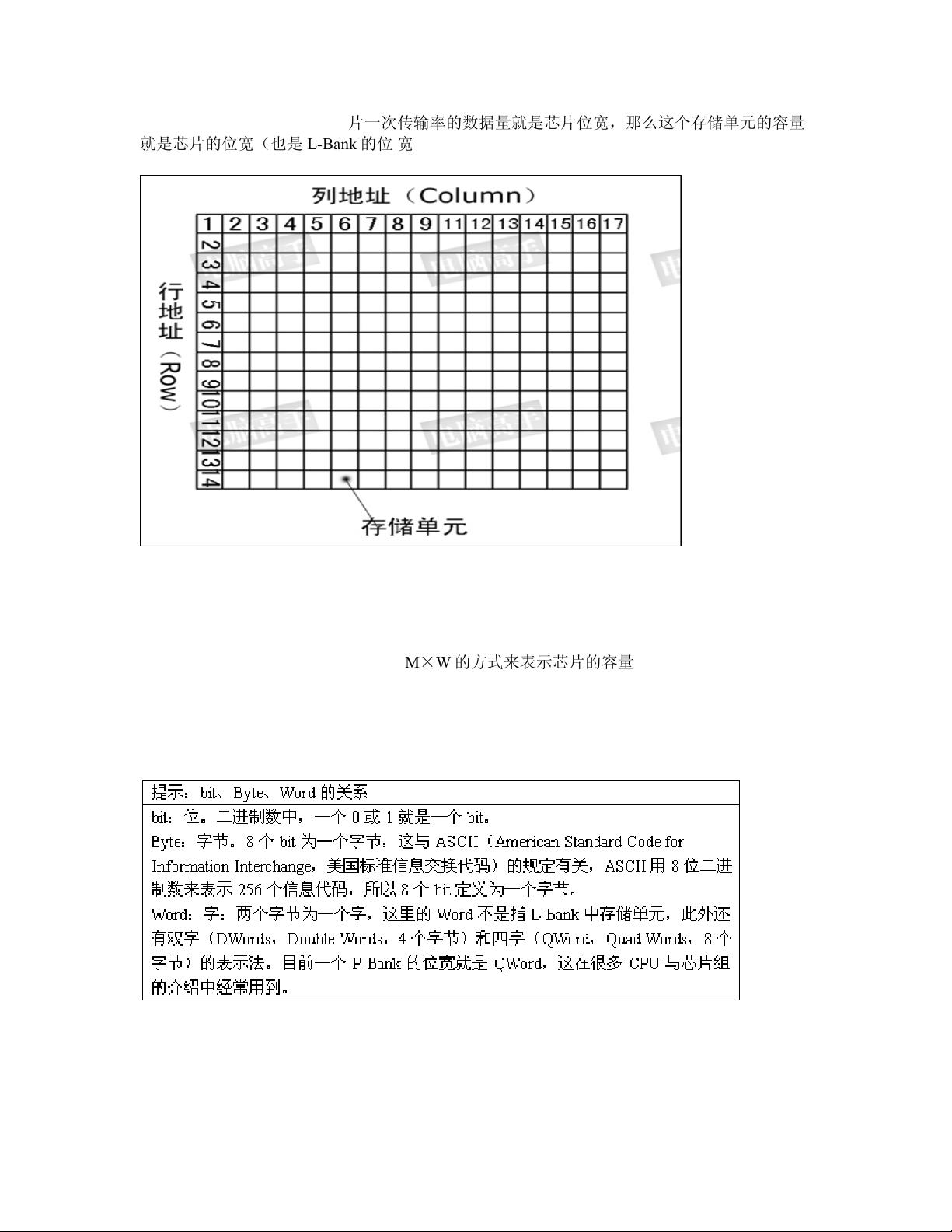

阵列就如同表格一样,将数据“填”进去,你可以它想象成一张表格。和表格的检索原理一

样,先指定一个行(Row),再指定一个列 (Column),

我们就可以准确地找到所需要的单

元格,这就是内存芯片寻址的基本原理。对于内存,这个单元格可称为存储单元, 那么这个表

格(存储阵列)叫什么呢?它就是逻辑 Bank(Logical Bank,下文简称 L-Bank)。

由于技术、成本等原因,不可能只做一个全容量的 L-Bank,而且最重要的是,由于 SDRAM

的工作原理限制,单一的 L-Ban k 将会造成非常严重的寻址冲突,大幅降低内存效率(在后文

中将详细讲述)。所以人们在 SDRAM 内部分割成多个 L-Bank,较 早以前是两个,目前基本

都是 4 个,这也是 SDRAM 规范中的最高 L-Bank 数量。到了 RDRAM 则最多达到了 32 个,在

最新 DDR-Ⅱ的标准中,L-Bank 的数量也提高到了 8 个。

这样,在进行寻址时就要先确定是哪个 L-Bank,然后再在这个选定的 L-Bank 中选择相应的行

与列进行寻址。可见对内存的访 问,一次只能是一个 L-Bank 工作,而每次与北桥交换的数据

就是 L-Bank 存储阵列中一个“存储单元”的容量。在某些厂商的 表述中,将 L-Bank 中的存

储单元称为 Word(此处代表位的集合而不是字节的集合)。

评论1