没有合适的资源?快使用搜索试试~ 我知道了~

首页编写高效率的testbench

资源详情

资源评论

资源推荐

编写高效率的 testbench

简介:

由于设计的规模越来越大也越来越复杂,数字设计的验证已经成为一个日益困难和繁琐

的任务。

验证工程师们依靠一些验证工具和方法来应付这个挑战。对于几百万门的大型设计,

工程师们一般使用一套形式验证(formal verification)工具。然而对于一些小型的设计,设

计工程师常常发现用带有 testbench 的 HDL 仿真器就可以很好地进行验证。

Testbench 已

经成为一个验证高级语言(HLL --High-Level Language) 设计的标准方法。

通常 testbench 完成如下的任务:

1. 实例化需要测试的设计(

DUT);

2. 通过对 DUT 模型加载测试向量来仿真设计;

3. 将输出结果到终端或波形窗口中加以视觉检视;

4. 另外,将实际结果和预期结果进行比较。

通常 testbe

nch 用工业标准的 VHDL 或 Verilog 硬件描述语言来编写。Testbench 调用功

能设计,然后进行仿真。复杂的 testbench 完成一些附加的功能—例如它们包含一些逻辑来

选择产生合适的设计激励或比较实际结果和预期结果。

后续的章节描述了一个仔细构建的 t

estbench 的结构,并且提供了一个自动比较实际结

果与预期结果的进行自我检查的 testbench 例子。

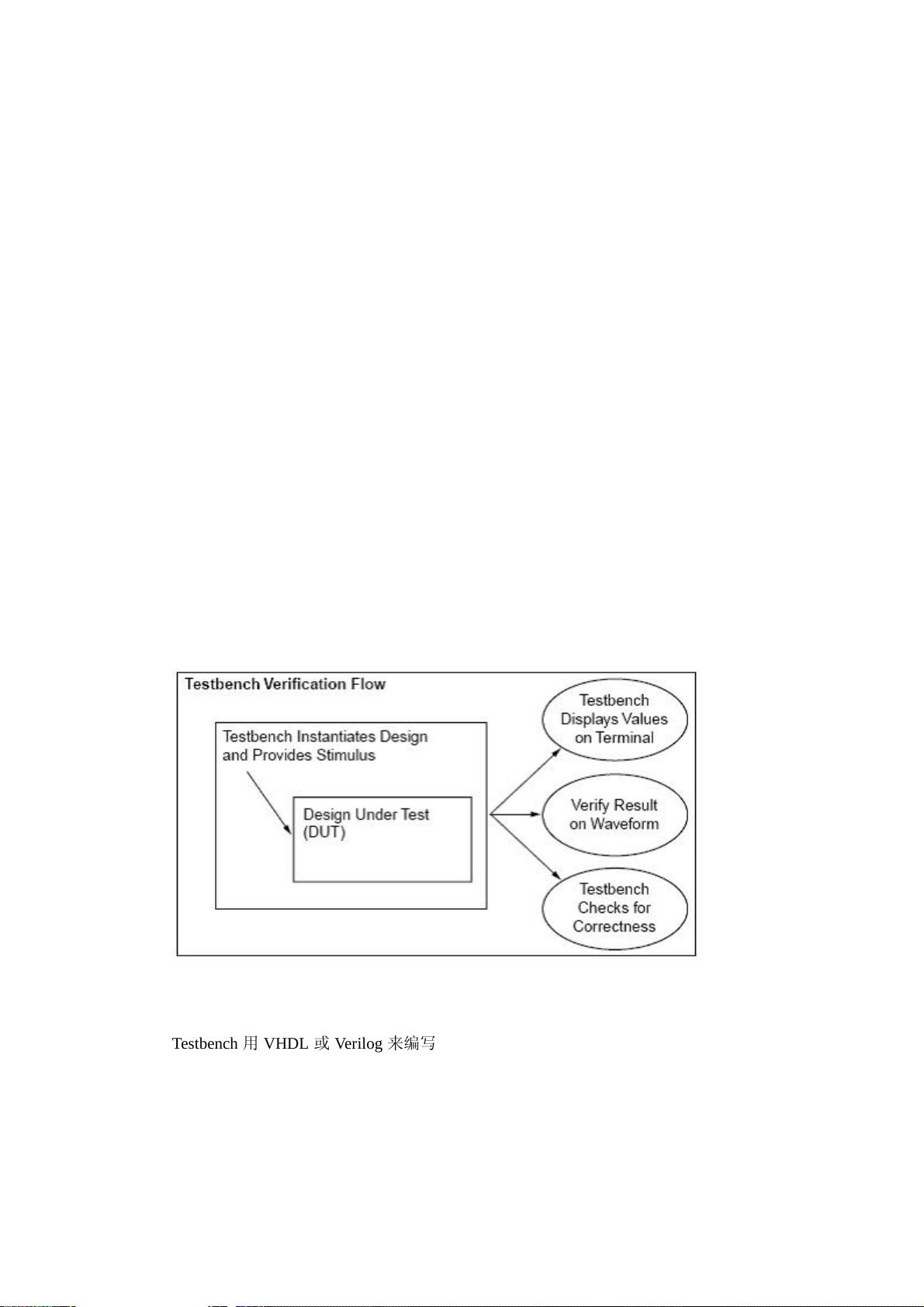

图 1 给出了一个如上所描述步骤的标准 HD

L 验证流程。由于 testbench 使用 VHDL 或

Verilog 来描述,testbench 的验证过程可以根据不同的平台或不同的软件工具实现。由于

VHDL 或 Verilog 是公开的通用标准,使用 VHDL 或 Verilog 编写的 testbench 以后也可以毫

无困难地重用(reuse)。

图 1 使用 Testbench 的 HDL 验证流程

构建 Te

stbench

Testbench 用 VHDL 或 V

erilog 来编写。由于 testbench 只用来进行仿真,它们没有那些

适用于综合的 RTL 语言子集的语法约束限制,而是所有的行为结构都可以使用。因而

testbench 可以编写的更为通用,使得它们可以更容易维护。

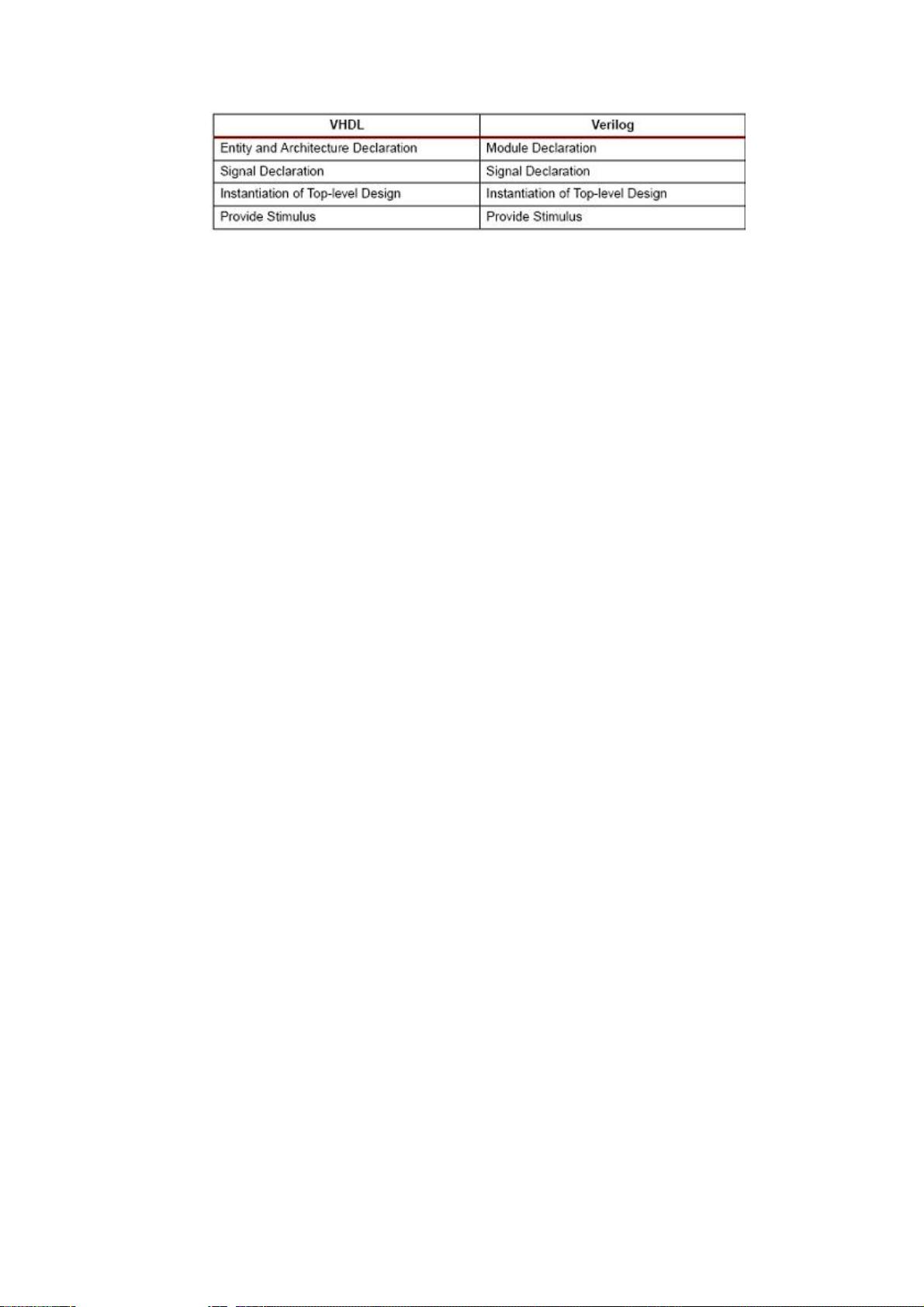

所有 testbench 包含了如表 1 的基本程序段。正如上面所提到的,testbench 通常包含附

加功能,如在终端上可视的结果和内建的错误检测。

表 1 testbench 的基本程序段

下面的例子介绍 testbench 中经常使用的结构。

产生时钟信号

使用系统时钟的时序逻辑设计必须产生时钟。时钟信号在 VHDL 或 Ve rilo g 中可以很容

易地实现。以下是 VHDL 和 Ve rilog 的时钟发生示例。

VHDL:

-- Declare a clock period constant.

Constant ClockPeriod : TIME := 10 ns;

-- Clock Generation method 1:

Clock <= not Clock after ClockPeriod / 2;

-- Clock Generation method 2:

GENERATE CLOCK: process

begin

wait for (ClockPeriod / 2)

Clock <= ’1’;

wait for (ClockPeriod / 2)

Clock <= ’0’;

end process;

Verilog:

// Declare a clock period constant.

Parameter ClockPeriod = 10;

// Clock Generation method 1:

initial begin

Clock = 0;

forever Clock = #(ClockPeriod / 2) ~ Clock;

end

// Clock Generation method 2:

always #(ClockPeriod / 2) Clock = ~Clock;

提供激励信号

为了获得 testbench 的验证结果,激励必须作用于 DUT。在 testbench 中使用的并行激励

块提供必要的激励。激励的产生可以采用两个方法:绝对时间激励和相对时间激励。在第一

个方法里,仿真变量相对于仿真时间零点进行详细描述。相对而言,相对时间激励提供初始

值,然后等待一个事件来重新触发激励。根据设计者的需要,两种方法可以在 testbench 中

同时使用。

下面的程序段是绝对时间激励的例子。

initial begin

reset = 1;

load = 0;

cout_updn = 0;

#100 reset = 0;

#20 load = 1;

#20 count_updn = 1;

end

下面的程序段是相对时间激励的例子。

always @(posedge clock)

tb_count <= tb_count + 1;

initial begin

if(tb_count <= 5)

begin

reset = 1;

load = 0;

count_updn = 0;

end

else

begin

reset = 0;

load = 1;

count_updn = 1;

end

end

initial begin

if(count = 1100) begin

count_updn <= 0;

$display(“Terminal count Reached,now counting down”);

end

end

Verilog 的 initial 块与文件中的其他 initial 块是同时执行。然而,在每一个 initial 块中,

事件是按照书写的顺序执行的。这说明在每一个并行块中的激励序列从序仿真时间零点开

始。为了代码有更好的可读性和更方便的可维护性,应采用多个块来分割复杂的测试激励。

显示结果

在 Verilog 中可以非常方便地使用系统函数$display()和$monitor()显示结果。VHDL

没有等效的显示指令,它提供了 std_textio 标准文本输入输出程序包。它允许文件的 i/o 重定

向到显示终端窗口(作为这个技术的示例,参看下面的自较验查验证设计)

下面是 verilog 示例,它将在终端屏幕上显示一些值。

// pipes the ASCII results to the terminal or text editor

initial begin

$timeformat(-9,1,"ns",12);

$display(" Time Clk Rst Ld SftRg Data Sel");

$monitor("%t %b %b %b %b %b %b", $realtime,

clock, reset, load, shiftreg, data, sel);

end

系统函数$display 在终端屏幕上输出引用的附加说明文字(“。。。”)。系统函数$monitor

操作不同。因为它的输出是事件驱动的。例中的变量$realtime(由用户赋值到当前的仿真时

间)用于触发信号列表中值的显示。信号表由变量$realtime 开始,跟随其他将要显示的信号

名(clock, reset, load 等)。以%开始的关键字包含一个格式描述的表,用来控制如何格式化

显示信号列表中的每个信号的值。格式列表是位置确定的。每个格式说明有序地与信号列表

中的信号顺序相关。比如%t 说明规定了$realtime 的值是时间格式。并且第一个%b 说明符格

式化 clock 的值是二进制形式。Verilog 提供附加的格式说明,比如%h 用于说明十六进制,

%d 说明十进制,%c 说明显示为八进制。图 2 说明格式显示结果

图 2 仿真结果

简单的 testbench

简单的 testbench 实例化用户设计,然后提供相应的激励。测试输出被图形化显示在仿

真器的波形窗口里或者作为文本发送到用户的终端或者是管道输出文本。

以下是一个简单的用 Verilog 实现的设计,它实现了一个移位寄存器的功能。

module shift_reg (clock, reset, load, sel, data, shiftreg);

input clock;

input reset;

input load;

input [1:0] sel;

input [4:0] data;

output [4:0] shiftreg;

reg [4:0] shiftreg;

always @ (posedge clock)

begin

if (reset)

剩余15页未读,继续阅读

jingjin_huang

- 粉丝: 0

- 资源: 5

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0