没有合适的资源?快使用搜索试试~ 我知道了~

首页IOT-OS之RT-Thread(十五)— SDIO设备对象管理 + AP6181(BCM43362) WiFi模块

本章介绍SDIO Wi-Fi模块的驱动实现过程,对SDIO不熟悉的可以先参阅博客:SD/MMC + SDIO,对RT-Thread驱动分层与主从分离思想不熟悉的,可以先参阅博客:驱动分层与主从分离思想。 一、AP6181 Wi-Fi模块简介 1.1 AP6181 硬件接口 Pandora开发板为我们提供了一个板载Wi-Fi 芯片 — AP6181,我们不需要再外接扩展模块(比如 ESP8266)即可实现连接 Wi-Fi 并访问外部网络的功能。我们先看下Pandora开发板原理图中 Wi-Fi 模块 AP6181 的硬件接线原理图: 正基公司的 AP6181 Wi-Fi 模组具有以下特点: 符

资源详情

资源评论

资源推荐

IOT-OS之之RT-Thread(十五)(十五)— SDIO设备对象管理设备对象管理 + AP6181(BCM43362) WiFi模块模块

本章介绍SDIO Wi-Fi模块的驱动实现过程,对SDIO不熟悉的可以先参阅博客:SD/MMC + SDIO,对RT-Thread驱动分层与主从分离思想不熟悉的,可以先参阅博客:驱动分层与主

从分离思想。

一、一、AP6181 Wi-Fi模块简介模块简介

1.1 AP6181 硬件接口硬件接口

Pandora开发板为我们提供了一个板载Wi-Fi 芯片 — AP6181,我们不需要再外接扩展模块(比如 ESP8266)即可实现连接 Wi-Fi 并访问外部网络的功能。我们先看下Pandora开发板

原理图中 Wi-Fi 模块 AP6181 的硬件接线原理图:

正基公司的 AP6181 Wi-Fi 模组具有以下特点:

符合IEEE 802.11 b/g/n标准,可以实现单通道高达72.2Mbps 的传输速度(IEEE 802.11n 标准);

支持标准接口SDIO v2.0(时钟频率高速模式可达50MHz,数据线位宽支持4位或1位模式);

集成ARM Cortex-M3 (带有片上存储器)以运行 IEEE802.11 固件(用于Wi-Fi 数据帧的处理);

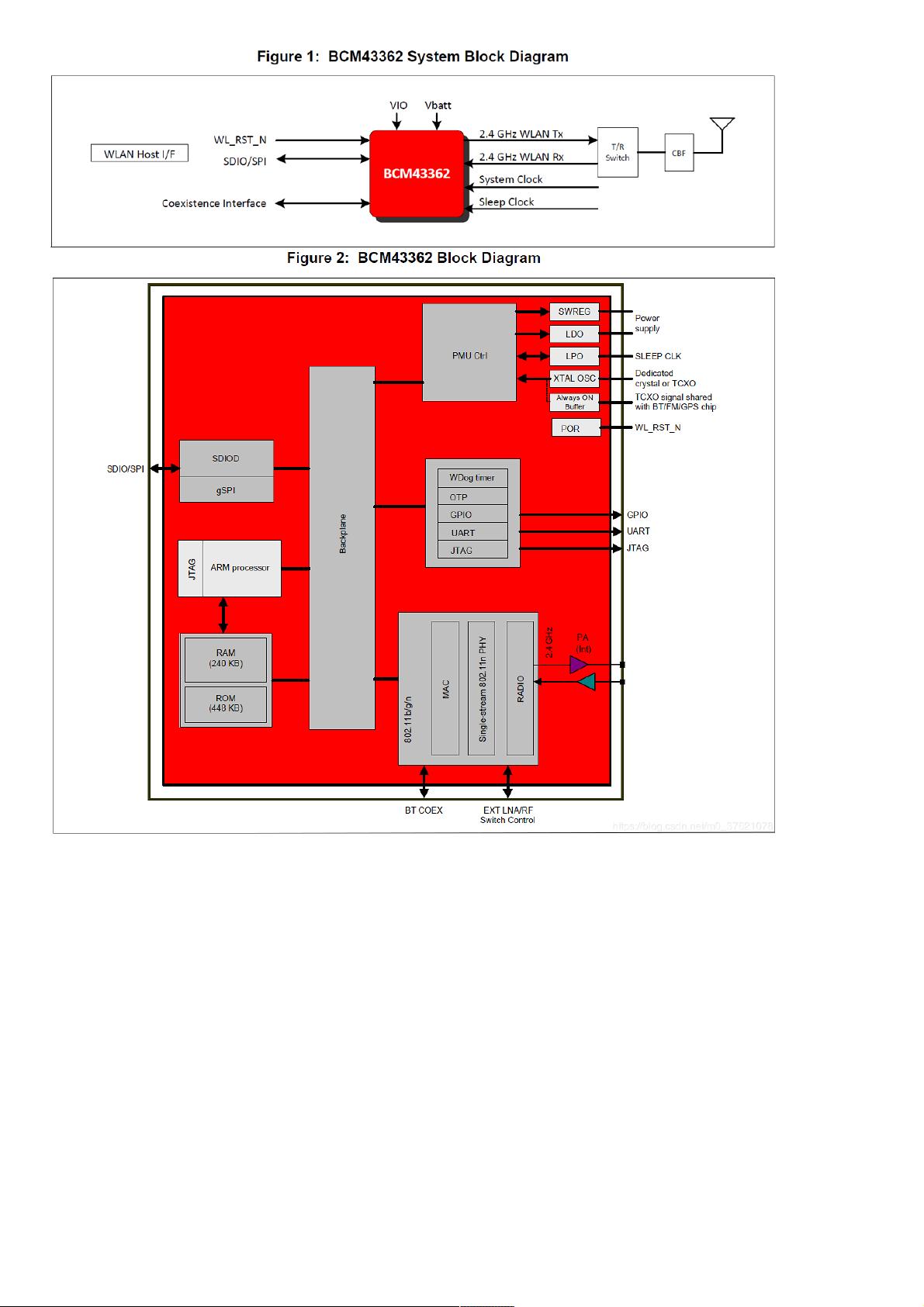

AP6181 Wi-Fi 模组内部实际封装的是Broadcom 43362 芯片,接下来看看 BCM43362 芯片内部都有哪些模块(图片取自BCM43362_datasheet):

从上面 BCM43362 系统框图可以看出,内部是集成了ARM处理器及RAM/ROM存储空间的,用于运行 Wi-Fi 固件,管理 Wi-Fi MAC/PHY/RADIO层的无线链路信道资源,完成 Wi-Fi

数据帧 与 以太网数据帧 之间的转换等功能。

AP6181 / BCM43362 模组外接引脚如下:

SDIO(Secure Digital Input Output):包括DATA[0:3]、CMD、CLK 共6个引脚,支持SDIO V2.0总线标准;

WiFi INT / WL_HOST_WAKE:WLAN wake-up Host,当接收到数据帧后,产生中断信号,唤醒主机Host接收并处理该数据帧;

WL_REG_ON:Internal regulators power enable/disable,我觉得跟BCM43362芯片引脚 WL_RST_N / POR(WLAN Reset / Power-On Reset,该引脚持续拉低则BCM 43362进入

Power-down状态,给该引脚一个低电平脉冲则BCM 43362进入Reset 状态) 功能相似;

Coexistence interface:相近频率的无线设备(比如蓝牙)通过该接口与BCM43362连接,可以共享BCM43362的无线介质(MAC/PHY/RADIO层及其后的ANT等资源),我们暂时

不需要蓝牙功能,该引脚可忽略;

WL_BT_ANT:向外与板载丝印天线相连,向内通过 T/R Switch 与WLAN Tx/Rx 相连,AP6181把BCM43362与T/R Switch封装到一起了;

System Clock / XTAL:外接晶振XTAL_IN / XTAL_OUT,为AP6181或BCM43362提供系统时钟;

Sleep Clock / LPO:睡眠时钟或者低功耗时钟输入,Pandora开发板并未使用该引脚;

VBAT / VDDIO / LDO:Power supply,为AP6181或BCM43362提供电源支持。

从AP6181 模块的接线图可以看出,我们需要重点关注的是SDIO、WiFi INT、WL_REG_ON这三组共8个引脚,其余的引脚Pandora 开发板上已经帮我们接好了。SDIO引脚的定义在

博客:SD/MMC + SDIO中已经有过介绍,WiFi INT引脚需要绑定自定义的中断处理函数,WL_REG_ON引脚是内部稳压电源的使能引脚,在WLAN模块正常工作时需要将其拉高,

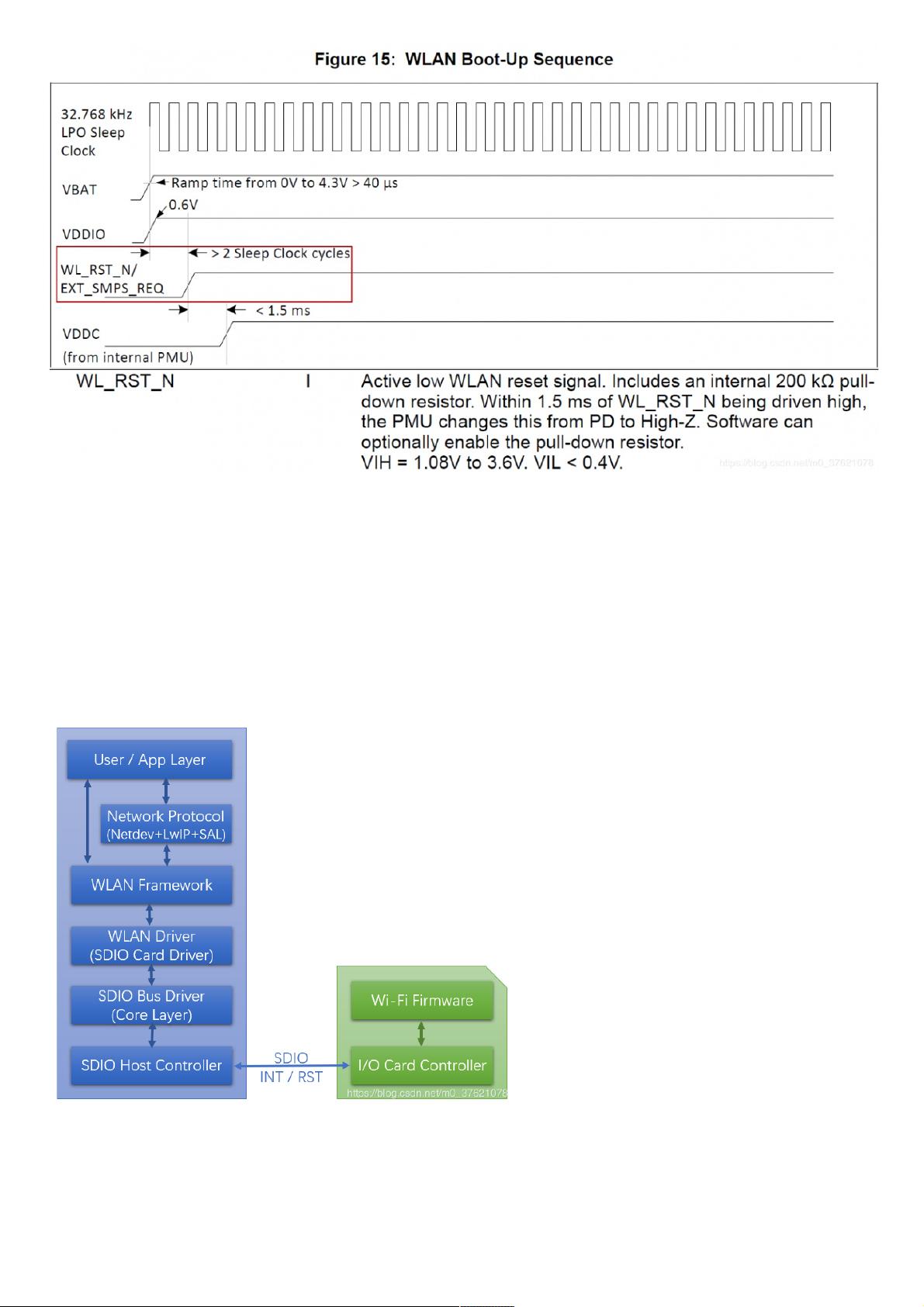

对该引脚的拉高时间有什么要求吗?我们看下AP6181 / BCM43362 WLAN模块的启动时序图:

从上图可以看出,WL_REG_ON引脚需要在 VBAT / VDDIO 上电2个睡眠时钟周期(32.768KHZ)后,1.5ms之内完成电平拉高,我们可以在 AP6181 驱动代码中设置WL_REG_ON

引脚的拉高时机(比如0.1ms ~ 1ms)与动作。

1.2 AP6181 驱动层级驱动层级

AP6181 模块不像 ESP8266 模块那样内部集成了 WLAN驱动与TCP/IP协议栈,甚至AP6181 为了节省成本,模块内可能就没有可供存放WLAN驱动代码的ROM区域。

AP6181 模块内部有ARM处理器和RAM 内存区域,在工作时也需要运行WLAN固件程序以处理WLAN数据帧,这就需要开发者在初始化该模块时,将主控端Flash中保存的WLAN固

件代码传送到AP6181 模块内(RAM内存区域)。这样做虽然增加了点主控端的驱动代码和ROM占用空间,但也有三个明显的好处:

省去了大部分ROM空间,降低了模块的成本;

不需要在模块出厂时单独为其烧录固件代码,减少了生产环节;

固件代码便于维护和升级,只需要更新主控端Flash内的固件文件,模块初始化时自动会将新的固件代码传输到模块内。

由于Nand Flash成本比Nor Flash(可以在芯片内执行代码,而不需先拷贝到RAM内存中)更低,且在主控端Flash中更新固件代码更灵活方便,因此这种固件加载方式在设备驱动开发

中很常见。

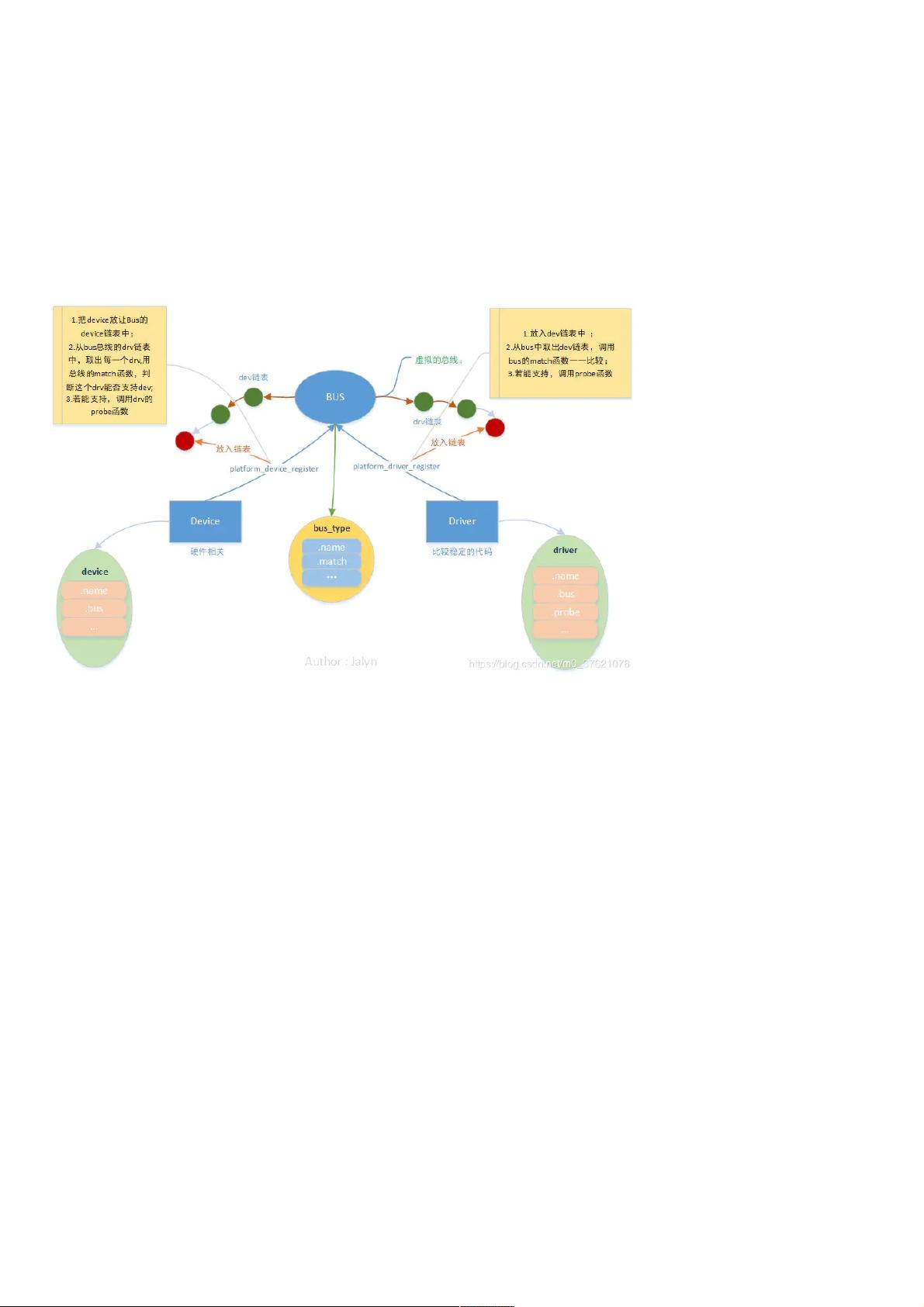

AP6181 模块是基于SDIO 总线协议进行通信的,因此模块与主控端最底层应该分别是SDIO Card controller与Host controller。SDIO Card内有一个CSA(Code Storage Area)可以用来

存放WLAN固件代码(由AP6181 芯片供应商提供),SDIO Host controller上层则分别是SDIO Bus Driver和SDIO Card Driver。AP6181 模块提供的是Wi-Fi 网络访问服务,因此这里

的SDIO Card Driver 也就是 WLAN Driver(由AP6181 芯片供应商提供公版驱动,开发者再根据需要调整或移植)。当 WLAN Driver 适配完成,接下来的Wi-Fi 管理与网络服务就可

以交给操作系统了,Pandora 开发板上的 AP6181 模块WLAN驱动及TCP/IP协议栈的层级关系图如下:

RT-Thread为方便我们管理Wi-Fi 设备,提供了一个WLAN管理框架,相当于WLAN 设备无关层,可以向上提供统一的访问接口。当我们更换 Wi-Fi 模块时,只需要修改相应的适配代

码,不需要修改上层的应用程序。

二二 SDIO设备对象管理设备对象管理

前篇博客:SD/MMC + SDIO已经简单介绍过SDIO协议的三个部分:SDIO Host controller、SDIO Bus protocol、SDIO Card。上面已经简单介绍过本文需要用到的 SDIO Card —

AP6181 模块,这里重点介绍主机端的SDIO Host controller 与 SDIO Bus protocol,包括SDIO Card Driver — WLAN Driver。

前篇博客:驱动分层与主从分离思想介绍了RT-Thread I/O 设备驱动管理的分层思想和一主多从工作模式的主从分离思想,也提到了Linux的总线设备驱动模型。SDIO驱动也可以看

出明显的分层结构(只列出了SDIO相关的驱动文件,省去了MMC/SD相关的驱动文件):

// I/O 设备管理层

rt-thread-4.0.1\include\rtdef.h

rt-thread-4.0.1\src\device.c

// 设备驱动框架层

rt-thread-4.0.1\components\drivers\include\drivers\sdio.h

rt-thread-4.0.1\components\drivers\sdio\sdio.c

rt-thread-4.0.1\components\drivers\include\drivers\mmcsd_card.h

rt-thread-4.0.1\components\drivers\include\drivers\mmcsd_core.h

rt-thread-4.0.1\components\drivers\include\drivers\mmcsd_cmd.h

rt-thread-4.0.1\components\drivers\sdio\mmcsd_core.c

rt-thread-4.0.1\components\drivers\include\drivers\mmcsd_host.h

// 设备驱动层

libraries\HAL_Drivers\drv_sdio.h

libraries\HAL_Drivers\drv_sdio.c

SDIO的设备驱动框架层还可以细分为SDIO Card Layer、Core Layer、Host Layer,但这种分层没有清晰的展示出Host与Card的主从分离思想。上面并没有展示SDIO Card Driver —

WLAN Driver 的相关文件,我也不知道应该将其放到设备驱动框架层还是设备驱动层。

如果按照主从分离思想看,SDIO协议可以分为主机Host 与卡设备Card,I/O Card可能支持的功能模块比较多(1个I/O Card最多可以包含7个功能模块),驱动种类与数量自然也比

较多。如果我们把 I/O Card和 function device driver 看作一体,驱动代码的复用性就比较低。如果我们我们借鉴Linux的总线设备驱动模型(如下图所示),将 I/O Card和 function

device driver 也分开,就可以根据需要灵活匹配 Driver 与 Function Device,不仅实现了Host — Card 的主从分离,也实现了 Function Device — Function Driver 的设备驱动分离,符

合编写代码的高内聚、低耦合原则。

一个总线Bus 分别管理一个设备链表device_list 和一个驱动链表 driver_list,当新注册一个I/O Card/Device 或 Function device Driver 时,探测已有的 driver_list 或 device_list 并尝试

与自己匹配(调用Bus提供的match接口函数)。当Driver 与 Device 完成匹配后,就可以调用Driver提供的probe接口函数完成Device设备的初始化,后面就可以通过Driver提供的

API 来访问Device设备,实现相应功能的扩展服务。

2.1 SDIO Bus Driver

2.1.1 Host 数据结构描述数据结构描述

SDIO Bus要给出Command、Response、Data三部分分别是如何描述、配置和传输的,而这三部分的传输是受主机Host 控制的,在介绍Command/Response与Data的描述结构前,

先介绍下主机Host 是如何描述的:

// rt-thread-4.0.1\components\drivers\include\drivers\mmcsd_host.h

struct rt_mmcsd_host {

struct rt_mmcsd_card *card;

const struct rt_mmcsd_host_ops *ops;

rt_uint32_t freq_min;

rt_uint32_t freq_max;

struct rt_mmcsd_io_cfg io_cfg;

rt_uint32_t valid_ocr; /* current valid OCR */

#define VDD_165_195 (1 << 7) /* VDD voltage 1.65 - 1.95 */

#define VDD_20_21 (1 << 8) /* VDD voltage 2.0 ~ 2.1 */

#define VDD_21_22 (1 << 9) /* VDD voltage 2.1 ~ 2.2 */

#define VDD_22_23 (1 << 10) /* VDD voltage 2.2 ~ 2.3 */

#define VDD_23_24 (1 << 11) /* VDD voltage 2.3 ~ 2.4 */

#define VDD_24_25 (1 << 12) /* VDD voltage 2.4 ~ 2.5 */

#define VDD_25_26 (1 << 13) /* VDD voltage 2.5 ~ 2.6 */

#define VDD_26_27 (1 << 14) /* VDD voltage 2.6 ~ 2.7 */

#define VDD_27_28 (1 << 15) /* VDD voltage 2.7 ~ 2.8 */

#define VDD_28_29 (1 << 16) /* VDD voltage 2.8 ~ 2.9 */

#define VDD_29_30 (1 << 17) /* VDD voltage 2.9 ~ 3.0 */

#define VDD_30_31 (1 << 18) /* VDD voltage 3.0 ~ 3.1 */

#define VDD_31_32 (1 << 19) /* VDD voltage 3.1 ~ 3.2 */

#define VDD_32_33 (1 << 20) /* VDD voltage 3.2 ~ 3.3 */

#define VDD_33_34 (1 << 21) /* VDD voltage 3.3 ~ 3.4 */

#define VDD_34_35 (1 << 22) /* VDD voltage 3.4 ~ 3.5 */

#define VDD_35_36 (1 << 23) /* VDD voltage 3.5 ~ 3.6 */

rt_uint32_t flags; /* define device capabilities */

#define MMCSD_BUSWIDTH_4 (1 << 0)

#define MMCSD_BUSWIDTH_8 (1 << 1)

#define MMCSD_MUTBLKWRITE (1 << 2)

#define MMCSD_HOST_IS_SPI (1 <flags & MMCSD_HOST_IS_SPI)

#define MMCSD_SUP_SDIO_IRQ (1 << 4) /* support signal pending SDIO IRQs */

#define MMCSD_SUP_HIGHSPEED (1 << 5) /* support high speed */

rt_uint32_t max_seg_size; /* maximum size of one dma segment */

rt_uint32_t max_dma_segs; /* maximum number of dma segments in one request */

rt_uint32_t max_blk_size; /* maximum block size */

rt_uint32_t max_blk_count; /* maximum block count */

剩余16页未读,继续阅读

weixin_38615397

- 粉丝: 6

- 资源: 895

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 27页智慧街道信息化建设综合解决方案.pptx

- 计算机二级Ms-Office选择题汇总.doc

- 单链表的插入和删除实验报告 (2).docx

- 单链表的插入和删除实验报告.pdf

- 物联网智能终端项目设备管理方案.pdf

- 如何打造品牌的模式.doc

- 样式控制与页面布局.pdf

- 武汉理工Java实验报告(二).docx

- 2021线上新品消费趋势报告.pdf

- 第3章 Matlab中的矩阵及其运算.docx

- 基于Web的人力资源管理系统的必要性和可行性.doc

- 基于一阶倒立摆的matlab仿真实验.doc

- 速运公司物流管理模式研究教材

- 大数据与管理.pptx

- 单片机课程设计之步进电机.doc

- 大数据与数据挖掘.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0