没有合适的资源?快使用搜索试试~ 我知道了~

首页Micron_DDR4_Spec

资源详情

资源评论

资源推荐

DDR4 SDRAM

MT40A2G4

MT40A1G8

MT40A512M16

Features

•V

DD

= V

DDQ

= 1.2V ±60mV

•V

PP

= 2.5V, –125mV, +250mV

• On-die, internal, adjustable V

REFDQ

generation

• 1.2V pseudo open-drain I/O

•T

C

maximum up to 95°C

– 64ms, 8192-cycle refresh up to 85°C

– 32ms, 8192-cycle refresh at >85°C to 95°C

• 16 internal banks (x4, x8): 4 groups of 4 banks each

• 8 internal banks (x16): 2 groups of 4 banks each

•8n-bit prefetch architecture

• Programmable data strobe preambles

• Data strobe preamble training

• Command/Address latency (CAL)

• Multipurpose register READ and WRITE capability

• Write and read leveling

• Self refresh mode

• Low-power auto self refresh (LPASR)

• Temperature controlled refresh (TCR)

• Fine granularity refresh

• Self refresh abort

• Maximum power saving

• Output driver calibration

• Nominal, park, and dynamic on-die termination

(ODT)

• Data bus inversion (DBI) for data bus

• Command/Address (CA) parity

• Databus write cyclic redundancy check (CRC)

• Per-DRAM addressability

• Connectivity test (x16)

• JEDEC JESD-79-4 compliant

• sPPR and hPPR capability

Options

1

Marking

• Configuration

– 2 Gig x 4 2G4

– 1 Gig x 8 1G8

– 512 Meg x 16 512M16

• 78-ball FBGA package (Pb-free) – x4,

x8

– 9mm x 13.2mm – Rev. A PM

– 8mm x 12mm – Rev. B, D, G WE

– 7.5mm x 11mm – Rev. E, H SA

• 96-ball FBGA package (Pb-free) – x16

– 9mm x 14mm – Rev. A HA

– 8mm x 14mm – Rev. B JY

– 7.5mm x 13.5mm – Rev. D, E, H LY

• Timing – cycle time

– 0.625ns @ CL = 22 (DDR4-3200) -062E

– 0.682ns @ CL = 21 (DDR4-2933) -068

– 0.750ns @ CL = 19 (DDR4-2666) -075

– 0.750ns @ CL = 18 (DDR4-2666) -075E

– 0.833ns @ CL = 17 (DDR4-2400) -083

– 0.833ns @ CL = 16 (DDR4-2400) -083E

– 0.937ns @ CL = 15 (DDR4-2133) -093E

– 1.071ns @ CL = 13 (DDR4-1866) -107E

• Operating temperature

– Commercial (0° T

C

95°C) None

– Industrial (–40° T

C

95°C) IT

• Revision :A,

:B, :D, :G,

:E, :H

Note:

1. Not all options listed can be combined to

define an offered product. Use the part

catalog search on http://www.micron.com

for available offerings.

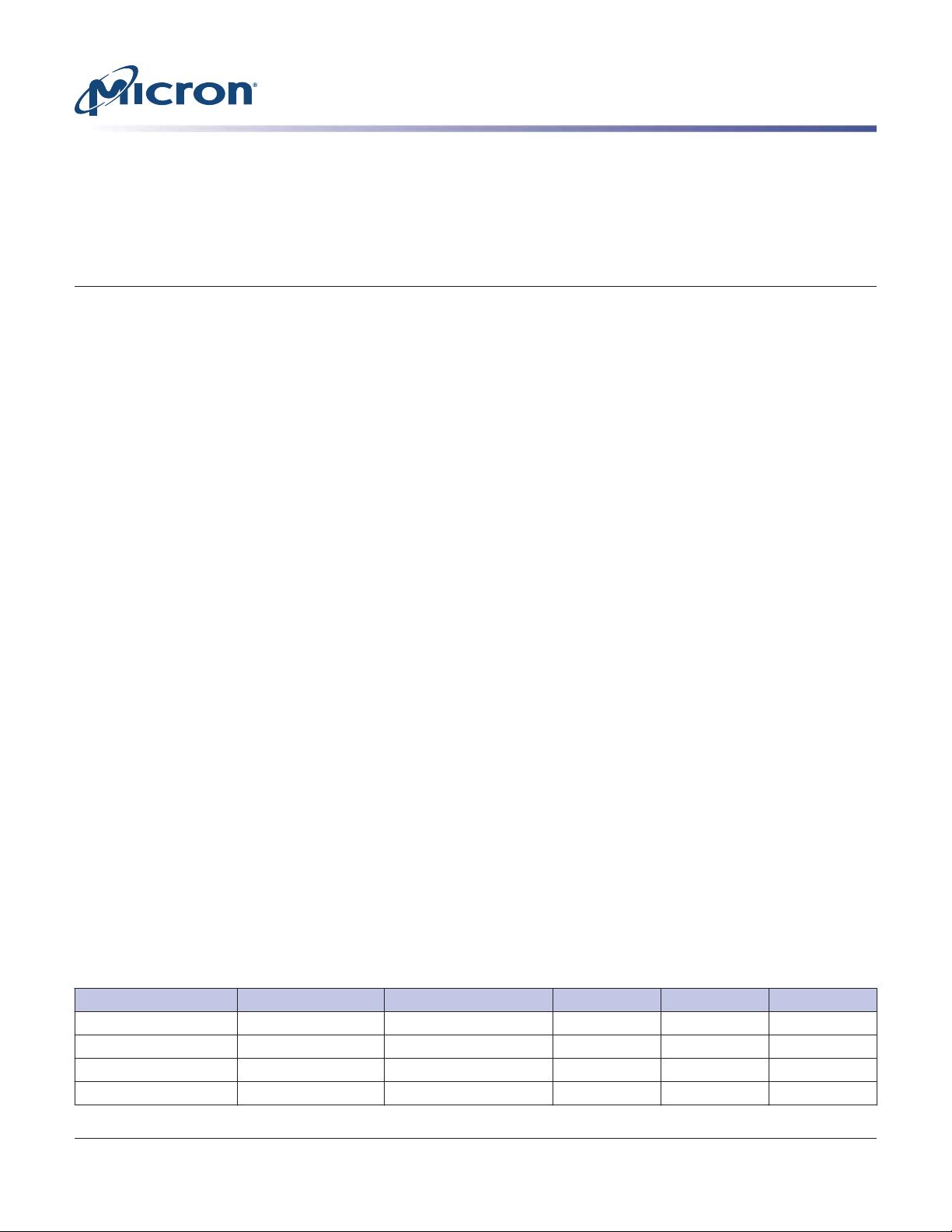

Table 1: Key Timing Parameters

Speed Grade Data Rate (MT/s) Target CL-

t

RCD-

t

RP CL (ns)

t

RCD (ns)

t

RP (ns)

-062E

6

3200 22-22-22 13.75 13.75 13.75

-068

5

2933 21-21-21 14.32 14.32 14.32

-075

4

2666 19-19-19 14.25 14.25 14.25

-075E

4

2666 18-18-18 13.50 13.50 13.50

8Gb: x4, x8, x16 DDR4 SDRAM

Features

CCMTD-1725822587-9875

8gb_ddr4_dram.pdf - Rev. M 10/17 EN

1

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2015 Micron Technology, Inc. All rights reserved.

Products and specifications discussed herein are subject to change by Micron without notice.

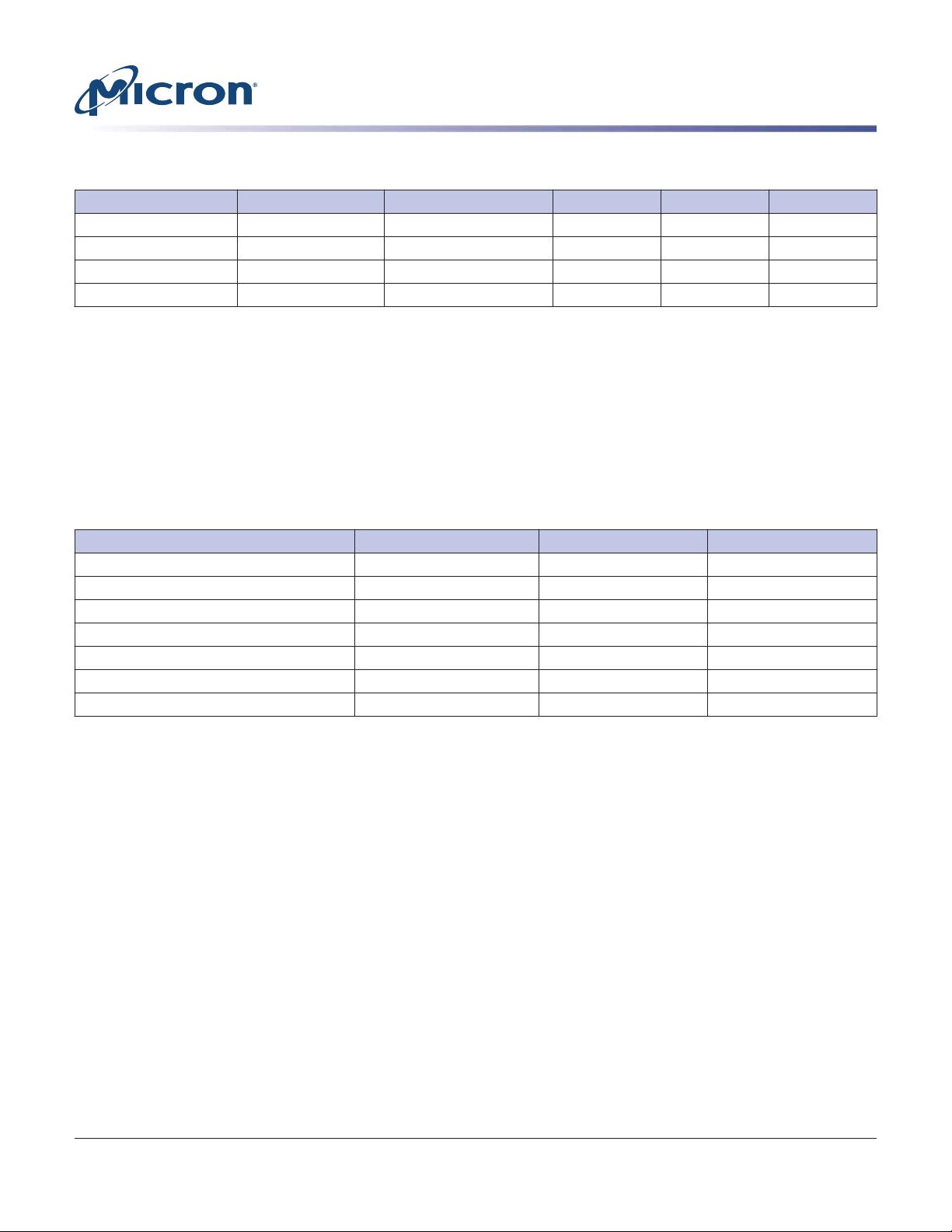

Table 1: Key Timing Parameters (Continued)

Speed Grade Data Rate (MT/s) Target CL-

t

RCD-

t

RP CL (ns)

t

RCD (ns)

t

RP (ns)

-083

3

2400 17-17-17 14.16 14.16 14.16

-083E

3

2400 16-16-16 13.32 13.32 13.32

-093E

2

2133 15-15-15 14.06 14.06 14.06

-107E

1

1866 13-13-13 13.92 13.92 13.92

Notes:

1. Backward compatible to 1600, CL = 11.

2. Backward compatible to 1600, CL = 11 and 1866, CL = 13.

3. Backward compatible to 1600, CL = 11; 1866, CL = 13; and 2133, CL = 15.

4. Backward compatible to 1600, CL = 11; 1866, CL = 13; 2133, CL = 15; and 2400, CL = 17.

5. Backward compatible to 1600, CL = 11; 1866, CL = 13; 2133, CL = 15; 2400, CL = 17; and 2666, CL = 19. Speed

offering may have restricted availability.

6. Backward compatible to 1600, CL = 11; 1866, CL = 13; 2133, CL = 15; 2400, CL = 17; 2666, CL = 19. Speed

offering may have restricted availability.

Table 2: Addressing

Parameter 2048 Meg x 4 1024 Meg x 8 512 Meg x 16

Number of bank groups 4 4 2

Bank group address BG[1:0] BG[1:0] BG0

Bank count per group 4 4 4

Bank address in bank group BA[1:0] BA[1:0] BA[1:0]

Row addressing 128K (A[16:0]) 64K (A[15:0]) 64K (A[15:0])

Column addressing 1K (A[9:0]) 1K (A[9:0]) 1K (A[9:0])

Page size

1

512B/1KB

2

1KB 2KB

Notes:

1. Page size is per bank, calculated as follows:

Page size = 2

COLBITS

× ORG/8, where COLBIT = the number of column address bits and ORG = the number of

DQ bits.

2. Die rev-dependent.

8Gb: x4, x8, x16 DDR4 SDRAM

Features

CCMTD-1725822587-9875

8gb_ddr4_dram.pdf - Rev. M 10/17 EN

2

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2015 Micron Technology, Inc. All rights reserved.

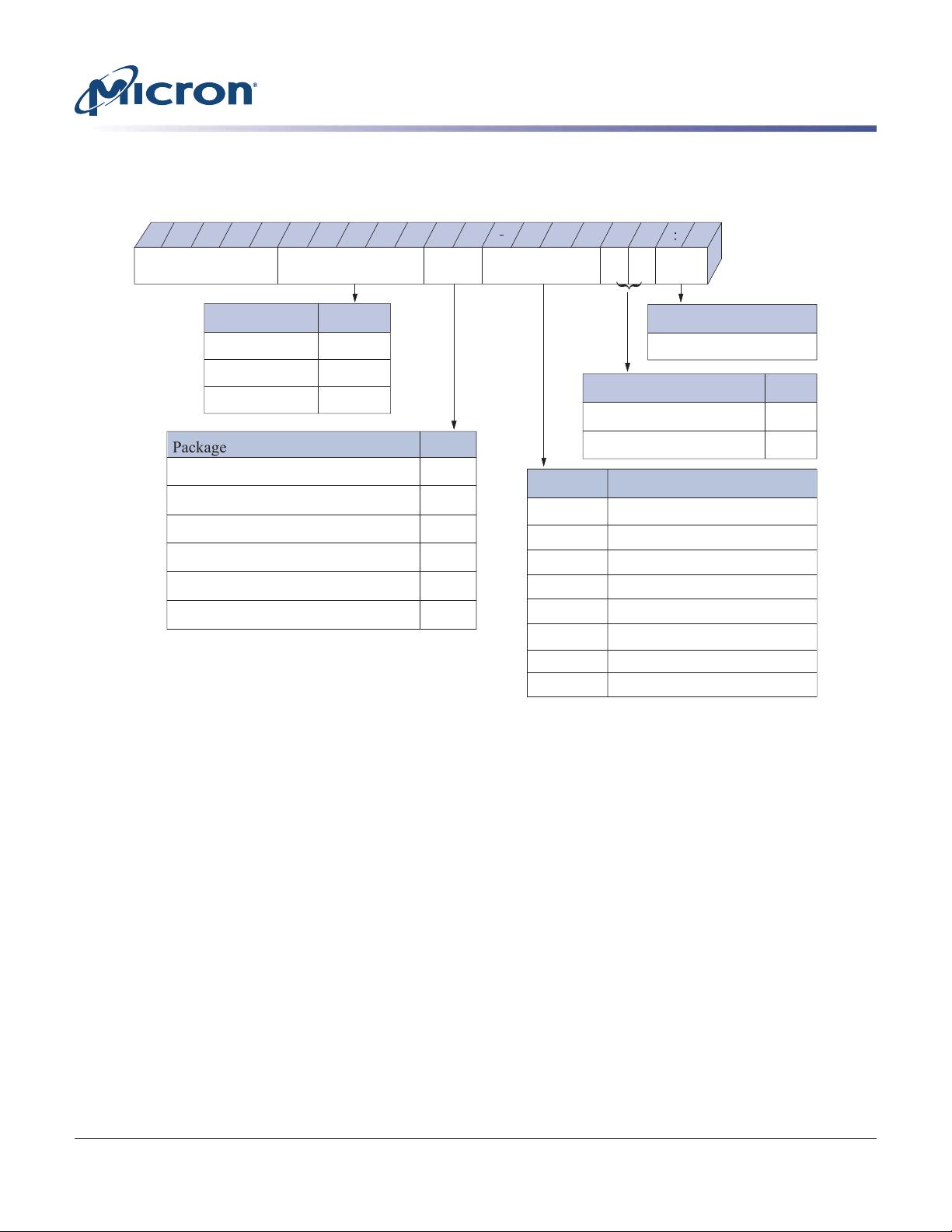

Figure 1: Order Part Number Example

3DFNDJH

Example Part Number: MT40A1G8WE-083:D

MT40A

Configuration

Package

Speed

Die Revision

Revision

:A, :B, :D, :G, :E, :H

Configuration

Case Temperature

Commercial

None

Industrual temperature

IT

2 Gig x 4 2G4

1 Gig x 8 1G8

512 Meg x 16 512M16

Mark

Speed

Grade

78-ball, 9.0mm x 13.2mm FBGA PM

78-ball, 8.0mm x 12.0mm FBGA WE

78-ball, 7.5mm x 11.0mm FBGA SA

96-ball, 9.0mm x 14.0mm FBGA HA

96-ball, 8.0mm x 14.0mm FBGA JY

96-ball, 7.5mm x 13.5mm FBGA LY

-107E CK = 1.071ns, CL = 13

-093E CK = 0.937ns, CL = 15

-083E CK = 0.833ns, CL = 16

-083 CK = 0.833ns, CL = 17

-075E CK = 0.750ns, CL = 18

-075 CK = 0.750ns, CL = 19

-068 CK = 0.682ns, CL = 21

-062E CK = 0.625ns, CL = 22

t

t

t

t

t

t

t

t

Cycle Time, CAS Latency

8Gb: x4, x8, x16 DDR4 SDRAM

Features

CCMTD-1725822587-9875

8gb_ddr4_dram.pdf - Rev. M 10/17 EN

3

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2015 Micron Technology, Inc. All rights reserved.

Contents

General Notes and Description ....................................................................................................................... 19

Description ................................................................................................................................................ 19

Industrial Temperature ............................................................................................................................... 19

General Notes ............................................................................................................................................ 19

Definitions of the Device-Pin Signal Level ................................................................................................... 20

Definitions of the Bus Signal Level ............................................................................................................... 20

Functional Block Diagrams ............................................................................................................................. 21

Ball Assignments ............................................................................................................................................ 23

Ball Descriptions ............................................................................................................................................ 25

Package Dimensions ....................................................................................................................................... 28

State Diagram ................................................................................................................................................ 34

Functional Description ................................................................................................................................... 36

RESET and Initialization Procedure ................................................................................................................. 37

Power-Up and Initialization Sequence ......................................................................................................... 37

RESET Initialization with Stable Power Sequence ......................................................................................... 40

Uncontrolled Power-Down Sequence .......................................................................................................... 41

Programming Mode Registers ......................................................................................................................... 42

Mode Register 0 .............................................................................................................................................. 45

Burst Length, Type, and Order ..................................................................................................................... 47

CAS Latency ............................................................................................................................................... 48

Test Mode .................................................................................................................................................. 48

Write Recovery(WR)/READ-to-PRECHARGE ............................................................................................... 48

DLL RESET ................................................................................................................................................. 48

Mode Register 1 .............................................................................................................................................. 49

DLL Enable/DLL Disable ............................................................................................................................ 50

Output Driver Impedance Control ............................................................................................................... 51

ODT R

TT(NOM)

Values .................................................................................................................................. 51

Additive Latency ......................................................................................................................................... 51

DQ RX EQ .................................................................................................................................................. 51

Write Leveling ............................................................................................................................................ 52

Output Disable ........................................................................................................................................... 52

Termination Data Strobe ............................................................................................................................. 52

Mode Register 2 .............................................................................................................................................. 53

CAS WRITE Latency .................................................................................................................................... 55

Low-Power Auto Self Refresh ....................................................................................................................... 55

Dynamic ODT ............................................................................................................................................ 55

Write Cyclic Redundancy Check Data Bus .................................................................................................... 55

Mode Register 3 .............................................................................................................................................. 56

Multipurpose Register ................................................................................................................................ 57

WRITE Command Latency When CRC/DM is Enabled ................................................................................. 58

Fine Granularity Refresh Mode .................................................................................................................... 58

Temperature Sensor Status ......................................................................................................................... 58

Per-DRAM Addressability ........................................................................................................................... 58

Gear-Down Mode ....................................................................................................................................... 58

Mode Register 4 .............................................................................................................................................. 59

Hard Post Package Repair Mode .................................................................................................................. 60

Soft Post Package Repair Mode .................................................................................................................... 61

WRITE Preamble ........................................................................................................................................ 61

READ Preamble .......................................................................................................................................... 61

READ Preamble Training ............................................................................................................................ 61

8Gb: x4, x8, x16 DDR4 SDRAM

Features

CCMTD-1725822587-9875

8gb_ddr4_dram.pdf - Rev. M 10/17 EN

4

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2015 Micron Technology, Inc. All rights reserved.

Temperature-Controlled Refresh ................................................................................................................. 61

Command Address Latency ........................................................................................................................ 61

Internal V

REF

Monitor ................................................................................................................................. 61

Maximum Power Savings Mode ................................................................................................................... 62

Mode Register 5 .............................................................................................................................................. 63

Data Bus Inversion ..................................................................................................................................... 64

Data Mask .................................................................................................................................................. 65

CA Parity Persistent Error Mode .................................................................................................................. 65

ODT Input Buffer for Power-Down .............................................................................................................. 65

CA Parity Error Status ................................................................................................................................. 65

CRC Error Status ......................................................................................................................................... 65

CA Parity Latency Mode .............................................................................................................................. 65

Mode Register 6 .............................................................................................................................................. 66

t

CCD_L Programming ................................................................................................................................. 67

V

REFDQ

Calibration Enable .......................................................................................................................... 67

V

REFDQ

Calibration Range ........................................................................................................................... 67

V

REFDQ

Calibration Value ............................................................................................................................ 68

DQ RX EQ .................................................................................................................................................. 68

Truth Tables ................................................................................................................................................... 69

NOP Command .............................................................................................................................................. 72

DESELECT Command .................................................................................................................................... 72

DLL-Off Mode ................................................................................................................................................ 72

DLL-On/Off Switching Procedures .................................................................................................................. 74

DLL Switch Sequence from DLL-On to DLL-Off ........................................................................................... 74

DLL-Off to DLL-On Procedure .................................................................................................................... 75

Input Clock Frequency Change ....................................................................................................................... 76

Write Leveling ................................................................................................................................................ 77

DRAM Setting for Write Leveling and DRAM TERMINATION Function in that Mode ..................................... 79

Procedure Description ................................................................................................................................ 80

Write Leveling Mode Exit ............................................................................................................................ 81

Command Address Latency ............................................................................................................................ 82

Low-Power Auto Self Refresh Mode ................................................................................................................. 87

Manual Self Refresh Mode .......................................................................................................................... 87

Multipurpose Register .................................................................................................................................... 89

MPR Reads ................................................................................................................................................. 90

MPR Readout Format ................................................................................................................................. 92

MPR Readout Serial Format ........................................................................................................................ 92

MPR Readout Parallel Format ..................................................................................................................... 93

MPR Readout Staggered Format .................................................................................................................. 94

MPR READ Waveforms ............................................................................................................................... 95

MPR Writes ................................................................................................................................................ 97

MPR WRITE Waveforms .............................................................................................................................. 98

MPR REFRESH Waveforms ......................................................................................................................... 99

Gear-Down Mode .......................................................................................................................................... 102

Maximum Power-Saving Mode ....................................................................................................................... 105

Maximum Power-Saving Mode Entry .......................................................................................................... 105

Maximum Power-Saving Mode Entry in PDA .............................................................................................. 106

CKE Transition During Maximum Power-Saving Mode ................................................................................ 106

Maximum Power-Saving Mode Exit ............................................................................................................ 106

Command/Address Parity .............................................................................................................................. 108

Per-DRAM Addressability .............................................................................................................................. 116

V

REFDQ

Calibration ........................................................................................................................................ 119

8Gb: x4, x8, x16 DDR4 SDRAM

Features

CCMTD-1725822587-9875

8gb_ddr4_dram.pdf - Rev. M 10/17 EN

5

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2015 Micron Technology, Inc. All rights reserved.

剩余381页未读,继续阅读

weixin_43758466

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

- MW全能培训汽轮机调节保安系统PPT教学课件.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论5