没有合适的资源?快使用搜索试试~ 我知道了~

首页Intel千兆网卡数据说明书

资源详情

资源评论

资源推荐

PCI/PCI-X Family of Gigabit Ethernet

Controllers Software Developer’s

Manual

82540EP/EM, 82541xx, 82544GC/EI, 82545GM/EM, 82546GB/EB, and

82547xx

317453006EN.PDF

Revision 4.0

ii Software Developer’s Manual

Legal Notice

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY

ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN

INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS

ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES

RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER

INTELLECTUAL PROPERTY RIGHT.

Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not

finalize a design with this information.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

This product has not been tested with every possible configuration/setting. Intel is not responsible for the product’s failure in any configuration/setting,

whether tested or untested.

The Intel product(s) discussed in this document may contain design defects or errors known as errata which may cause the product to deviate from

published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation

P.O. Box 5937

Denver, CO 80217-9808

or call in North America 1-800-548-4725, Europe 44-0-1793-431-155, France 44-0-1793-421-777, Germany 44-0-1793-421-333, other Countries 708-

296-9333.

Intel

®

is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

*Other names and brands may be claimed as the property of others.

Copyright © Intel Corporation, 2009

Software Developer’s Manual iii

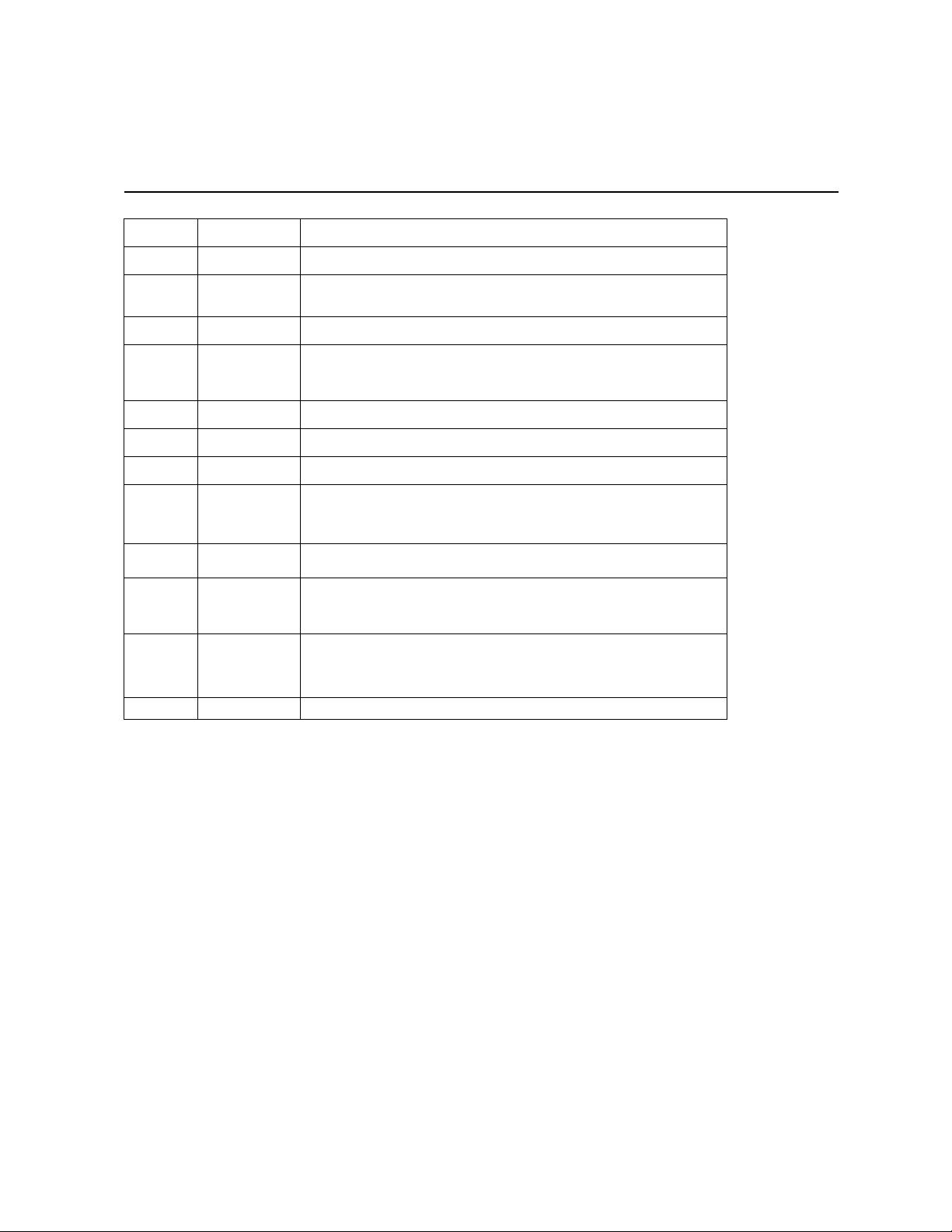

Revision History

Date Version Comments

Mar 2009 4.0

Updated Section 5 (added Table 5-15 “LED Configuration Defaults).

Oct 2008 3.9

Updated section 8.7.4 “Discard PAUSE Frames and Pass MAC Control

Frames”.

June 2008 3.8

Updated EEPROM Word 21h bit descriptions (section 5.6.18).

June 2008 3.7

Updated Sections 13.4.30 and 13.4.31 (added text stating to use the

Interrupt Throttling Register (ITR) instead of registers RDTR and RADV for

applications requiring an interrupt moderation mechanism).

Jan 2007 3.6

Added a note to sections 13.4.20 and 13.4.21 for the 82547Gi/EI.

Sept 2007 3.5

Updated section 13.4.16.

May 2007 3.4

Updated section 6.4.1. Changed acronym “WCR” to “WUC”.

Dec 2006 3.3

Updated Table 13-87. Changed bit 24 settings to:

0b = Cache line granularity.

1b = Descriptor granularity.

June 2006 3.2 Updated Table 13.47. Changed the default setting of reserved bit 3 from 0b

to 1b.

April 2006 3.1 Added bit definitions (bits 9:8) to PHY register PSCON (16d).

Updated Figure 3.2 (added Receive Queue artwork).

Changed 81541ER-C0 to 82541ER-CO in Table 5-1.

Nov 2005 3.0 Updated Device Control/Status, EEPROM Flash Control & Data, Extended

Device Control, and TCTL register bit assignments.

Updated PHY register 00d - 03d, 07d, 09d, 17d - 21d, and 23d bit assign-

ments.

July 2005 2.5 Initial Public Release.

iv Software Developer’s Manual

Note: This page is intentionally left blank.

Software Developer’s Manual v

Contents

Contents

1 Introduction..................................................................................................................1

1.1 Scope ....................................................................................................................1

1.2 Overview ...............................................................................................................1

1.3 Ethernet Controller Features.................................................................................2

1.3.1 PCI Features ........................................................................................2

1.3.2 CSA Features (82547GI/EI Only).........................................................2

1.3.3 Network Side Features.........................................................................2

1.3.4 Host Offloading Features .....................................................................3

1.3.5 Additional Performance Features.........................................................4

1.3.6 Manageability Features (Not Applicable to the 82544GC/EI or

82541ER)5

1.3.7 Additional Ethernet Controller Features ...............................................5

1.3.8 Technology Features............................................................................5

1.4 Conventions ..........................................................................................................6

1.4.1 Register and Bit References ................................................................6

1.4.2 Byte and Bit Designations ....................................................................6

1.5 Related Documents...............................................................................................6

1.6 Memory Alignment Terminology............................................................................6

2 Architectural Overview ............................................................................................7

2.1 Introduction............................................................................................................7

2.2 External Architecture.............................................................................................8

2.3 Microarchitecture.................................................................................................10

2.3.1 PCI/PCI-X Core Interface ...................................................................10

2.3.2 82547GI/EI CSA Interface..................................................................11

2.3.3 DMA Engine and Data FIFO ..............................................................11

2.3.4 10/100/1000 Mb/s Receive and Transmit MAC Blocks ......................12

2.3.5 MII/GMII/TBI/Internal SerDes Interface Block ....................................12

2.3.6 10/100/1000 Ethernet Transceiver (PHY) ..........................................13

2.3.7 EEPROM Interface.............................................................................13

2.3.8 FLASH Memory Interface...................................................................14

2.4 DMA Addressing .................................................................................................14

2.5 Ethernet Addressing............................................................................................15

2.6 Interrupts .............................................................................................................16

2.7 Hardware Acceleration Capability .......................................................................17

2.7.1 Checksum Offloading .........................................................................17

2.7.2 TCP Segmentation .............................................................................17

2.8 Buffer and Descriptor Structure...........................................................................17

3 Receive and Transmit Description....................................................................19

3.1 Introduction..........................................................................................................19

3.2 Packet Reception ................................................................................................19

3.2.1 Packet Address Filtering ....................................................................19

3.2.2 Receive Data Storage ........................................................................20

3.2.3 Receive Descriptor Format.................................................................20

3.2.4 Receive Descriptor Fetching ..............................................................25

剩余409页未读,继续阅读

emel

- 粉丝: 2

- 资源: 1

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

- MW全能培训汽轮机调节保安系统PPT教学课件.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0