基于基于APD的的2.5D封装中介层自动化设计封装中介层自动化设计

由于高带宽存储器(High Bandwidth Memory,HBM)的高带宽特性,在2.5D封装中介层(Interposer)的版图

设计过程中存在大量HBM接口的连线需要手动完成。介绍了如何使用SKILL语言在Allegro封装设计工具 (Allegro

Package Design,APD) 中实现HBM接口的自动布线,将原来的手动布线时间从2周缩短到10 min,大大压缩设

计周期。

0 引言引言

集成高带宽存储器(High Bandwidth Memory,HBM)的2.5D先进封装具有高带宽、高集成度和低成本的综合优势,开始广泛

应用于计算和网络市场。由于HBM的高带宽特性,在2.5D封装中介层(Interposer)设计中存在大量布线工作。并且由于HBM的

相对位置在不同的设计中存在差异,因此无法直接复制以前的布线设计。考虑到这些连接非常规则,可以通过软件编程的方式

实现自动化,以节省手动布线时间。

本文介绍如何使用SKILL语言在APD中实现HBM接口的自动布线。此方法的核心在于如何获取每个连线上的各点坐标,再

通过SKILL调用布线、打孔命令实现自动化布线工作。

1 2.5D先进封装简介先进封装简介

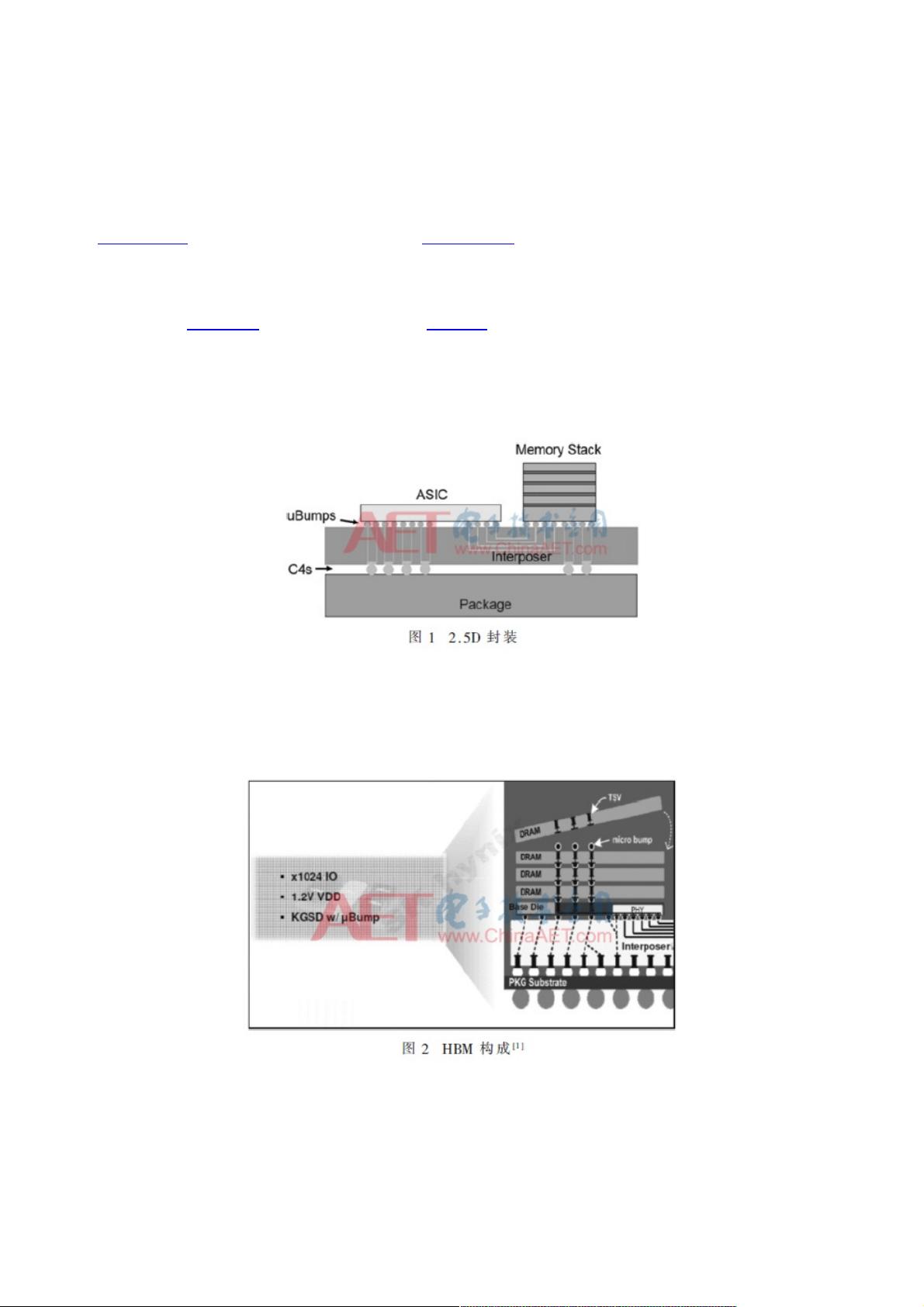

如图1所示,这里的2.5D封装相比普通2D封装主要多了Interposer和HBM。

Interposer主要用于连接专用集成电路(ASIC)和HBM,利用硅工艺实现小尺寸线宽和线间距的高密度布线设计。其他信

号通过硅通孔(TSV)技术从顶部芯片直接连接到底下的封装基板。

如图2所示,HBM是多个动态随机存取存储器(Dynamic Random Access Memory,DRAM)的堆叠,以实现高带宽和大容量

集成。第二代HBM, 每个IO速率达2 Gb/s,总共1 024个IO,即每个HBM具有2 Tb/s的带宽。

由于HBM的高带宽特性,在Interposer的版图设计过程中,ASIC的HBM接口有大量的网络连接(大于1 700),如图3所示。

这些网络除了连线,还要打地孔(VSS Via),加地隔离(VSS Shielding),占用大量的手工布线时间。

评论0