亚稳态

1.亚稳态发生的原因

在同步系统中,如果触发器的 setup time / hold time 不满足,就可能产生亚稳态,此时触

发器输出端 Q 在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里 Q 端

毛刺、振荡,是介于”0”、” 1”电平之间的一个状态,而不是等于数据输入端 D 的值。这段

之间成为决断时间(resolution time)。经过 resolution time 之后 Q 端将稳定到 0 或 1 上,

但是究竟是 0 还是 1,这是随机的,与输入没有必然的关系。亚稳态是触发器的一个固有

特性,正常采样也会有一个亚稳态时间。当建立保持时间满足时,在经历采样、亚稳态后

进入一个正确的状态。如果建立保持时间不满足,那么会有一个相当长的亚稳态时间,最

后随机进入一个固定态。对触发器而言,DFF 内部建立保持时间内数据不稳定就会发生亚

稳态。

2.亚稳态的危害

由于输出在稳定下来之前可能是毛刺、振荡、固定的某一电压值,因此亚稳态导致:

① 逻辑误判

② 输出 0~1 之间的中间电压值还会使下一级产生亚稳态(即导致亚稳态的传播)。

3.亚稳态的解决办法

Remove Duplicate Register

:选择

OFF

。

只要系统中有异步元件,亚稳态就是无法避免的,因此设计的电路首先要减少亚稳态导致

错误的发生,其次要使系统对产生的错误不敏感。

前者要同步化或 FIFO

、双口

RAM

(外部异步信号可用,内部异步信号也可用,数据接口

更好用

;

即

读出数据,并有缓冲器空满信号来管理数据的读写 ,

以免数据丢失)

来实现,而后者根据不同的设计应用有不同的处理办法。

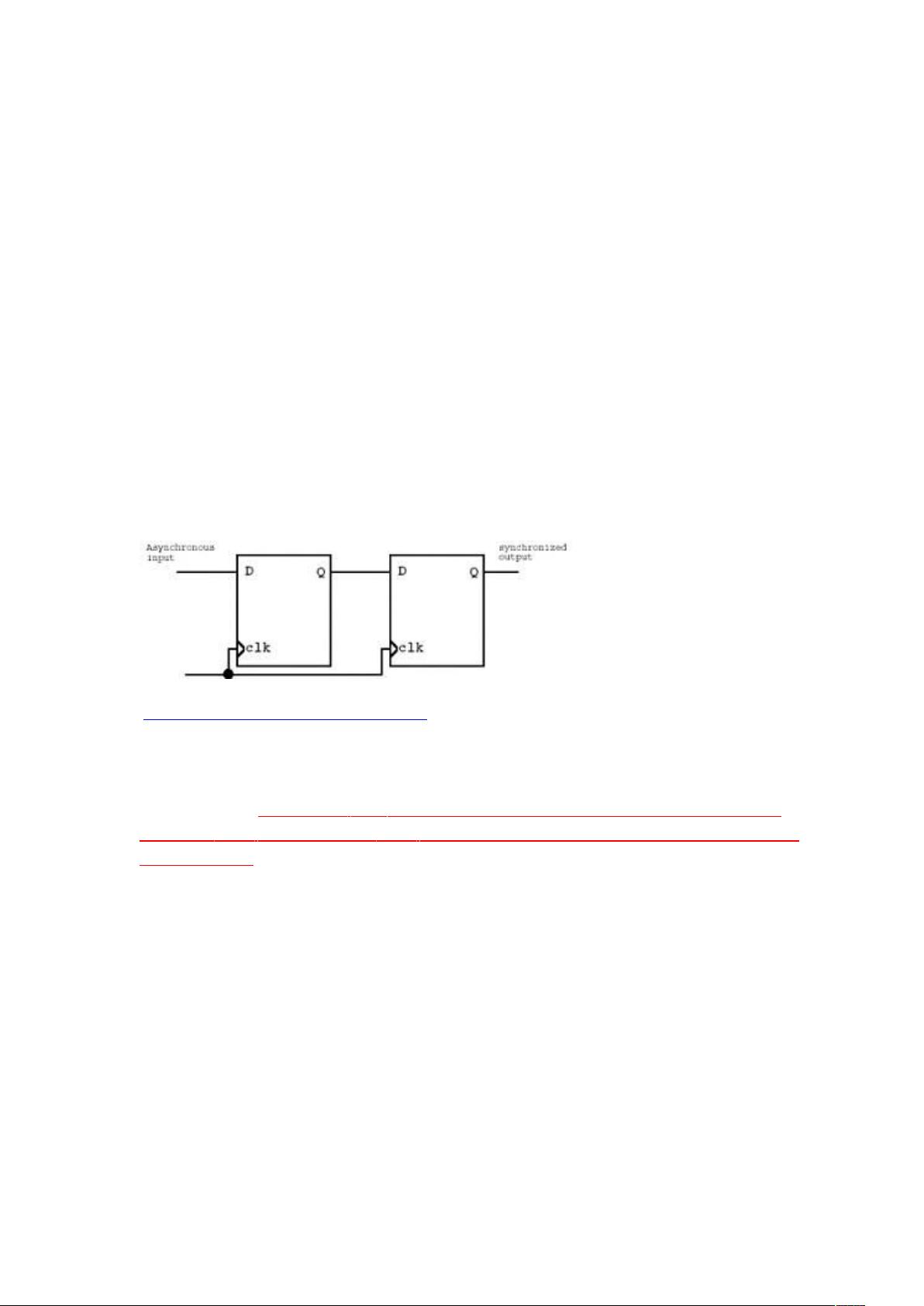

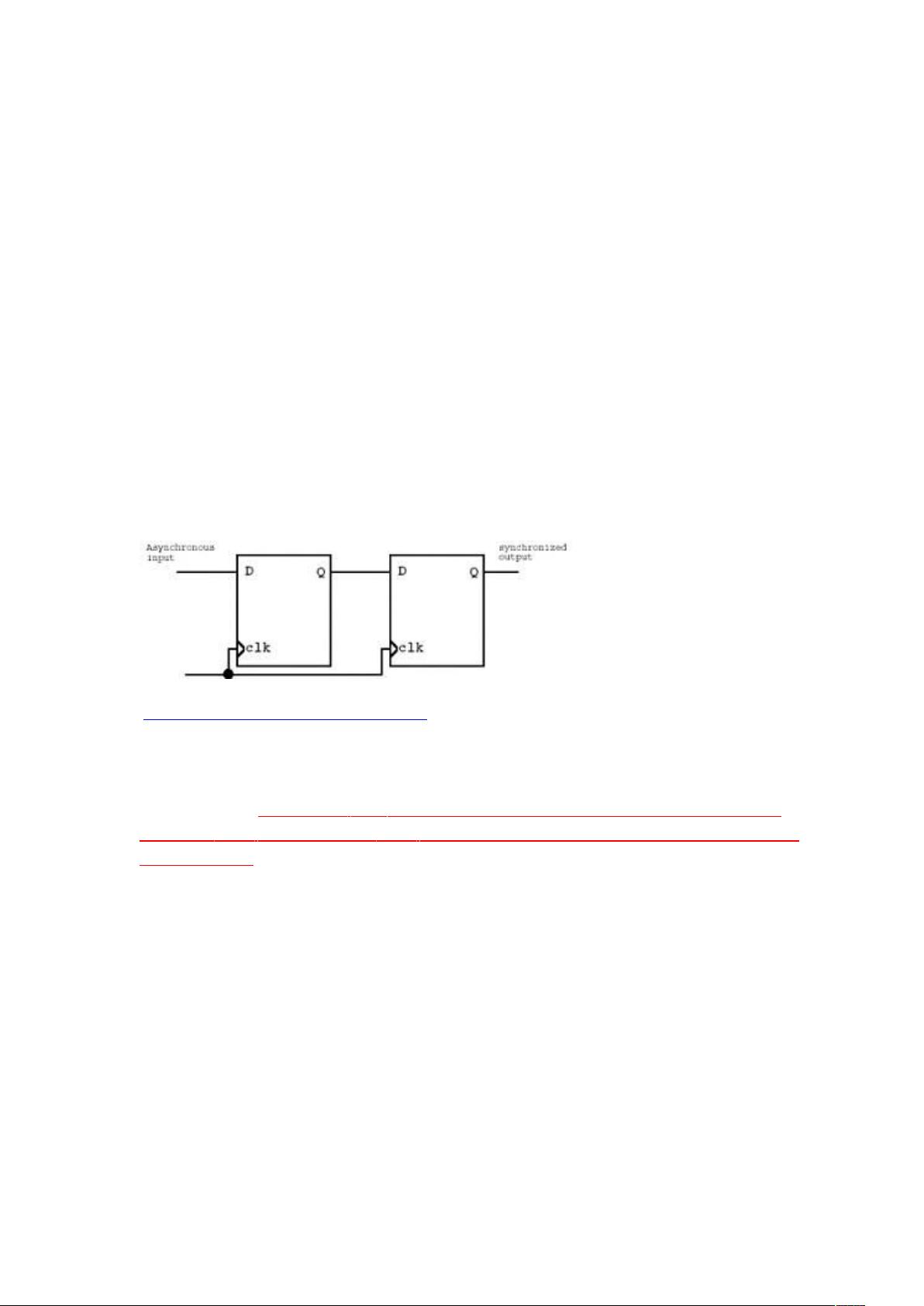

用两级触发器同步来减少亚稳态发生机会,输出基本不存在亚稳态。

其根本思想是异步信

号同步化。

其原理是即使触发器 D1 的输出端存在亚稳态,经过一个 CLK 周期后,触发器

D2 时钟沿到来时 D1 输出的亚稳态决断时间已过,稳定在 0 或 1,因此第二个触发器 Q 端

基本不会产生亚稳态,因此 CLK 频率越小亚稳态传播概率越小,同步化后异步信号会延

迟一个或 2 个 CLK 周期输出。(如异步输入由 0 到 1 的情况:第一个发生亚稳态,可能输

出 0 或 1,若输出 1,则正好;若输出 0,则也会在第二个时钟沿传到触发器 D2,若异步数

据 1 在第二个时钟沿消失则该数据采不到,若仍稳定,则第二个时钟沿会被触发器 D1 采到,

这时不会有亚稳态,在第三个时钟沿被 D2 采到,即会又延迟一个周期输出。)若采用三

级触发器,则 D2 采到亚稳态决断时间时,D2 也会输出亚稳态并最终也会稳定在 0 或 1,

传播亚稳态的概率更低。

评论1