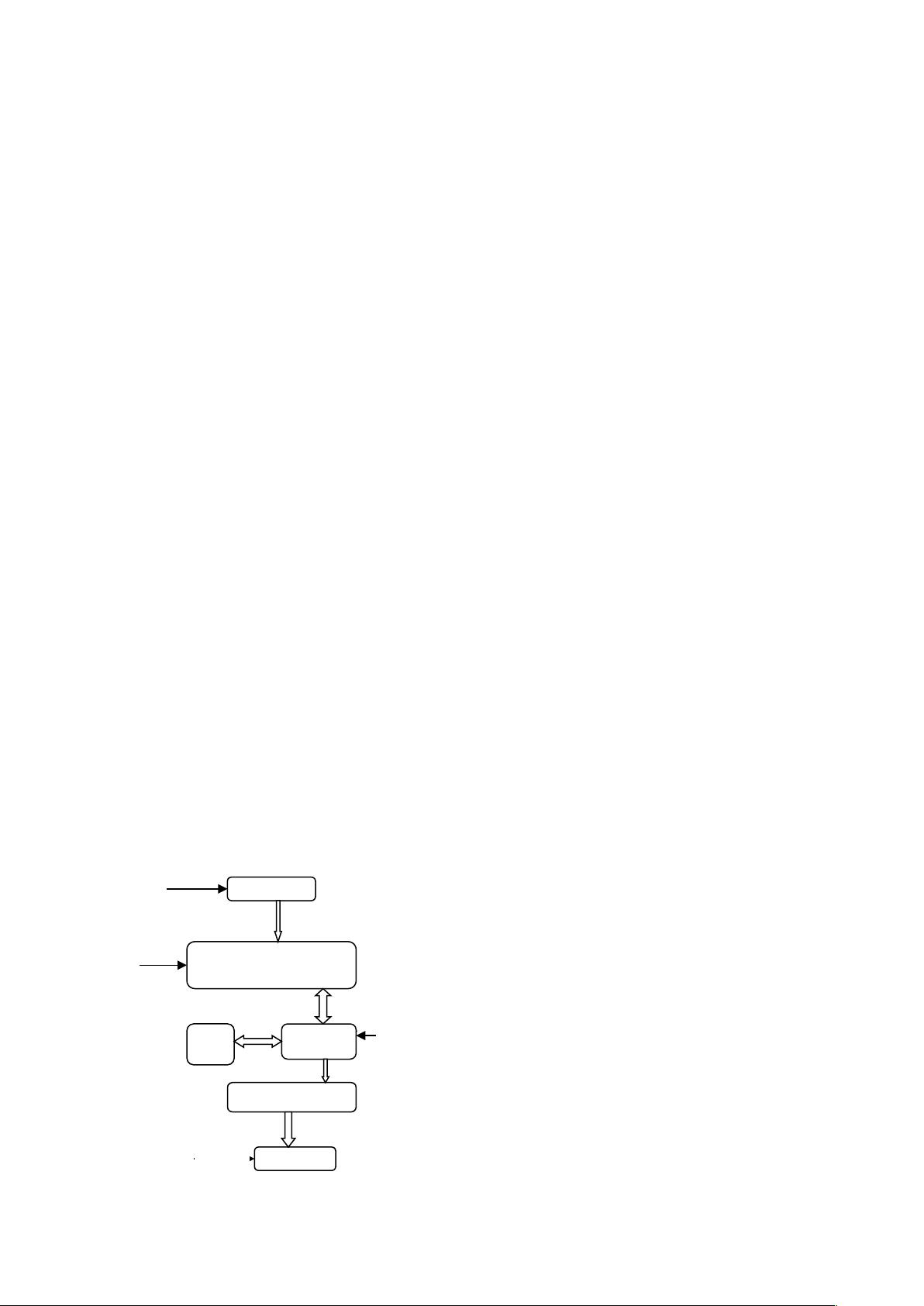

2.各模块详细设计

(1)计数器模块

本模块主要用于计数,包括开始计数、计数结束、计数暂停、计数输出等功能。

(2)分频模块

本模块主要用于时钟分频,分别将 FPGA 板子上的 50MHz 的频率转换为 1MHz 用于 RAM

存储器的输入和输出;将板子上的 50MHz 的频率转换为 1Hz 用以秒计时。

(3)RAM 模块

本模块主要用于将输入的预置值 1~10 存储于 RAM 的 10 个单元中每个单元 8bit。具体完成

读使能/写使能、输入数据端、输出数据端、内部读写控制端。

(4)显示模块

本模块主要用于显示输出的数据,用于辨别设计功能是否成功。一般采用七段数码管。

4.3 功能验证方案

1. 具体描述:

用一个 8×10 的单口 RAM 完成 10 个 8 位计数器,每个计数器的初值分别为 1-10,时

钟频率为 1MHz,将其进行 50 分频送入,每来一个时钟,计数器计一个数。第一个时钟

来时,第一个计数器计 1,此时,此计数器中的值变为 1,其余的计数器中的值不变,以

此类推,直到第 10 个时钟来时,第 10 个计数器计 1,计数器中的值 9 变为 0,以此类推,

完成 10 个 8 位计数器,得到计数器计数频率即为 1Hz。

2.验证描述

(1)计数器分频的验证:系统提供 50MHz 的标准频率 clk_in,验证 50 分频的实现,即

输出 1MHz 的频率 clk。当 clk 的上升沿 reset 的下降沿时,如果 reset=0,clk=0,否

则,clk 取反,实现了 clk_in 的 50 分频。

(2)RAM 功能的验证:定义一个 8x10 的双口 RAM,有两条地址线,读写各一个地址。

如果使信号 wr=1 且 rd=0 数据存入 RAM,如果使能信号 wr=0 且 rd=1RAM 将其中的

数据读出,从而实现了双口 RAM 的功能。

(3)数据写入与读出功能的验证:定义一个模块实现将 1—10 个数据写入 RAM,同时赋

予 RAM 地址值,每来一个时钟,RAM 就按地址递加的方式计数,并将计数器的值输出。

在时钟的上升沿 reset 的下降沿时,如果 reset=0,则地址 addr=0,计数器 cnt=0;否

则,如果使能信号 wr=1,地址 addr_in 递加,当 addr_in 大于 10 时,addr_in=0,计

数器 cnt=cnt+1 将 addr_in+cnt 送入数据输入 din.。