没有合适的资源?快使用搜索试试~ 我知道了~

首页GD5F1GQ4UAYIG.PDF

GD5F1GQ4UAYIG.PDF

GD5F1GQ4UAYIG SPI NAND FLASH 文档描述详细coder: 通过 CreateVideoDecoder 函数创建的视频解码器指针; nScaleDownRatio: 图像缩放比例因子。 返回值 0: 表示成功;-1: 失败

资源详情

资源评论

资源推荐

SPI(x1/x2/x4) NAND Flash GD5F1GQ4UAYIG

1

SPI (Serial Peripheral Interface) NAND Flash Memory

FEATURE

◆ 1G-bit Serial NAND Flash ◆ Program/Erase/Read Speed

-128M-byte -Page Program time: 400us typical

-2048 bytes page for read and program, spare 64bytes -Block Erase time: 3ms typical

-(128K + 4K)bytes per block for erase

-Page read time: 120us maximum(w/I ECC)

◆ Standard, Dual, Quad SPI ◆ Low Power Consumption

-Standard SPI: SCLK, CS#, SI, SO, WP#, HOLD# -40mA maximum active current

-Dual SPI: SCLK, CS#, SIO0, SIO1, WP#, HOLD# -70uA maximum standby current

-Quad SPI: SCLK, CS#, SIO0, SIO1, SIO2, SIO3

◆ High Speed Clock Frequency ◆ Enhanced access performance

-108MHz for fast read with 30PF load -2kbyte cache for fast random read

-Quad I/O Data transfer up to 480Mbits/s -Cache read and cache program

-2112/2048/64/16 wrap read option

◆ Software/Hardware Write Protection ◆ Advanced Feature for NAND

-Write protect all/portion of memory via software -Internal ECC option, per 512bytes

-Enable/Disable protection with WP# Pin -Internal data move by page with ECC

-Top or Bottom, Block selection combination -Promised golden block0

◆ Advanced security Features

-8K-Byte OTP Region

◆ Single Power Supply Voltage

-Full voltage range:2.7~3.6V

Note: please contact GigaDevice for details

GD Confidential

Preliminary

SPI(x1/x2/x4) NAND Flash GD5F1GQ4UAYIG

2

GENERAL DESCRIPTION

SPI (Serial Peripheral Interface) NAND Flash provides an ultra cost-effective while high density non-volatile memory

storage solution for embedded systems, based on an industry-standard NAND Flash memory core. It is an attractive

alternative to SPI-NOR and standard parallel NAND Flash, with advanced features:

• Total pin count is 8, including VCC and GND

• Density range from 256Mbit to 8Gbit

• Superior write performance and cost per bit over SPI-NOR

• Significant low cost than parallel NAND

This low-pin-count NAND Flash memory follows the industry-standard serial peripheral interface, and always

remains the same pinout from one density to another. The command sets resemble common SPI-NOR command sets,

modified to handle NAND specific functions and added new features. GigaDevice SPI NAND is an easy-to-integrate

NAND Flash memory, with specified designed features to ease host management:

• User-selectable internal ECC. ECC code is generated internally during a page program operation. When a page is

read to the cache register, the ECC code is detect and correct the errors when necessary. The 64-bytes spare area is

available even when internal ECC enabled. The device outputs corrected data and returns an ECC error status.

• Assistant Block Management. With corresponding options set, the device can prohibit the Bad Block from being

erased. This option features favor the block management convenience and enhance the performance.

• Internal data move or copy back with internal ECC. The device can be easily refreshed and manage garbage

collection task, without need of shift in and out of data.

• Power on Read with internal ECC. The device will automatically read first page of fist block to cache after power

on, then host can directly read data from cache for easy boot. Also the data is promised correctly by internal ECC.

It is programmed and read in page-based operations, and erased in block-based operations. Data is transferred to or

from the NAND Flash memory array, page by page, to a data register and a cache register. The cache register is closest to

I/O control circuits and acts as a data buffer for the I/O data; the data register is closest to the memory array and acts as a

data buffer for the NAND Flash memory array operation. The cache register functions as the buffer memory to enable

page and random data READ/WRITE and copy back operations. These devices also use a SPI status register that reports

the status of device operation.

CONNECTION DIAGRAM

CS#

SO

WP#

VSS

Top View

VCC

HOLD#

SCLK

SI

8–LEAD WSON

1

2

3

4 5

6

7

8

GD Confidential

Preliminary

SPI(x1/x2/x4) NAND Flash GD5F1GQ4UAYIG

3

PIN DESCRIPTION

Pin Name I/O Description

CS# I

Chip Select input, active low

SO/SIO1 I/O

Serial Data Output / Serial Data Input Output 1

WP#/SIO2 I/O

Write Protect, active low / Serial Data Input Output 2

VSS Ground

Ground

SI/SIO0 I/O

Serial Data Input / Serial Data Input Output 0

SCLK I

Serial Clock input

HOLD#/SIO3 I/O

Hold input, active low / Serial Data Input Output3

VCC Supply

Power Supply

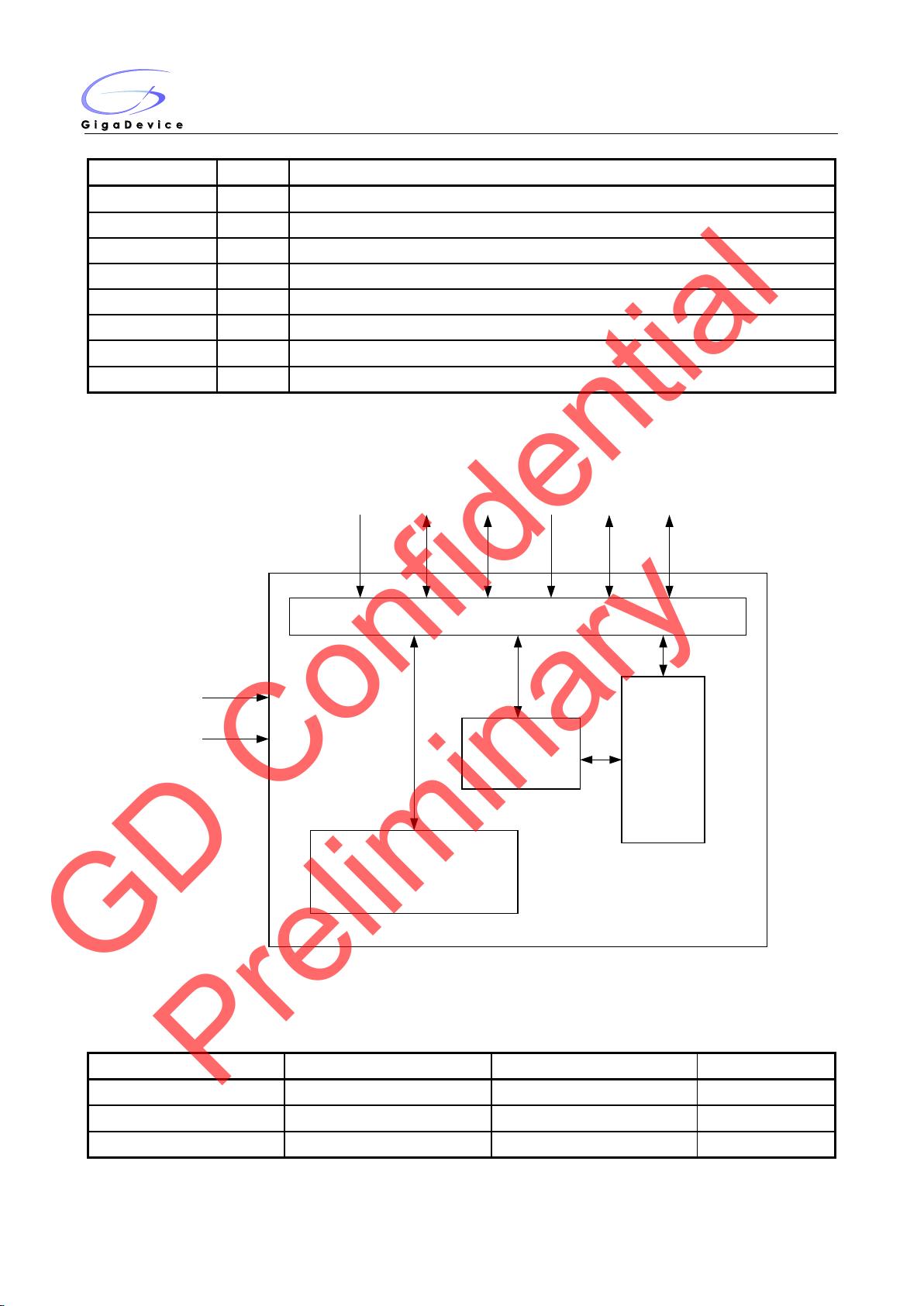

BLOCK DIAGRAM

Serial NAND controler

Cache

memory

NAND

memory

core

ECC and status register

Vcc

Vss

SCLK SI/SIO0 SO/SIO1 CS#

HOLD#/

SIO3

WP#/

SIO2

ARRAY ORGANIZATION

Each device has Each block has Each page has

128M+4M 128K+4K 2K+64 bytes

1024 x 64 64 - pages

1024 - - blocks

GD Confidential

Preliminary

SPI(x1/x2/x4) NAND Flash GD5F1GQ4UAYIG

4

Figure1. Array Organization

2048

64

2048 64

1 block

1 block = (2K + 64) bytes x 64 pages

= (128K + 4K) bytes

1 page = (2K + 64 bytes)

1 device = (128K + 4K) bytes x 1024 blocks

= 1Gb

Cache Register

Data Register

1024 Blocks

per device

SO

SI

MEMORY MAPPING

0

1

2

1023

0

1

63

0

1

2

2111

Blocks

RA<15:6>

Pages

RA<5:0>

Bytes

CA<11:0>

Note:

1. CA: Column Address. The 12-bit address is capable of addressing from 0 to 4095 bytes; however, only bytes 0 through

2111 are valid. Bytes 2112 through 4095 of each page are “out of bounds,” do not exist in the device, and cannot be

addressed.

2. RA: Row Address. RA<5:0> selects a page inside a block, and RA<15:6> selects a block.

GD Confidential

Preliminary

SPI(x1/x2/x4) NAND Flash GD5F1GQ4UAYIG

5

DEVICE OPERATION

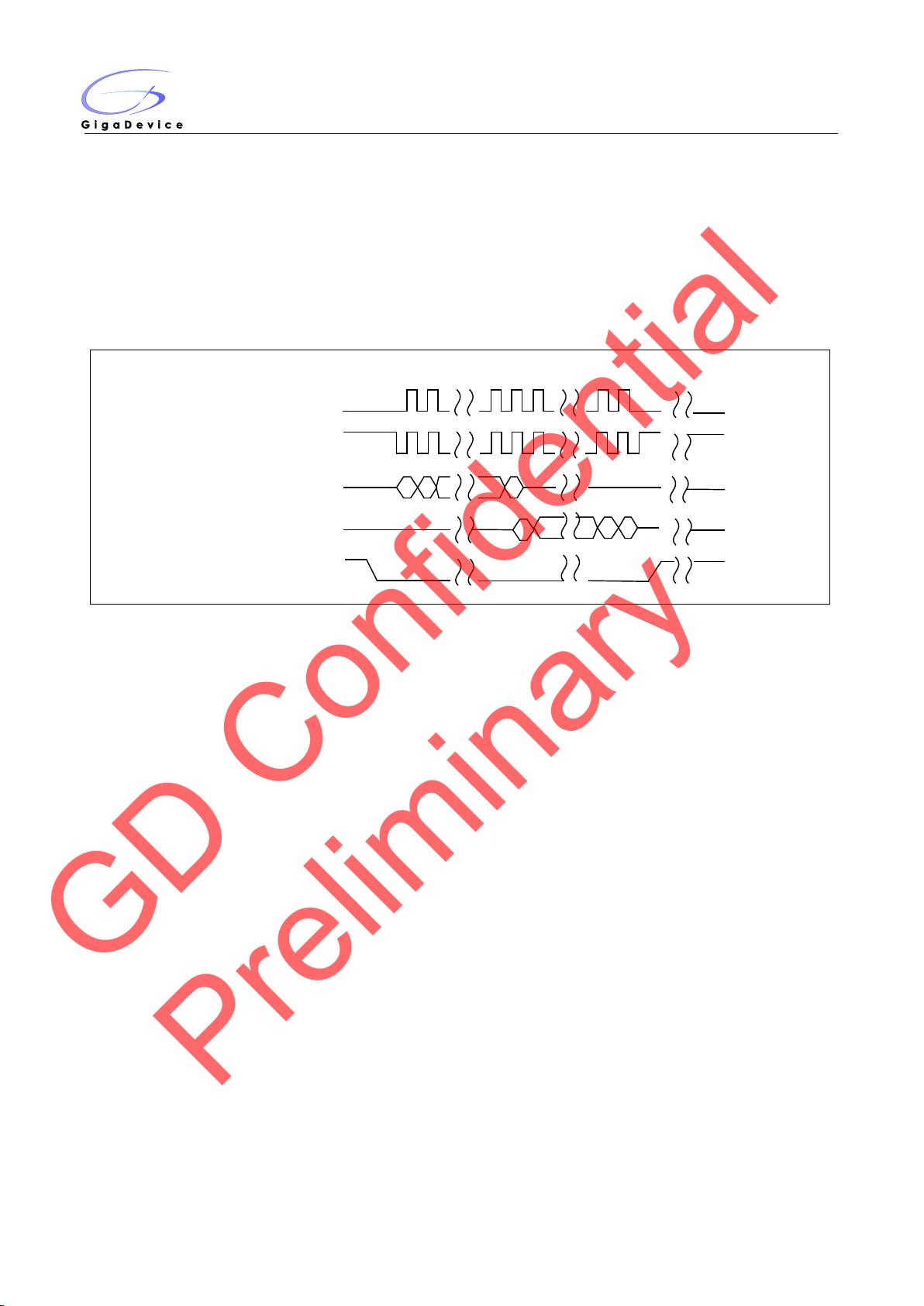

SPI Modes

SPI NAND supports two SPI modes:

• CPOL = 0, CPHA = 0 (Mode 0)

• CPOL = 1, CPHA = 1 (Mode 3)

Input data is latched on the rising edge of SCLK and data shifts out on the falling edge of SCLK for both modes. All

timing diagrams shown in this data sheet are mode 0. See figure2 for more details.

Figure2. SPI Modes Sequence Diagram

CS#

SCLK

SCLK

SI

SO

CPOL CPHA

00

11

MSB LSB

MSB LSB

Note: While CS# is HIGH, keep SCLK at VCC or GND (determined by mode 0 or mode 3). Do not toggle SCLK until CS# is driven

LOW.

Standard SPI

SPI NAND Flash features a standard serial peripheral interface on 4 signals bus: Serial Clock (SCLK), Chip Select

(CS#), Serial Data Input (SI) and Serial Data Output (SO).

Dual SPI

SPI NAND Flash supports Dual SPI operation when using the x2 and dual IO commands. These commands allow

data to be transferred to or from the device at two times the rate of the standard SPI. When using the Dual SPI command

the SI and SO pins become bidirectional I/O pins: SIO0 and SIO1.

Quad SPI

SPI NAND Flash supports Quad SPI operation when using the x4 and Quad IO commands. These commands allow

data to be transferred to or from the device at four times the rate of the standard SPI. When using the Quad SPI command

the SI and SO pins become bidirectional I/O pins: SIO0 and SIO1, and WP# and HOLD# pins become SIO2 and SIO3.

HOLD Mode

The HOLD# signal goes low to stop any serial communications with the device, but doesn’t stop the operation of

write status register, programming, or erasing in progress.

The operation of HOLD, need CS# keep low, and starts on falling edge of the HOLD# signal, with SCLK signal being

low (if SCLK is not being low, HOLD operation will not start until SCLK being low). The HOLD condition ends on rising

edge of HOLD# signal with SCLK being low (If SCLK is not being low, HOLD operation will not end until SCLK being low).

The SO is high impedance, both SI and SCLK don’t care during the HOLD operation, if CS# drives high during

HOLD operation, it will reset the internal logic of the device. To re-start communication with chip, the HOLD# must be at

high and then CS# must be at low.

GD Confidential

Preliminary

剩余31页未读,继续阅读

mirkerson

- 粉丝: 1399

- 资源: 5

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 27页智慧街道信息化建设综合解决方案.pptx

- 计算机二级Ms-Office选择题汇总.doc

- 单链表的插入和删除实验报告 (2).docx

- 单链表的插入和删除实验报告.pdf

- 物联网智能终端项目设备管理方案.pdf

- 如何打造品牌的模式.doc

- 样式控制与页面布局.pdf

- 武汉理工Java实验报告(二).docx

- 2021线上新品消费趋势报告.pdf

- 第3章 Matlab中的矩阵及其运算.docx

- 基于Web的人力资源管理系统的必要性和可行性.doc

- 基于一阶倒立摆的matlab仿真实验.doc

- 速运公司物流管理模式研究教材

- 大数据与管理.pptx

- 单片机课程设计之步进电机.doc

- 大数据与数据挖掘.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论2