实验五 半整数分频器的设计

一、 实验目的:

掌握半整数分频器的 VHDL 设计原理与方法。

掌握在 MAXPLUSⅡ 中进行简单数字系统设计的全过程。

二、实验的软硬件要求:

EDA2000 实验箱 2、主芯片:EP1KOTC100-3 3、计算机与 MAXPLUSⅡ 软件

三、 实验原理:

在数字系统设计中,分频器是一种基本电路。分频器的实现非常简单,可采用标准的

计数器,也可采用可编程逻辑器件来实现一个整数分频器。分频器通常用来对某个给定频

率进行分频,得到所需的频率。在某些场合下,用户所需要的频率与频率时钟源不是整数

倍关系,此时可采用小数分频器进行分频。

1 小数分频的基本原理

设有一个 5 MHz 的时钟源,但电路中需要产生一个 2 MHz 的时钟信号,由于分频比

为 2.5,因此整数分频器将不能胜任。

采用可编程逻辑器件实现分频系数为 2.5 的分频器,可采用以下方法:设计一个模 3

的计数器,再设计一个扣除脉冲电路,加在模 3 计数器输出之后,每来两个脉冲就扣除一

个脉冲(实际上是使被扣除的脉冲变成很窄的脉冲,可由异或门实现),就可以得到分频系

数为 2.5 的小数分频器。采用类似方法,可以设计分频系数为任意半整数的分频器。

小数分频的基本原理为脉冲吞吐计数法:设计两个不同分频比的整数分频器,通过控

制单位时间内两种分频比出现的不同次数,从而获得所需的小数分频值。例如设计一个分

频系数为 10.1 的分频器,可以将分频器设计成 9 次 10 分频,1 次 11 分频,这样总的分

频值为

(9×10+1×11)/(9+1) =10.1

从这种实现方法的特点可以看出,由于分频器的分频值在不断改变,因此分频后得到

的信号抖动较大。

当分频系数为 N-0.5(N 为整数)时,可控制扣除脉冲的时间,使输出为一个稳定的脉冲

频率,而不是一次 N 分频,一次 N-1 分频。

1.2 电路组成

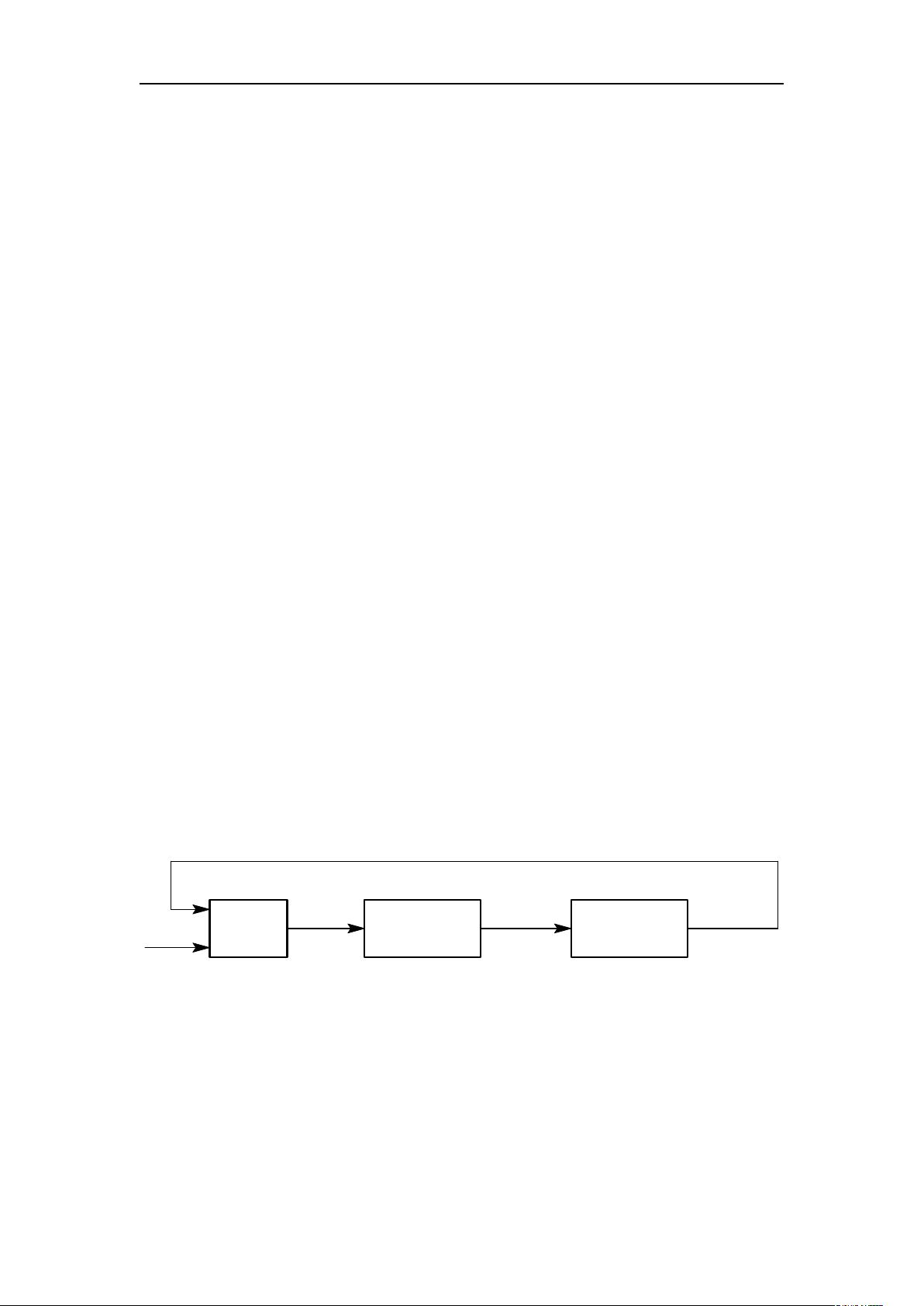

设需要设计一个分频系数为 N-0.5 的分频器,其电路可由一个模 N 计数器、一个二分

频器和一个异或门组成,如图 1 所示。在实现时,模 N 计数器可设计成带预置的计数器,

这样就可以实现任意分频系数为 N-0.5 的分频器。

图 1 通用半整数分频器

四、实验步骤

(一)、设计输入

1.图形输入方式(略)

2.文本输入方式(VHDL 或 Verilog HDL 语言等)

现以 VHDL 语言为例说明在 MAX+plusⅡ 系统下进行文本输入的方法。(3-8 译码

器)

① 创 建 VHDL 设 计 工 程 ② 编 辑 VHDL 源 程 序 文 件 (2) 将 设 计 项 目 设 置 成 工 程 文 件

实验五 半整数分频器的设计- 1 -

评论0