没有合适的资源?快使用搜索试试~ 我知道了~

首页zynq-7000 pcb

zynq-7000 pcb

Zynq-7000 All Programmable SoC PCB Design Guide

资源详情

资源评论

资源推荐

Zynq-7000

All Programmable SoC

PCB Design Guide

UG933 (v1.7.1) August 5, 2014

Zynq-7000 PCB Design Guide www.xilinx.com 2

UG933 (v1.7.1) August 5, 2014

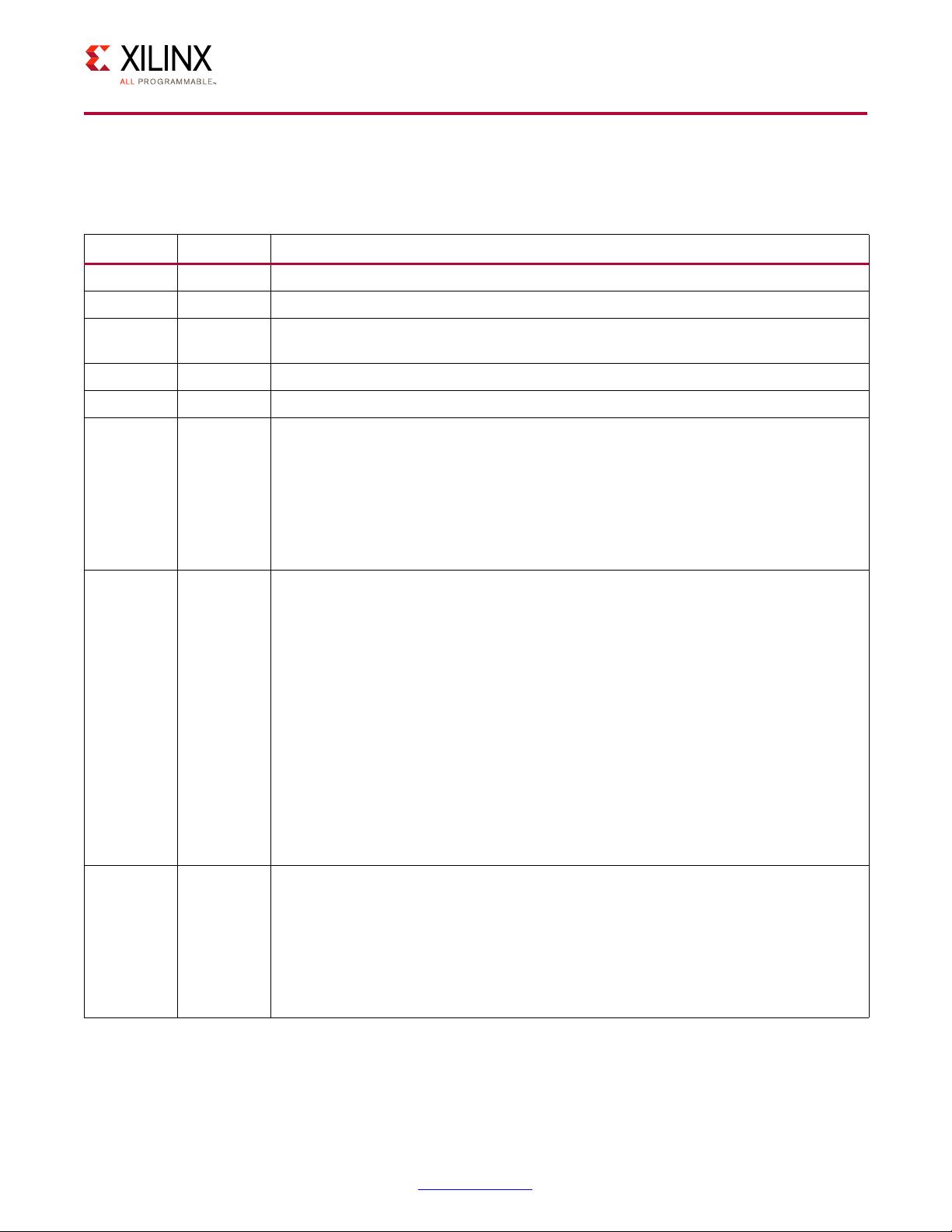

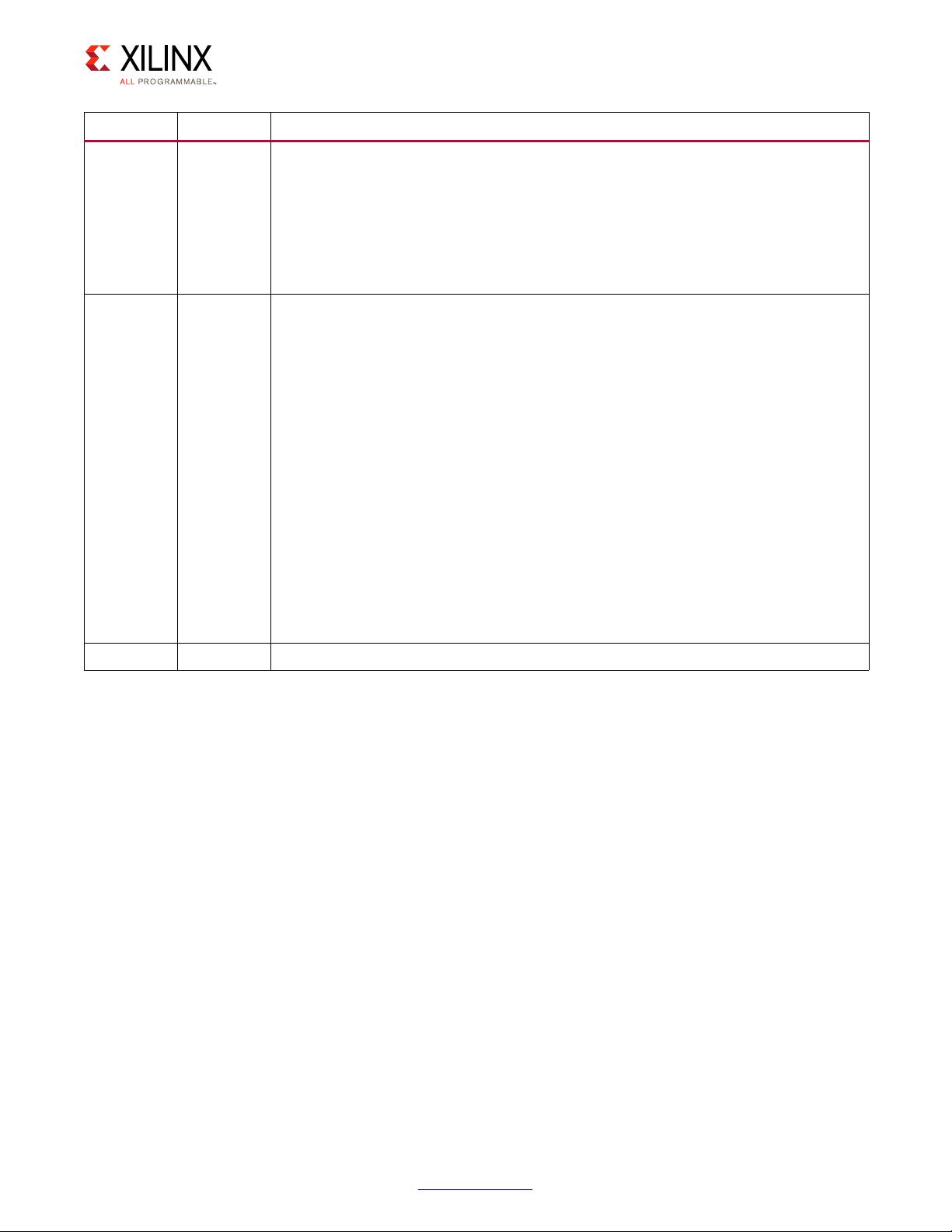

Revision History

The following table shows the revision history for this document.

Date Version Revision

06/04/2012 1.0

Initial Xilinx release.

06/06/2012 1.1

Corrected format issue.

08/29/2012 1.2

Updated Table 3-1 and Table 3-2 for additional devices/packages. Added 680 µF

capacitor specification to Table 3-3.

10/11/2012 1.2.1

Corrected document number (changed UG993 to UG933).

11/05/2012 1.2.2

Corrected sizing problem in PDF (no content change).

02/12/2013 1.3

Added Note

(2)

to Tab le 3-2. Added suggested part numbers to Table 3-3. Modified

paragraph under V

CCPAUX

– PS Auxiliary Logic Supply. Modified paragraph under

V

CCPLL

– PS PLL Supply. Added Figure 5-3. Modified second to last sentence and

added last sentence under PS_DDR_VREF0, PS_DDR_VREF1 – PS DDR Reference

Voltage. Modified CAUTION! under Configuring the V

CCO_MIO0

, V

CCO_MIO1

Voltage

Mode and Note under DDR Supply Voltages. Changed Cke connection from a

pull-down resistor to a pull-up resistor in Figure 5-5 through Figure 5-7. Updated

entire MIO/EMIO IP Layout Guidelines section.

04/01/2013 1.4

Added XC7Z100 devices to Table 3-1 and Tab le 3-2. Updated ESR range values in

Tabl e 3-3. Changed “0805 Ceramic Capacitor” section heading to Mid and High

Frequency Capacitors and modified first paragraph. Removed dimensions, changed

“0805” to “0402” in Figure 3-1 and deleted “0402 Ceramic Capacitor” subsection.

Deleted last sentence under , Modes and Attributes. Changed “minimum” to

“maximum” in third sentence of second paragraph under V

CCPLL

– PS PLL Supply.

Added second to last sentence under PS_DDR_VREF0, PS_DDR_VREF1 – PS DDR

Reference Voltage. Changed “Rup” to “Rterm” in Figure 5-5 and Figure 5-6. Deleted

Drst_b from Figure 5-6 and Figure 5-7. Changed Rup pull-up resistor to Rdown

pull-down resistor in Figure 5-7. Changed LPDDR2 setting in last row of Tabl e 5- 6 to

N/A. Updated values in first row of Tabl e 5-9. Changed “Three” different topologies

to “two” under DDR Routing Topology. Removed Fly-by topology from Figure 5-8 and

Tabl e 5-12. Deleted “NAND (ONFI),” “NOR/Flash/SRAM,” “SPI Master,” “SWDT (System

Watch Dog Timer),” and “TTC (Triple Time Counter” subsections from MIO/EMIO IP

Layout Guidelines and modified remaining subsections. Changed “EN208” to “EN247”

and “DS821” to “PG054” under Additional Resources and Legal Notices in Appendix A.

09/26/2013 1.5

Added XC7Z010, XC7Z015, and XC7Z030 packages/devices to Table 3-1 and Tabl e 3-2.

Changed suggested part number for the 4.7 µF capacitor in Tab le 3-3. Added DDR ECC

unused pins to Tab le 5-5. Modified Figure 5-6 (Cke pins are now applied to GND via

resistor Rdown instead of VTT via Rterm). Expanded first paragraph under DDR

Termination. Clarified DDR Termination paragraph. Added fly-by routing to DDR

Routing Topology section. Deleted SD/SDIO Peripheral Controller section. Added last

sentence under sections IIC and SDIO and second sentence under QSPI. Added

Chapter 6, Migration from XC7Z030-SBG485 to XC7Z015-CLG485 Devices.

Zynq-7000 PCB Design Guide www.xilinx.com 3

UG933 (v1.7.1) August 5, 2014

12/04/2013 1.6

Changed “DDR3” to “DDR3/3L” throughout document. Updated capacitor quantities

and packages in Tab le 3- 1 and Ta ble 3-2 . Updated capacitor specifications in

Tabl e 3-3. Updated descriptions for V

CCPINT

– PS Internal Logic Supply and V

CCPAUX

–

PS Auxiliary Logic Supply. Deleted “Capacitor Consolidation Rules” section. Modified

next-to-last sentence under PS_DDR_VREF0, PS_DDR_VREF1 – PS DDR Reference

Voltage. Added paragraph preceding Ta bl e 5-5 and updated Table 5- 5. Updated Addr,

Command, Contrl output name in Figure 5-7. Deleted last sentence under DDR Trace

Length.

08/01/2014 1.7

Removed “and Pin Planning Guide” from title. Added recommendation to

Recommended PCB Capacitors per Device. Changed V

CCO

per Bank sub-heading from

“100 µF” to 47 µF” in Table 3-1 . Added note 6 to Table 3-1. Removed values for V

CCPLL

and replaced with reference (Note 3) in Table 3-2. Changed “Terminal” type to

“Terminal Tantalum” and added “X7U” to 100 µF capacitor in Table 3-3 . Modified first

paragraph under Noise Limits by removing specifications and adding a reference to

the data sheet. Updated second paragraph under Unconnected V

CCO

Pins. Changed

Murata part number from “GRM155R60J475ME47D” to “GRM155R60J474KE19” under

Unconnected V

CCO

Pins. Updated first paragraph under PS_DDR_VRN, PS_DDR_VRP –

PS DDR Termination Voltage. Updated Unused DDR Memory. Deleted last two

sentences under PS_POR_B – Power on Reset and last sentence under PS_SRST_B –

External System Reset. Changed “Boot Mode Pins” section (pins MIO[2] to MIO[8] to

Boot Mode Pin MIO[8]. Modified Figure 5-5 (CKE resistor layout). Modified Figure 5-6

(changed clk signal to differential signals CLK_P/CLK_N and added pull-down resistor

to ODT). Added separate column for DDR3L to Table 5-6 and modified values.

Clarified DDR Trace Length and DDR Trace Impedance sections. Clarified byte

swapping under DDR Routing Topology. Added last paragraph under Ethernet GEM.

Deleted “Lower Operating Frequencies (without Feedback Mode)” section from

Chapter 6.

08/05/2014 1.7.1

Updated document to latest user guide template.

Date Version Revision

Zynq-7000 PCB Design Guide www.xilinx.com 4

UG933 (v1.7.1) August 5, 2014

Table of Contents

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Chapter 1: Introduction

About This Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Additional Support Resources. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Chapter 2: PCB Technology Basics

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

PCB Structures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Transmission Lines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Return Currents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Chapter 3: Power Distribution System

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

PCB Decoupling Capacitors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Basic PDS Principles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Simulation Methods . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

PDS Measurements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Troubleshooting. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Chapter 4: SelectIO Signaling

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Interface Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Single-Ended Signaling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Chapter 5: Processing System (PS) Power and Signaling

Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

PS Clock and Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Boot Mode Pin MIO[8] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Dynamic Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

MIO/EMIO IP Layout Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Zynq-7000 PCB Design Guide www.xilinx.com 5

UG933 (v1.7.1) August 5, 2014

Chapter 6: Migration from XC7Z030-SBG485 to XC7Z015-CLG485 Devices

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Differences between XC7Z030-SBG485 and XC7Z015-CLG485 Devices . . . . . . . . . . . . . . . . . . . . . . 69

Appendix A: Additional Resources and Legal Notices

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Solution Centers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Please Read: Important Legal Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

剩余76页未读,继续阅读

ryangcholung

- 粉丝: 2

- 资源: 29

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 面 向 对 象 课 程 设 计(很详细)

- 复杂可编程逻辑器件ppt课件.ppt

- 2021.12-2021居住客群消费趋势年报-贝壳-20页.pdf

- (完整word版)基于单片机的智能交通灯控制系统设计.doc

- 四川天羚绒业公司电子商务营销策略研究.docx

- TI-DS125BR111.pdf

- Oracle培训基础1.ppt

- SAP-Warehouse-Insights-中文介绍

- sed&awk;手册

- MATLAB6.0数学手册精简版

- 年数据库技术大会万振龙数据治理与大数据平台设计40.pptx

- 计算机组装维修教程11

- 全国统一数据资产登记体系建设白皮书.pdf

- 北邮概率论与随机过程课件 教学内容: 1、事件的独立性; 2、伯努利试验概型。

- 电子商务与民航信息化(PPT).ppt

- SAP等公司的面试题

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论2