简介

8255 是 Intel 公司生产的可编程并行 I/O 接口芯片,有 3 个 8 位并行 I/O 口。具有 3

个通道 3 种工作方式的可编程并行接口芯片(40 引脚)。 其各口功能可由软件

选择,

使 用 灵 活 , 通 用 性 强 。 8255 可 作 为 单 片 机 与 多 种 外 设 连 接 时 的 中 间 接 口 电 路 。

8255 作为主机与外设的连接芯片,必须提供与主机相连的 3 个总线接口,即数据线、

地址线、控制线接口。同时必须具有与外设连接的接口 A、B、C 口。由于 8255 可编

程,所以必须具有逻辑控制部分,因而 8255 内部结构分为 3 个部分:与 CPU 连接部分、

与外设连接部分、控制部分。

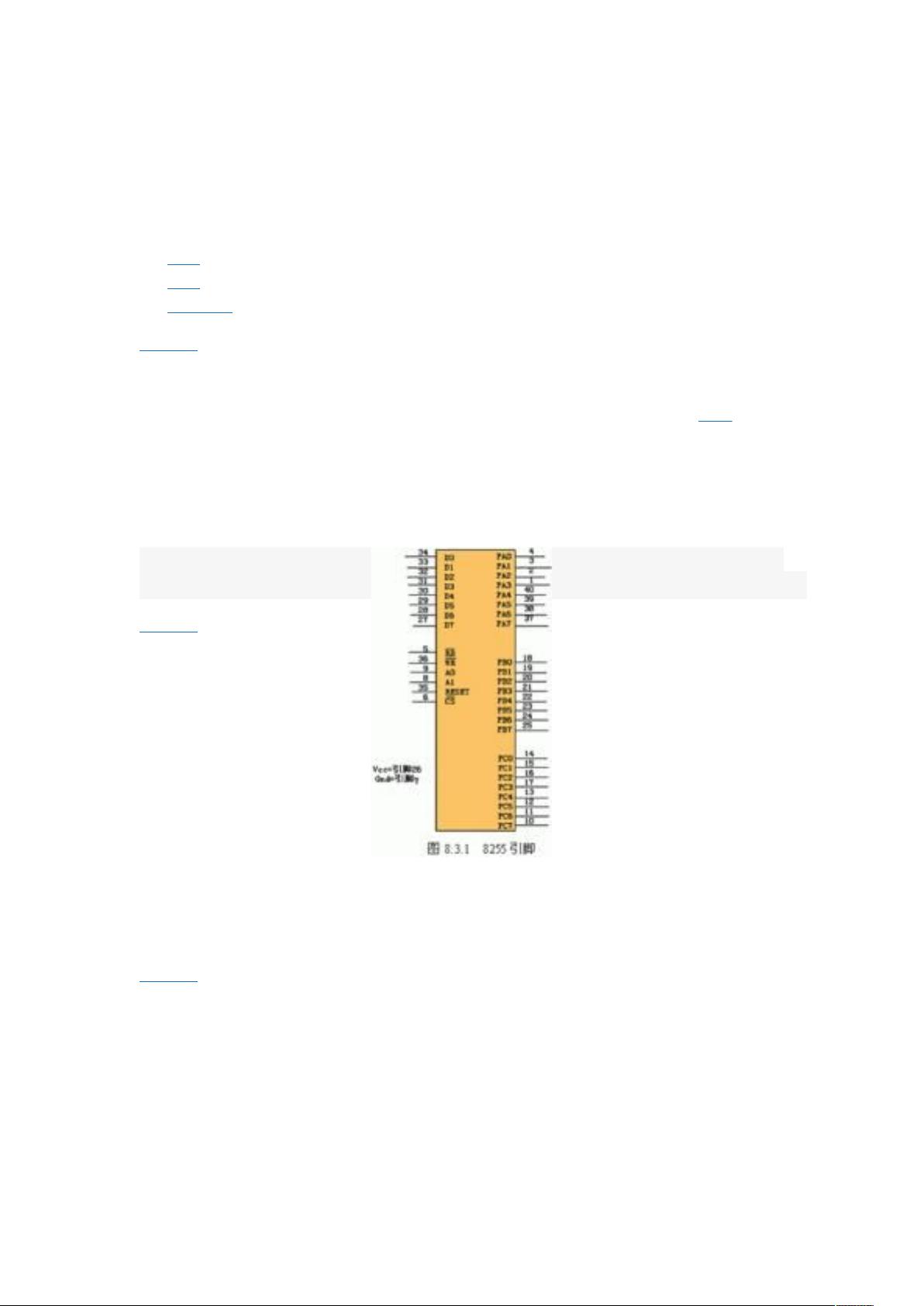

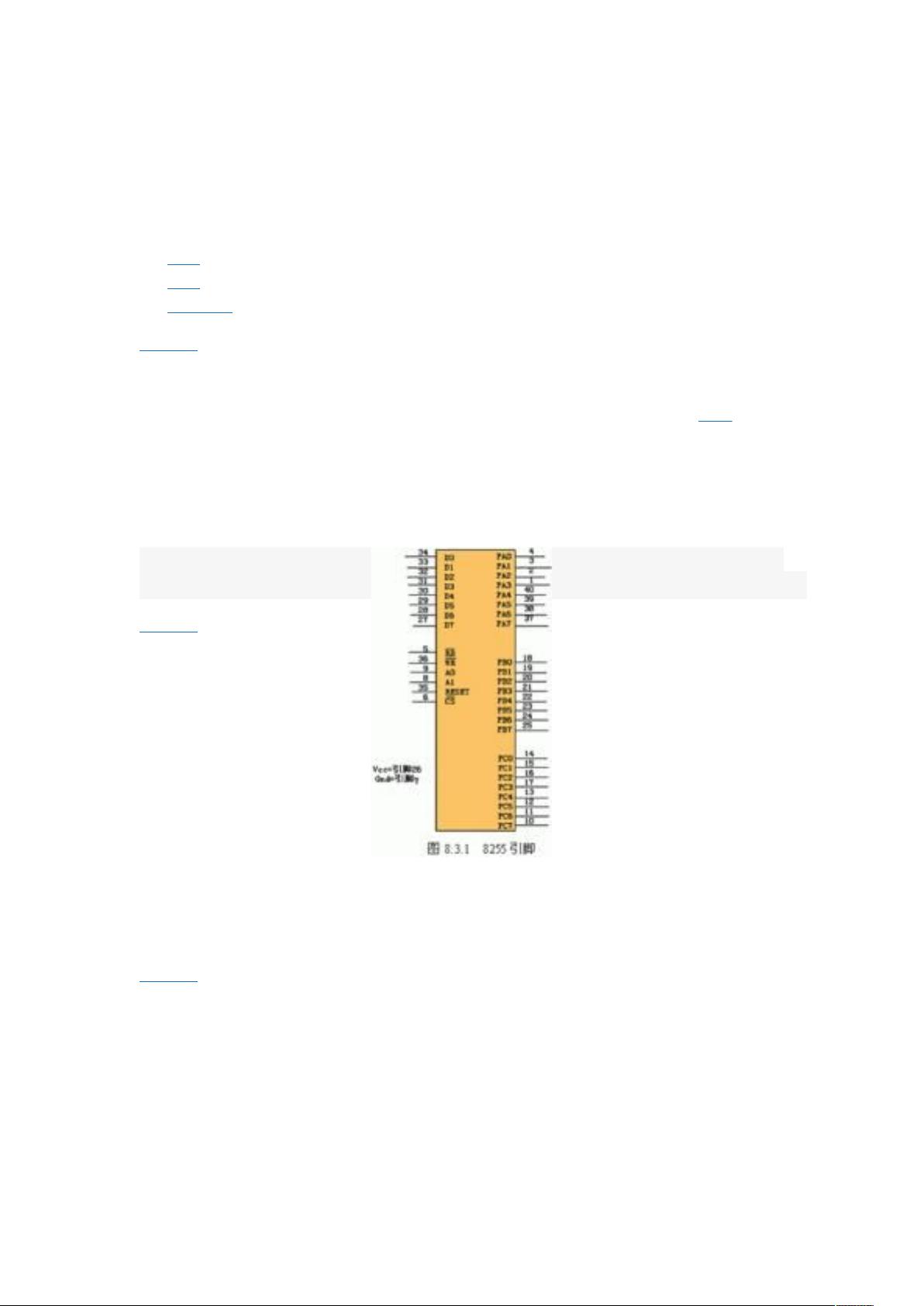

8255 管脚

编辑本段

特性

(1)一 个并行输入/ 输出 的

LSI 芯片,多功能的 I/O 器件,可

作为 CPU 总线 与 外 围的接口 .

(2)具有 24 个可编程设置的 I/O

口, 即 3 组 8 位 的 I/O 口 为 PA

口,PB 口和 PC 口. 它们又可分

为两组 12 位的 I/O 口,A 组包括

A 口 及 C 口 ( 高 4

位,PC4~PC7),B 组包括 B 口及

C 口(低 4 位,PC0~PC3).A 组可设置为基本的 I/O 口,闪控(STROBE)的 I/O 闪控式,双向

I/O3 种模式;B 组只能设置为基本 I/O 或闪控式 I/O 两种模式,而这些操作模式完全由控

制寄存器的控制字决定.

编辑本段

引脚功能

RESET:复位输入线,当该输入端处于高电平时,所有内部寄存器(包括控制寄存

器)均被清除,所有 I/O 口均被置成输入方式。

CS:芯片选择信号线,当这个输入引脚为低电平时,即/CS=0 时,表示芯片被选

中,允许 8255 与 CPU 进行通讯;/CS=1 时,8255 无法与 CPU 做数据传输.

RD:读信号线,当这个输入引脚为低电平时,即/RD=0 且/CS=0 时,允许 8255

通过数据总线向 CPU 发送数据或状态信息,即 CPU 从 8255 读取信息或数据。

WR:写入信号,当这个输入引脚为低电平时 ,即/WR=0 且/CS=0 时,允许 CPU 将

评论2