没有合适的资源?快使用搜索试试~ 我知道了~

首页tef6635 datasheet

资源详情

资源评论

资源推荐

1. General description

The TEF6635 and TEF6638 devices are radio and audio single-chip ICs. These ICs

contain an AM/FM radio tuner, software defined radio signal processing, audio processing

and input/output selection.

The TEF6638 is the premium version that provides th

e full feature set. The TEF6635 is

the lite version including a basic feature set.

The AM/FM radio receiver includes the front ends, tuning

synthesizer, channel filtering,

FM multipath improvement, demodulation, FM stereo decoding, weak signal processing,

no

ise blanking and Radio Data System (RDS) reception. A maximum amount of digital

signal processing is used, taking full advantage of the CMOS IC technology.

The audio processing block receives audio signals from the internal AM/FM radio receiver,

ex

ternal digital radio or external analog or digital audio sources. The audio signal

processing contains basic functionality as tone-volume control as well as advanced digital

audio processing functionality as audio equalization, chimes etc. The output signals of the

audio processing block are provided in digital format on the host I

2

S outputs and in analog

format on the audio DAC outputs.

The TEF6638 supports the digital standards HD Radio and Digital Radio Mondiale (DRM)

in combination with NXP

terrestrial digital radio coprocessors such as SAF356x.

2. Features and benefits

All in one digital receiver including tuner, software defined radio and audio processing

Easy to control with high-level user interface

FM receiver with a tuning range from 65 MHz to

108 MHz covering OIRT, Japan,

Europe and US bands

AM receiver covering Long Wave (LW), Medium Wave (MW) and full Short Wave (SW)

b

ands

Fully integrated tuning system combining low phase noise and fast tuning times

FM Low-Noise Amplifier (LNA)

with Automatic Gain Control (AGC)

FM mixer for frequency conversion to a low Intermediate

Frequency (IF) complex

signal

AM front-end LNA and AGC matching active and passive antenna applications

AM MW RF

selectivity with integrated capacitor bank and automatic calibration

AM mixer fo

r frequency conversion to a low IF complex signal

TEF6635; TEF6638

Highly efficient radio one-chip

Rev. 2 — 19 July 2011 Product data sheet

TEF6635_TEF6638 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 2 — 19 July 2011 2 of 81

NXP Semiconductors

TEF6635; TEF6638

Highly efficient radio one-chip

High dynamic range Sigma-Delta (SD) IF Analog-to-Digital Converter (ADC)

Digital IF signal processing including decimation, shift to baseband, AGC control,

In-

phase/Quadrature-phase (I/Q) correction, Precision Adjacent Channel Suppression

(PACS), FM multipath suppression and demodulation

Baseband I

2

S output for support of HD Radio and DRM with external digital radio

coprocessor (TEF6638)

Signal quality detection, FM stereo decod

ing, noise blanking and weak signal

processing

Advanced RDS and Radio Broadcast Data System (RBDS) demodulation and

d

ecoding with versatile output configuration

One (TEF6635) or two (TEF6638) stereo third-order sigma-delta audio

Ana

log-to-Digital Converters (ADCs) with an anti-aliasing input filter

Three analog audio inputs with flexible inp

ut configuration connected to the analog

input selector and audio ADC

One differential stereo input connected to

the second audio ADC (TEF6638)

Two (TEF6635) or three (TEF6638) asynchronous Inter IC Sound (I

2

S) inputs

One analog So

ny Philips Digital InterFace (SPDIF) format input

One digita

l SPDIF input, mutually exclusive with one asynchronous I

2

S input

One (TEF6635) or two (TEF6638) synchronous I

2

S inputs and outputs in master mode

Audio sample rate converters

Digital audio processing with tone and volume control functions

Four audio Digital-to-Analog Converters (DACs)

Single 3.3 V su

pply voltage

Fast mode I

2

C-bus (400 kHz)

Built-in 1.2 V

regulator control circuit

Qualified i

n accordance with AEC-Q100

3. Applications

Single tuner AM/FM receivers addressing aftermarket and entry-level to mainstream

OEM in the automotive segment

4. Ordering information

Table 1. Ordering information

Type number Package

Name Description Version

TEF6635HW HTQFP100 plastic thermal enhanced thin quad flat package; 100 leads;

body 14 14 1 mm; exposed die pad

SOT638-3

TEF6638HW

xxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx x xxxxxxxxxxxxxx xxxxxxxxxx xxx xxxxxx xxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxx

xxxxx xxxxxx xx xxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxx xxxxxxx xxxxxxxxxxxxxxxxxxx

xxxxxxxxxxxxxxxx xxxxxxxxxxxxxx xxxxxx xx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxx xxxxxxx

xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxx xxxxx x x

TEF6635_TEF6638 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 2 — 19 July 2011 3 of 81

NXP Semiconductors

TEF6635; TEF6638

Highly efficient radio one-chip

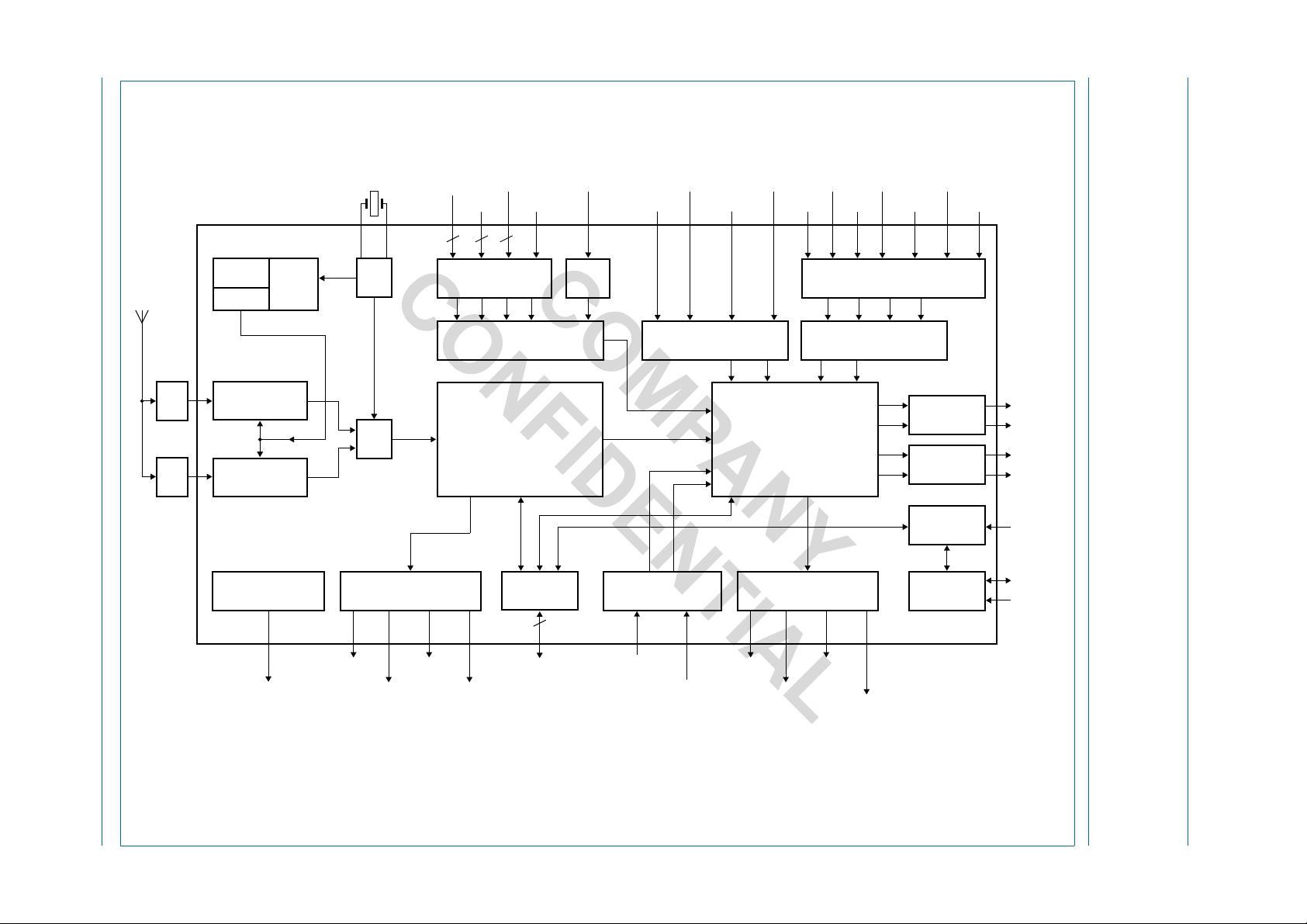

5. Functional diagram

(1) Not available in TEF6635.

Fig 1. Functional diagram

008aaa197

TEF6635

TEF6638

DCO

ANALOG INPUT SELECTOR

DIGITAL

TUNING

SYSTEM

SDA

SCL

AUDIO PROCESSING

XTAL

OSC

INPUT BUFFER

I

2

C-BUS

HOST_BCK

IC CONTROL

UNIT

HOST_O_SD_1

(1)

HOST_WS

HOST_O_SD_0

HOST_I_SD_1

(1)

HOST_I_SD_0

AIN_2_REF

DAC_RR

DAC_RL

STEREO

DAC

DAC_FR

DAC_FL

STEREO

DAC

STEREO

ADC

STEREO

ADC

(1)

OUTPUT BUFFER

AIN_1_REF

AIN_1_L

AIN_3

AIN_1_R AIN_3_REF

AIN_2

AIN_0_L

(1)

AIN_0_L_REF

(1)

AIN_0_R

(1)

AIN_0_R_REF

(1)

RADIO PROCESSING

INPUT BUFFER

SPDIF

SPDIF_IN_0_AI2S_IN_2

(1)

I2S_IN_1

I2S_IN_0

DIGITAL INPUT SELECTOR

DIVIDERS

ADC

DR_BCK

(1)

DR_WS

(1)

DR_I_DATA

(1)

DR_Q_DATA

(1)

OUTPUT BUFFER

(1)

FM FRONT-END

AM FRONT-END

FM

BPF

AM

BPF

RESETN

I/O MUX

GPIO

9

1.2 V REGULATOR

CONTROL

BIT

SLICER

3 3 3

CTRL_1V2_SUPPLY

TEF6635_TEF6638 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 2 — 19 July 2011 4 of 81

NXP Semiconductors

TEF6635; TEF6638

Highly efficient radio one-chip

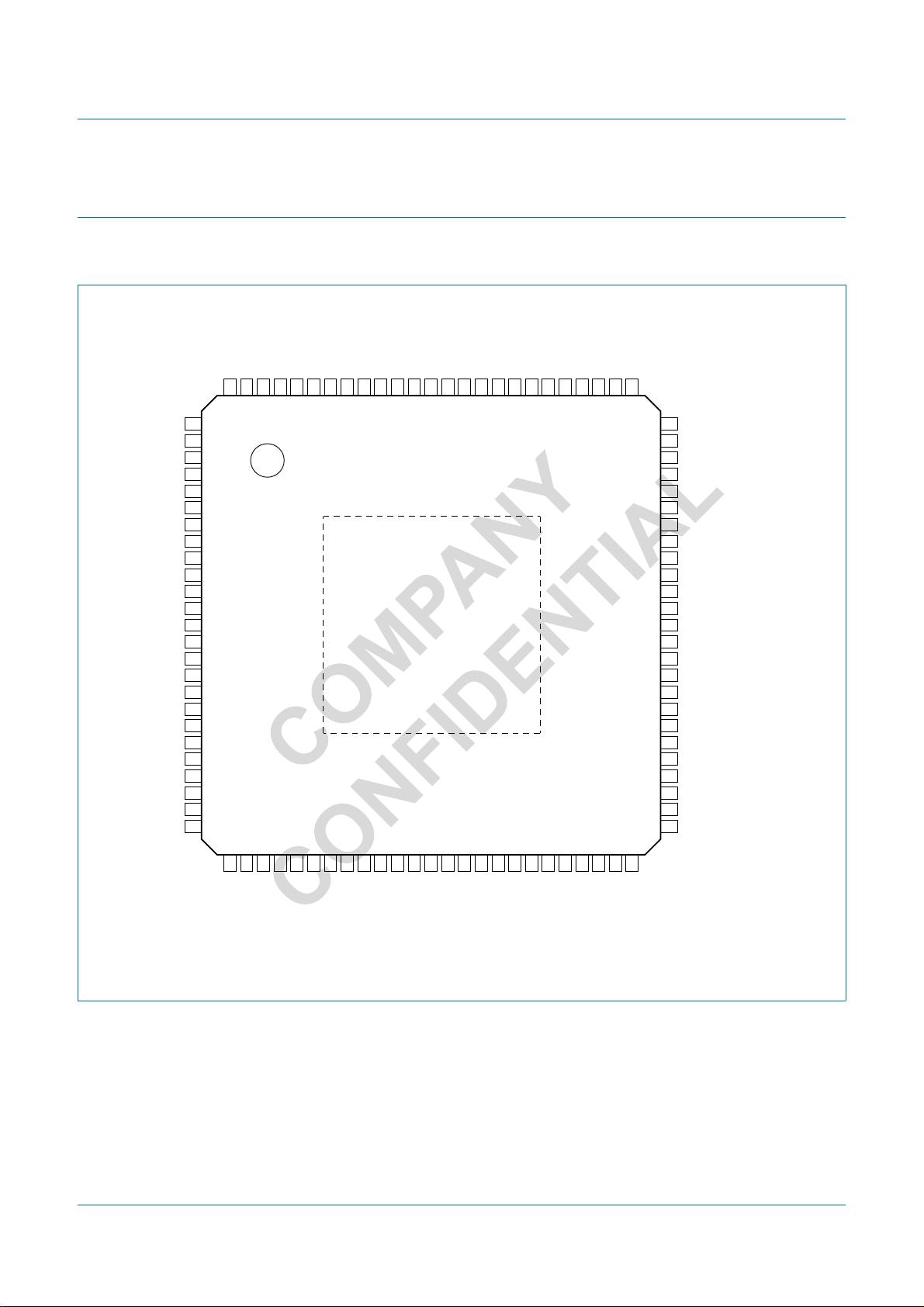

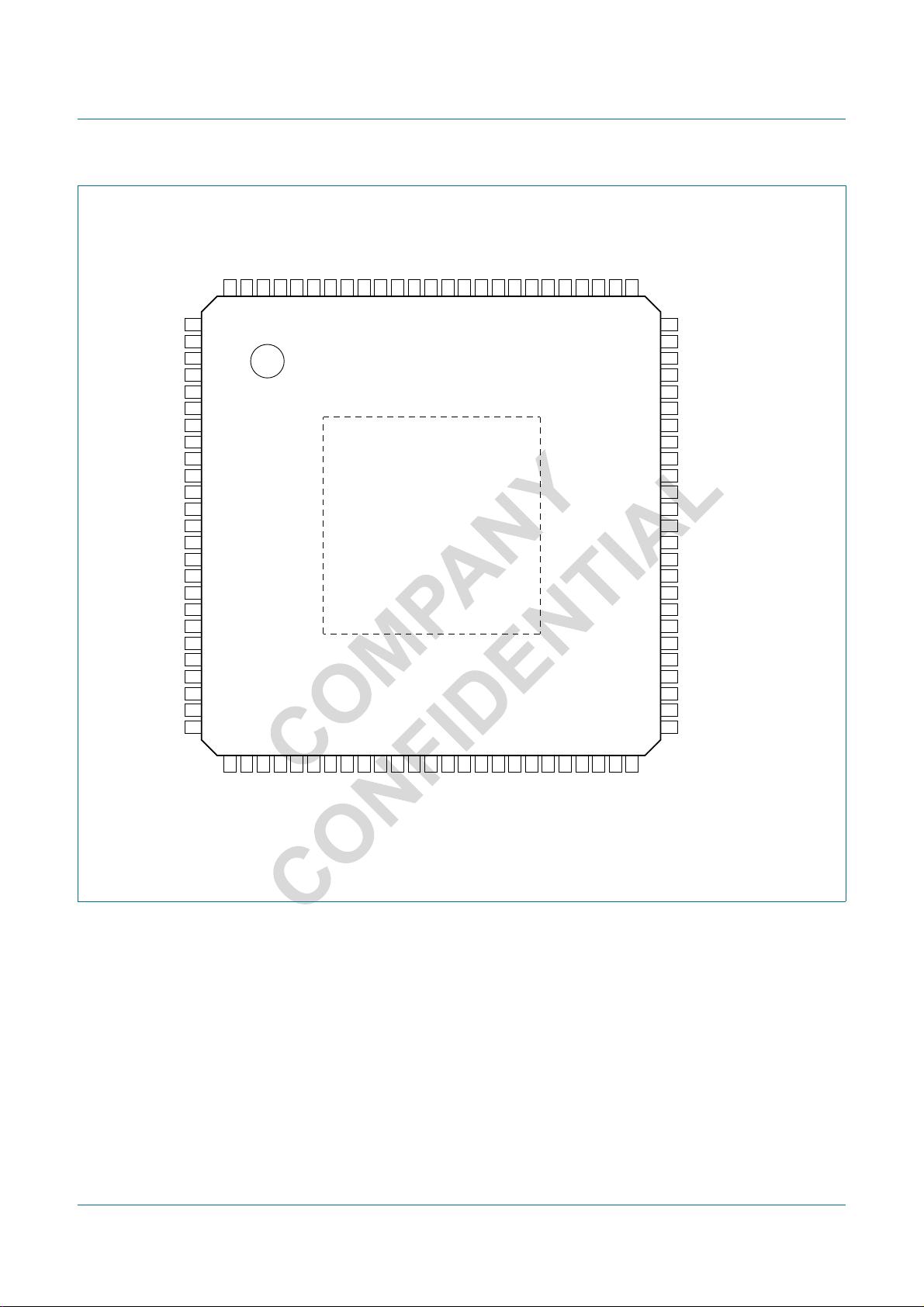

6. Pinning information

6.1 Pinning

Fig 2. Pin configuration for TEF6635HW

TEF6635HW

VDDIO_0_3V3 VDDM_1_1V2

i.c. VDDIO_2_3V3

i.c. VDDC_1_1V2

i.c. CTRL_1V2_SUPPLY

I2S_SD_IN_1 SDA

I2S_WS_IN_1 SCL

I2S_BCK_IN_1 RESETN

GPIO_4 I2S_BCK_IN_0

GPIO_3 I2S_WS_IN_0

GPIO_2 VSSD

GPIO_1 I2S_SD_IN_0/SPDIF_IN_0_D

GPIO_0 VDDA_PL550_1V2

TRSTN VDDD_PLL_3V3

AM_MIX_IN_N SPDIF_IN_0_A

AM_IN_P DAC_FL

VSSA_IF DAC_FR

VREF AIN_3

VDDA_RF_3V3 AIN_3_REF

i.c.

AM_MIX_IN_P

VSSA_RF_1

LNA_OUT_P

LNA_OUT_N

AM_LNA_CAP

AIN_2_REF

VDDA_CODEC_3V3

VREF_CODEC

VSSA_CODEC

DAC_RL

DAC_RR

i.c. AIN_2

i.c. VDDM_0_1V2

i.c. VDDC_0_1V2

FM_IN_N HOST_I_SD_0

FM_IN_P i.c.

FM_CAP HOST_BCK

VSSA_RF_0 i.c.

VDDA_LNA_3V3 HOST_WS

VSSA_SUBA_1 i.c.

VSSA_XTAL HOST_O_SD_0

XTAL_OUT i.c.

XTAL_IN i.c.

VDDA_PLL_3V3 i.c.

VSSA_PLL GPIO_8

VSSA_IFADC VDDIO_1_3V3

i.c. i.c.

i.c. i.c.

i.c. i.c.

AIN_1_R GPIO_5

AIN_1_REF

VDDA_IFADC_3V3

IFADC_DEC

VSSR_IFADC

VSSA_SUBA_2

i.c.

GPIO_6

i.c.

i.c.

i.c.

i.c.

i.c.

AIN_1_L GPIO_7

008aaa255

1

2

3

4

5

6

7

8

9

10

11

12

13

14

20

21

22

23

24

25

75

74

73

72

71

70

69

68

67

66

65

64

63

62

56

55

54

53

52

51

15

16

17

18

19

61

60

59

58

57

26

27

28

29

30

31

32

33

34

35

36

37

38

39

45

46

47

48

49

50

99

98

97

96

95

94

93

92

91

90

89

88

87

81

80

79

78

77

76

40

41

42

43

44

86

85

84

83

82

100

TEF6635_TEF6638 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 2 — 19 July 2011 5 of 81

NXP Semiconductors

TEF6635; TEF6638

Highly efficient radio one-chip

Fig 3. Pin configuration for TEF6638HW

TEF6638HW

VDDIO_0_3V3 VDDM_1_1V2

I2S_SD_IN_2 VDDIO_2_3V3

I2S_WS_IN_2 VDDC_1_1V2

I2S_BCK_IN_2 CTRL_1V2_SUPPLY

I2S_SD_IN_1 SDA

I2S_WS_IN_1 SCL

I2S_BCK_IN_1 RESETN

GPIO_4 I2S_BCK_IN_0

GPIO_3 I2S_WS_IN_0

GPIO_2 VSSD

GPIO_1 I2S_SD_IN_0/SPDIF_IN_0_D

GPIO_0 VDDA_PL550_1V2

TRSTN VDDD_PLL_3V3

AM_MIX_IN_N SPDIF_IN_0_A

AM_IN_P DAC_FL

VSSA_IF DAC_FR

VREF AIN_3

VDDA_RF_3V3 AIN_3_REF

i.c.

AM_MIX_IN_P

VSSA_RF_1

LNA_OUT_P

LNA_OUT_N

AM_LNA_CAP

AIN_2_REF

VDDA_CODEC_3V3

VREF_CODEC

VSSA_CODEC

DAC_RL

DAC_RR

i.c. AIN_2

i.c. VDDM_0_1V2

i.c. VDDC_0_1V2

FM_IN_N HOST_I_SD_0

FM_IN_P HOST_I_SD_1

FM_CAP HOST_BCK

VSSA_RF_0 i.c.

VDDA_LNA_3V3 HOST_WS

VSSA_SUBA_1 i.c.

VSSA_XTAL HOST_O_SD_0

XTAL_OUT i.c.

XTAL_IN HOST_O_SD_1

VDDA_PLL_3V3 i.c.

VSSA_PLL GPIO_8

VSSA_IFADC VDDIO_1_3V3

AIN_0_R_REF i.c.

AIN_0_L_REF DR_BCK

AIN_0_L i.c.

AIN_1_R GPIO_5

AIN_1_REF

VDDA_IFADC_3V3

IFADC_DEC

VSSR_IFADC

VSSA_SUBA_2

AIN_0_R

GPIO_6

DR_Q_DATA

i.c.

DR_I_DATA

i.c.

DR_WS

AIN_1_L GPIO_7

008aaa256

1

2

3

4

5

6

7

8

9

10

11

12

13

14

20

21

22

23

24

25

75

74

73

72

71

70

69

68

67

66

65

64

63

62

56

55

54

53

52

51

15

16

17

18

19

61

60

59

58

57

26

27

28

29

30

31

32

33

34

35

36

37

38

39

45

46

47

48

49

50

99

98

97

96

95

94

93

92

91

90

89

88

87

81

80

79

78

77

76

40

41

42

43

44

86

85

84

83

82

100

剩余80页未读,继续阅读

san_wang

- 粉丝: 1

- 资源: 1

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 27页智慧街道信息化建设综合解决方案.pptx

- 计算机二级Ms-Office选择题汇总.doc

- 单链表的插入和删除实验报告 (2).docx

- 单链表的插入和删除实验报告.pdf

- 物联网智能终端项目设备管理方案.pdf

- 如何打造品牌的模式.doc

- 样式控制与页面布局.pdf

- 武汉理工Java实验报告(二).docx

- 2021线上新品消费趋势报告.pdf

- 第3章 Matlab中的矩阵及其运算.docx

- 基于Web的人力资源管理系统的必要性和可行性.doc

- 基于一阶倒立摆的matlab仿真实验.doc

- 速运公司物流管理模式研究教材

- 大数据与管理.pptx

- 单片机课程设计之步进电机.doc

- 大数据与数据挖掘.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论5