没有合适的资源?快使用搜索试试~ 我知道了~

首页DDR2规范中文版.pdf

DDR2规范中文版.pdf

模式寄存器中的数据控制着DDR2 SDRAM的操作模式.它控制着CAS 延迟, 突发长度, 突发顺序, 测试模式, DLL复位, WR等各种选项,支持着DDR2 SDRAM 的各种应用. 模式寄存器的默认值没有被定义, 所以上电之后必须按规定的时序规范来设定模式寄存器的值. 通过将 CS, RAS, CAS, WE, BA0 , BA1置低来发布模式寄存器设定命令, 操作数通过地址脚A0 ~ A15同步送出. DDR2 SDRAM 在写模式寄存器之前,应该通过拉高CKE而完成了所有簇的裕充 电。模式寄存器设定命令的命令周期 (tMRD)必须满足完成对模式寄存器的写操作。在进行正常操作时,只要所有的簇都已经处于预充电完成状态,模式寄存 器都可以使用同一命令重新设定. 模式寄存器不同的位表示不同的功能. A0 ~ A2 设定突发长度是4还是8。突发长度的译码规则与DDR SDRAM相同. A3定义

资源详情

资源评论

资源推荐

Device Operations

DDR2 SDRAM

1

DDR2 SDRAM

操作时序规范

Device Operations

DDR2 SDRAM

2

基本功能

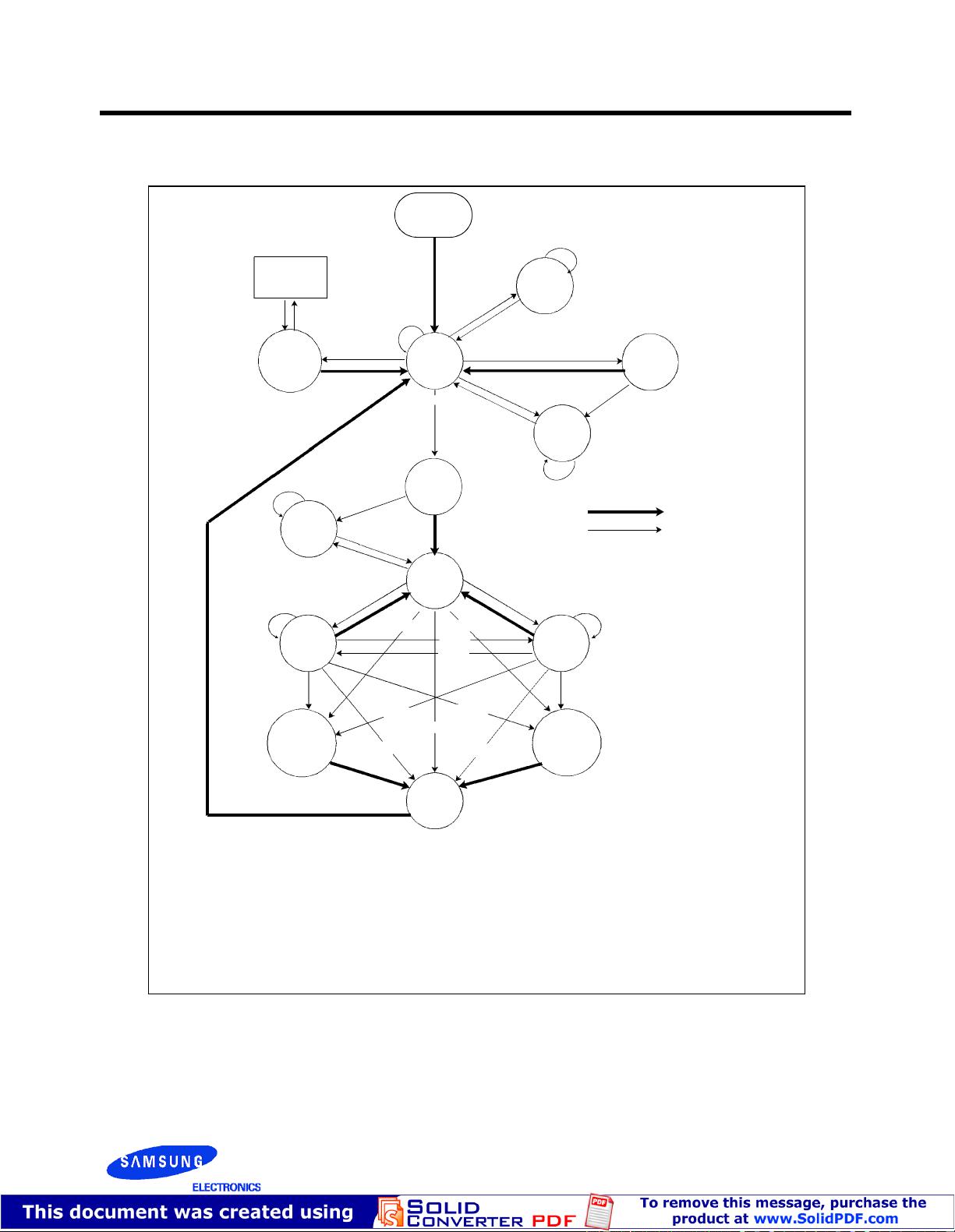

简单状态转换图:

初始化

CKEL

OCD

校准

SRF

PR

自我刷新

CKEH

设定

MRS

EMRS

(E)MRS

空闲

所有蔟已

预充电完成

REF

刷新

ACT

CKEL

CKEH

预充电

断电

CKEL

CKEL

主动

断电

Write

CKEL

CKEH

CKEL

Write

激活

簇激活

Read

CKEL

Read

自动默认流程

外加命令流程

写数据

WRA

RDA

Read

Write

读数据

WRA

带自动预

充电的写

WRA

PR, PRA

RDA

RDA

带自动

预充电

的读

PR, PRA PR, PRA

预充电

CKEL = CKE 低, 进入断电状态

CKEH = CKE 高,结束断电状态 ,结束自我刷新

ACT = 激活命令

WR(A) = 带自动预充电的写命令

RD(A) = 带自动预充电的读命令

PR(A) = 所有簇自动预充电命令

(E)MRS = 设定(扩展)模式寄存器命令

SRF = 进入自我刷新命令

REF =刷新命

注意 : 要谨慎使用此图 .

此图只是提供了所有可能的状态和状态见转换的控制命令

,而非全部细节.实际使用过程中可能出现的包括不止一

个簇,激活或禁止片内终结电阻 ,进入或结束断电状态等情况 ,这些情况的细节并没有全部列入上面的状态转换图 。

Device Operations

DDR2 SDRAM

3

基本功能

对 DDR2 SDRAM的访问是基于突发模式的 ; 读写时,选定一个起始地址 ,并按照事先编程设定的突发长度 (4或8)和突发顺序来依次读写 .访问操作开始

一个激活命令 , 后面紧跟的就是读或者写命令 。和激活命令同步送达的地址位包含了所要存取的簇和行 (BA0, BA1 选定簇; A0-A13 选定行). 和读或写命令

同步送达的地址位包含了突发存取的起始列地址 ,并决定是否发布自动预充电命令 。

在进行常用的操作之前 , 要先对 DDR2 SDRAM 进行初始化. 下面的几小节介绍初始化的详细信息 ,寄存器的定义 ,命令的描述和芯片的操作 。

上电和初始化

DDR2 SDRAM必须以预定义的时序进行上电和初始化 . 不按规定的操作将导致不可预期的情况出现 。.

上电和初始化时序

1. 对于上电和初始化来说 ,下列时序是必须的 。

供电且保持CKE 低于 0.2*V

DDQ

, ODT

*1

要处于低电平状态 (所有的其余脚可以都没有定义 .) 电源上升沿不可以有任何翻转 ,上升沿时间不能大于 200mS;

并且要求在电压上升沿过程中满足 , V

DD

>V

DDL

>V

DDQ

且 V

DD

-V

DDQ

<0.3 volts.

- V

DD

*2

, V

DDL

*2

和 V

DDQ

必须由同一个电源芯片供电 , 并且

- V

TT

最大只能到 0.95 V, 并且

- Vref 要时刻等于 V

DDQ

/2.

,紧跟

V

DDQ

变化。

或者

-在给 V

DDL

上电的同时或之前就给 V

DD

*2

.

上电

-在给 V

DDQ

上电的同时或之前就给

V

DDL

*2

上电

-

在给

V

TT

& V

REF

上电的同时或之前就给

V

DDQ

上电

.

上面的两个条件至少要满足一个 。

2. 开始时钟信号并保持信号稳定 .

3.在稳定电源和时钟 (CK, /CK)之后至少200s,

然后发布

NOP 或者取消选定命令 &

拉高

CKE.

4. 等待至少 400ns然后发布预充电所有簇 命令.在等待的400ns过程中要发布NOP或者取消选定命令 .

5. 发布 EMRS(2)命令. (EMRS(2) 命令, 需要将 BA0拉低, 将 BA1拉高.)

6. 发布 EMRS(3) 命令. (为了发布EMRS(3)命令,将 BA0和 BA1拉高.)

7.发布 EMRS命令以激活 DLL. (为了发布"DLL激活" 命令,将 A0拉低, BA0拉高 并且将 BA1-2和 A13-A15置低.)

8. 发布MRS命令实现 “DLL复位”

*2

.

(为了发布DLL 复位命令, 需要将 A8拉高 并使 BA0-1为低)

9. 发布预充电所有簇命令 。

10. 至少发布两次自动刷新命令 .

11. 将 A8拉低,发布模式寄存器设定命令 (MRS)对芯片进行初始化操作 . (也就是不对 DLL复位,编程芯片的操作参数 )

12.在第8步之后至少过200个时钟周期,执行OCD 校准 ( 片外驱动电阻调校 ).

如果不使用

OCD校准, EMRS OCD 校准模式结束命令 (A9=A8=A7=0) 必须在EMRS OCD默认命令 (A9=A8= A7=1)之后发布,用来设定EMRS的其它操

作参数。

13. 现在, DDR2 SDRAM 就准备好可以进行普通的操作了 。.

*1) 为了保证 ODT关闭, V

REF

必须有效 并且 ODT脚必须拉低.

*2)

如果

V

DDL

或V

DD

的电平值在正常操作过程中人为改变 , (例如e, 为了 V

DD

相交测试, 或者节省功率 )

则必须执行 “DLL 复位”.

Device Operations

DDR2 SDRAM

4

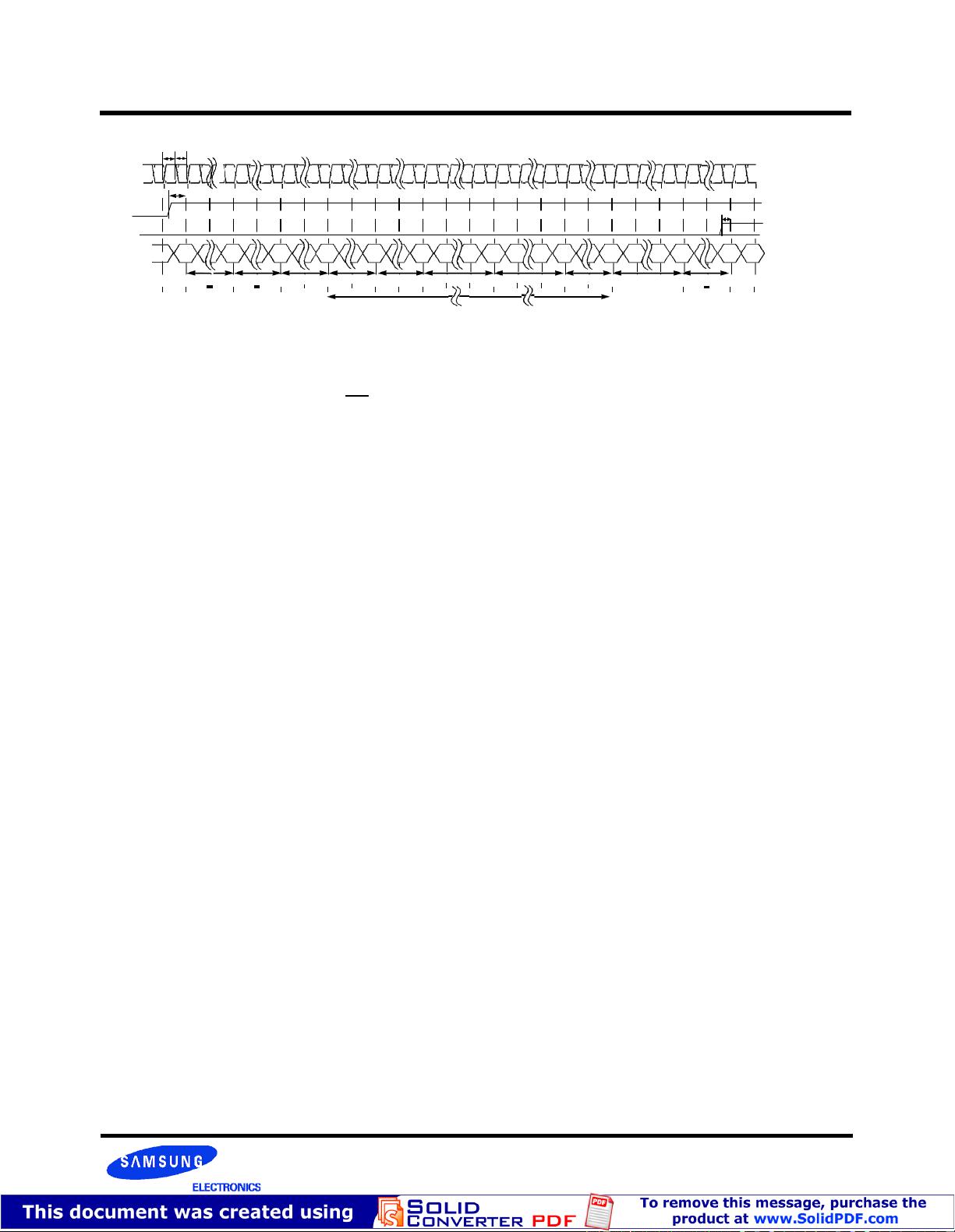

上电后的初始化时序图

tCHtCL

CK

/CK

tIS

CKE

ODT

Command

NOP

PRE

ALL

EMRS MRS

PRE

ALL

REF

REF

MRS EMRS

tIS

ANY

EMRS

CMD

400ns tRP

DLL

tMRD

tMRD

DLL

tRP

tRFC

tRFC

min. 200 Cycle

tMRD

OCD

Follow OCD

Flowchart

OCD

tOIT

ENABLE

RESET

Default

CAL. MODE

EXIT

编程(扩展)模式寄存器

为了增强使用灵活性 , 突发长度, 突发类型, /CAS延迟, DLL 复位功能, 写恢复时间(WR) 都是可以定义的变量 。通过预先编程模式寄存器就可以设定它们 . 除

此之外, DLL 禁止功能, 驱动电阻, 附加 CAS 延迟, ODT(终结电阻), 单线选通, 和 OCD(片外驱动电阻调整 ) 同样也是可以定义的变量 ,通过预先编程扩展

模式寄存器就可以设定它们 . 模式寄存器或者扩展模式寄存器的内容可以通过对他们进行重新设定来改变它们 .

如果用户只是想改变寄存器中某些特定的位 ,

也必须通过

MRS

或

EMRS

命令对全部寄存器位进行重新设定 。

MRS, EMRS和t DLL 复位这些命令并不会影响存储阵列的内容 ,这意味着上电后的任意时间执行初始化操作不会改变存储的内容 。

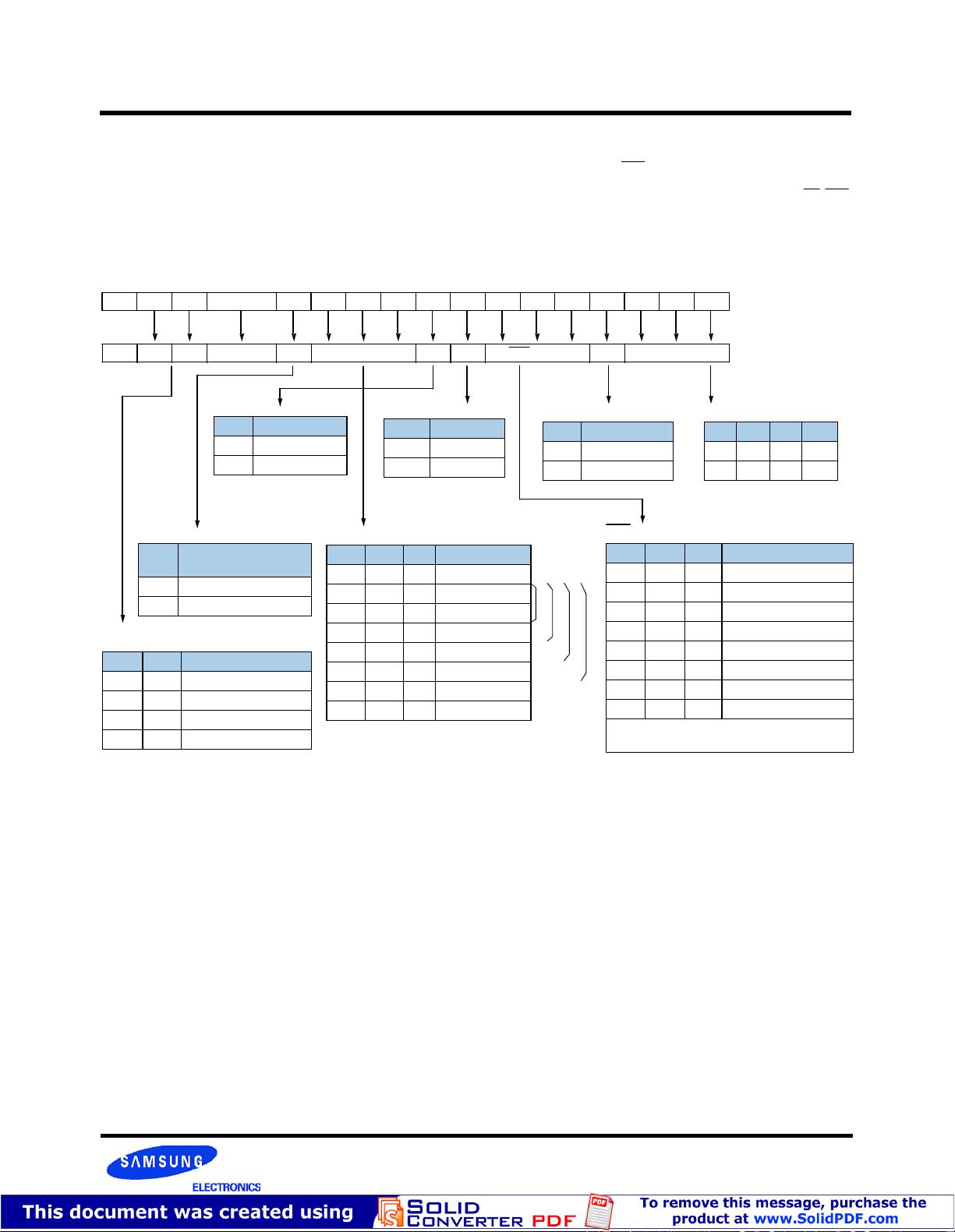

Device Operations

DDR2 SDRAM

BA2*

1

BA1

BA0

A15*

1

~A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

A7

mode

0

Normal

1

Test

A3

Burst Type

0

Sequential

1

Interleave

A12

主动下电结束

时间

0

快速结束(use tXARD)

1

慢速结束(use tXARDS)

A2

A1

A0

BL

0

1

0

4

0

1

1

8

A11

A10

A9

WR(周期)

0

0

0

Reserved

0

0

1

2

0

1

0

3

0

1

1

4

1

0

0

5

1

0

1

6

1

1

0

Reserved

1

1

1

Reserved

A6

A5

A4

延迟

0

0

0

保留

0

0

1

保留

0

1

0

2 (可选)

0

1

1

3 (speed bin determined)*

1

0

0

4

1

0

1

5 (speed bin determined)*

1

1

0

6 (speed bin determined)*

1

1

1

Reserved

* speed bin determined

= Not required on all speed bin

DDR2-400

DDR2-533

DDR2-667

DDR2-800

DDR2 SDRAM

模式寄存器设定

(MRS)

模式寄存器中的数据控制着 DDR2 SDRAM的操作模式.

它控制着

CAS 延迟, 突发长度 , 突发顺序,

测试模式

, DLL复位, WR等各种选项,支持着 DDR2

SDRAM 的各种应用. 模式寄存器的默认值没有被定义 ,

所以上电之后必须按规定的时序规范来设定模式寄存器的值

. 通过将 CS, RAS, CAS, WE, BA0 ,

BA1置低来发布模式寄存器设定命令 , 操作数通过地址脚 A0 ~ A15同步送出. DDR2 SDRAM 在写模式寄存器之前 ,应该通过拉高CKE而完成了所有簇的裕充

电。模式寄存器设定命令的命令周期 (tMRD)必须满足完成对模式寄存器的写操作 。在进行正常操作时 ,只要所有的簇都已经处于预充电完成状态 ,模式寄存

器都可以使用同一命令重新设定 . 模式寄存器不同的位表示不同的功能 . A0 ~ A2 设定突发长度是 4还是8。 突发长度的译码规则与 DDR SDRAM相同. A3定义

了突发地址顺序。A4 ~ A6定义了CAS延迟。. DDR2不支持半时钟延迟。 A7 设定测试模式. A8设定 DLL 复位。 对通常的 MRS操作,A7必须设定为低。

A9 ~ A11定义了写恢复时间 WR. 详细情况见下面的示意图 :.

地址字段

0*

1

0 0 0*

1

PD WR DLL TM CAS 延迟 BT 突发长度 模式寄存器

Burst Length

A8

DLL Reset

0

No

1

Yes

自动预充电的写恢复时间

CAS延迟

*2

BA1

BA0

MRS模式

0

0

MRS

0

1

EMRS(1)

1

0

EMRS(2): 保留

1

1

EMRS(3): 保留

*1 : A13现在保留,以后备用,设置模式寄存器时要设为 0。

BA2 和 A14 对于 512Mb DDR2不使用,但对于 1Gb 和2Gb DDR2 SDRAMs使用. A15 保留,以被后用

*2 : WR(自动预充电的写恢复时间 )的最小值由 tCK的最大值决定,而WR最大值由 tCK 最小值决定. WR 的计算方法是看 tWR 有几个时钟

周期,如果是小数,则进位为大一的整 数(WR[cycles] = tWR(ns)/tCK(ns)). 模式寄存器必须编程为这个值 . 同样的方法用 tRP决定 tDAL.

剩余46页未读,继续阅读

文韬-武略

- 粉丝: 8

- 资源: 17

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

- MW全能培训汽轮机调节保安系统PPT教学课件.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论10