没有合适的资源?快使用搜索试试~ 我知道了~

首页PCI Express SFF-8639 Module Specification

资源详情

资源评论

资源推荐

PCI Express

SFF-8639 Module

Specification

Revision 3.0, Version 0.9

February 22, 2018

PCI-SIG

®

disclaims all warranties and liability for the use of this document and the information contained herein and assumes no

responsibility for any errors that may appear in this document, nor does PCI-SIG make a commitment to update the information

contained herein.

Contact the PCI-SIG office to obtain the latest revision of this specification.

Questions regarding the PCI Express SFF-8639 Module Specification or membership in PCI-SIG may be forwarded to:

Membership Services

www.pcisig.com

E-mail: administration@pcisig.com

Phone: 503-619-0569

Fax: 503-644-6708

Technical Support

techsupp@pcisig.com

DISCLAIMER

This PCI Express SFF-8639 Module Specification is provided as is with no warranties whatsoever, including any warranty of

merchantability, non-infringement, fitness for any particular purpose, or any warranty otherwise arising out of any proposal,

specification, or sample. PCI-SIG disclaims all liability for infringement of proprietary rights, relating to use of information in this

specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

Trademarks

PCI, PCI Express, PCIe, ExpressModule, and PCI-SIG are trademarks or registered trademarks of PCI SIG. Other company and

product names may be trademarks of the respective companies with which they are associated.

Copyright

© 2014 – 2017 PCI SIG. All rights reserved.

1

PCI Express SFF-8639 Module

PCI Express SFF-8639 Module | 3

Revision History

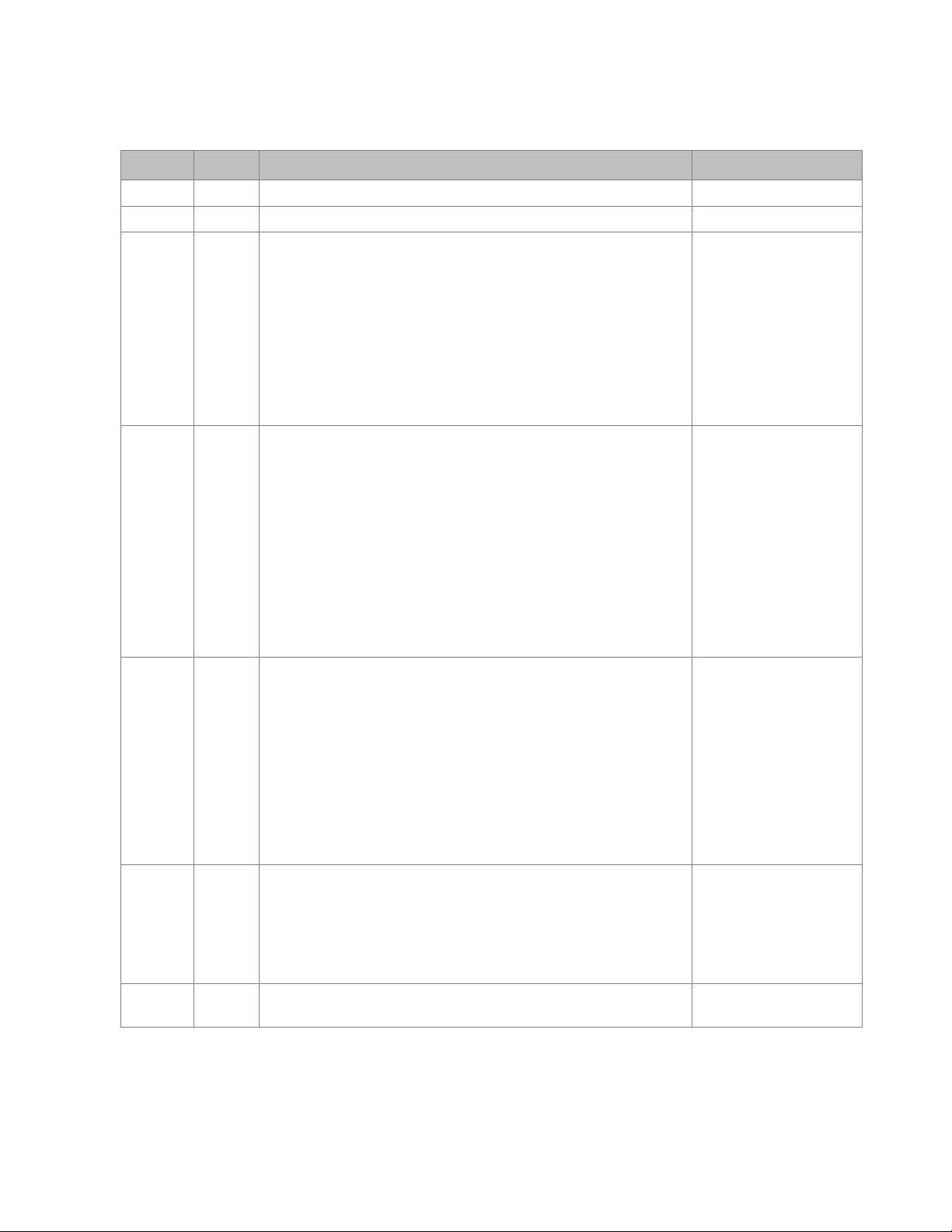

2

Revision

Version

History

Date

3.0

Initial draft 0.3

June 26, 2013

3.0

Initial draft 0.5

September 10, 2013

3.0

0.3

Updated the following Figures:

• Figure 1-1. Vertical SFF-8639 Receptacle

• Figure 1-2

• Figure 2-3 through Figure 2-9

• Figure 4-1 through Figure 4-5. Jitter Budget

• Figure 5-1. Illustration of Adjacent Pairs

• Added Table 2-3

• Global changes:

- Replaced REFCLK with REFCLK(B)

- Replaced PERST# with PERST(B)#.

August 6, 2014

3.0

0.4

Due to the very large number of changes to the revision 0.9

specification the revision level was reverted to 0.7.

• Global changes:

- Replaced REFCLK(B) with REFCLK

- Replaced PERST# with PERST#.

• Updated Figure 2-1, Figure 2-10, Figure 2-11, and

Figure 2-13

• Replaced REFCLK(B)- to REFCLK-

• Replaced PERSTB(B)# with PERSTB#

• Replaced IFDET with IfDet

• Replaced +3.3 Vaux with +3.3 Vaux

• General clean-up

September 6, 2016

3.0

0.5

• Added PWRDIS (Optional) to Auxiliary Signals

• Added PWRDIS Electrical Characteristics

• Added Table 2-6, PWRDIS DC and AC Electrical Characteristics

Applied to the SFF-8639 Module

• Miscellaneous fixes

• Incorporated the MAY Integrated 0p705 Draft SFF Connector

Comment List Round 11

• Incorporated the Integrated0p706 Draft SFF Connector

Comment List Round12

• Incorporated the Integrated0p706 June30 DraftSFF Connector

Comment List Round14

July 20, 2017

3.0

0.6

• Added reference to +12 V power to section 2.8, PWRDIS

(Optional)

• Updated Table 2 4 and Table 2 6.

• Incorporated Oct 04 Comments, Round 16

• Incorporated Oct 04 Comments, Round 17

• Incorporated Nov 07 Comments, Round 18

December 19, 2017

3.0

0.9

• Fixed typo in Table A-1.

• Rolled Revision to .09

February 27, 2018

3

PCI Express SFF-8639 Module

PCI Express SFF-8639 Module | 4

Table of Contents

4

1. SFF-8639 Connector Interface ................................................................................ 9

5

1.1. Document Organization .................................................................................................. 9

6

1.2. Capitalizations ................................................................................................................ 9

7

1.3. Terms and Definitions ..................................................................................................... 9

8

1.4. Reference Documents ...................................................................................................10

9

1.5. Specification Contents ...................................................................................................11

10

1.6. Objectives .....................................................................................................................11

11

1.7. Electrical Overview ........................................................................................................12

12

1.8. Mechanical Overview ....................................................................................................13

13

2. Auxiliary Signals .................................................................................................... 14

14

2.1. Reference Clock ............................................................................................................16

15

2.1.1. Low Voltage Swing, Differential Clocks ................................................................................... 16

16

2.1.2. Spread Spectrum Clocking (SSC) ........................................................................................... 17

17

2.1.3. REFCLK AC Specifications ..................................................................................................... 17

18

2.1.4. REFCLK Phase Jitter Specification for 2.5 GT/s Signaling Support ....................................... 21

19

2.1.5. REFCLK Phase Jitter Specification for 5.0 GT/s Signaling Support ....................................... 22

20

2.1.6. REFCLK Phase Jitter Specification for 8.0 GT/s Signaling Support ....................................... 22

21

2.2. PERST# Signal .............................................................................................................23

22

2.2.1. Initial Power-Up (G3 to S0) ...................................................................................................... 23

23

2.2.2. Power Management States (S0 to S3/S4 to S0) ..................................................................... 24

24

2.2.3. Power Down ............................................................................................................................ 25

25

2.3. WAKE# Signal ...............................................................................................................27

26

2.4. ACTIVITY# (Required) ..................................................................................................30

27

2.5. DualPortEn# (Optional) .................................................................................................30

28

2.6. SMBus (Optional) ..........................................................................................................30

29

2.6.1. Capacitive Load of High-power SMBus Lines ......................................................................... 31

30

2.6.2. Minimum Current Sinking Requirements for SMBus Devices ................................................. 31

31

2.6.3. SMBus Back Powering Considerations ................................................................................... 31

32

2.6.4. Power-on Reset ....................................................................................................................... 31

33

2.7. CLKREQ# (Optional) .....................................................................................................32

34

2.8. PWRDIS (Optional) .......................................................................................................32

35

2.9. Auxiliary Signal Parametric Specifications .....................................................................33

36

2.9.1. DC Specifications .................................................................................................................... 33

37

2.9.2. AC Specifications .................................................................................................................... 34

38

2.9.3. PWRDIS Electrical Characteristics .......................................................................................... 35

39

PCI Express SFF-8639 Module

PCI Express SFF-8639 Module | 5

3. Hot Insertion and Removal ................................................................................... 36

40

3.1. Scope 36

41

3.2. Hot Removal Detection ..................................................................................................36

42

3.2.1. Hot Insertion Detection ............................................................................................................ 37

43

4. Electrical Requirements ........................................................................................ 38

44

4.1. Power Supply Requirements .........................................................................................38

45

4.2. Power Supply Sequencing .............................................................................................39

46

4.3. Power Supply Decoupling..............................................................................................40

47

4.4. Electrical Topologies and Link Definitions ......................................................................40

48

4.4.1. Topologies ............................................................................................................................... 40

49

4.4.2. Link Definition .......................................................................................................................... 42

50

4.5. Electrical Budgets ..........................................................................................................43

51

4.5.1. AC-Coupling Capacitors .......................................................................................................... 43

52

4.5.2. Insertion Loss Values (Voltage Transfer Function) ................................................................. 43

53

4.5.3. Jitter Values ............................................................................................................................. 44

54

4.5.4. Crosstalk .................................................................................................................................. 46

55

4.5.5. Lane-to-Lane Skew ................................................................................................................. 47

56

4.5.6. Transmitter Equalization .......................................................................................................... 47

57

4.5.7. Skew within the Differential Pair .............................................................................................. 47

58

4.5.8. Differential Data Trace Impedance .......................................................................................... 48

59

4.5.9. Differential Data Trace Propagation Delay .............................................................................. 48

60

4.6. Eye Diagrams at the SFF-8639 Interface .......................................................................48

61

4.6.1. SFF-8639 Module Transmitter Path Compliance Eye Diagram at 2.5 GT/s ........................... 49

62

4.6.2. SFF-8639 Module Transmitter Path Compliance Eye Diagrams at 5.0 GT/s ......................... 50

63

4.6.3. SFF-8639 Module Transmitter Path Compliance Eye Diagrams at 8.0 GT/s ......................... 52

64

4.6.4. SFF-8639 Module Minimum Receiver Path Sensitivity Requirements at 2.5 GT/s ................. 53

65

4.6.5. SFF-8639 Module Minimum Receiver Path Sensitivity Requirements at 5.0 GT/s ................. 54

66

4.6.6. SFF-8639 Module Minimum Receiver Path Sensitivity Requirements at 8.0 GT/s ................. 55

67

4.6.7. SFF-8639 System Transmitter Path Compliance Eye Diagram at 2.5 GT/s ........................... 58

68

4.6.8. SFF-8639 System Transmitter Path Compliance Eye Diagram at 5.0 GT/s ........................... 59

69

4.6.9. SFF-8639 System Transmitter Path Compliance Eye Diagram at 8.0 GT/s ........................... 62

70

4.6.10. SFF-8639 System Minimum Receiver Path Sensitivity Requirements at 2.5 GT/s ................ 65

71

4.6.11. SFF-8639 System Minimum Receiver Path Sensitivity Requirements at 5.0 GT/s ................ 66

72

4.6.12. SFF-8639 System Minimum Receiver Path Sensitivity Requirements at 8.0 GT/s ................ 68

73

5. SFF-8639 Connector Specification ....................................................................... 70

74

5.1. Connector Pinout ...........................................................................................................70

75

5.2. Signal Integrity Requirements and Test Procedures ......................................................74

76

5.2.1. Signal Integrity Requirements ................................................................................................. 74

77

5.2.2. Signal Integrity Requirements and Test Procedures for 8.0 GT/s Support ............................. 74

78

5.2.2.1. Test Fixture Requirements ................................................................................................ 76

79

剩余81页未读,继续阅读

xg7zyj

- 粉丝: 3

- 资源: 5

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论1