没有合适的资源?快使用搜索试试~ 我知道了~

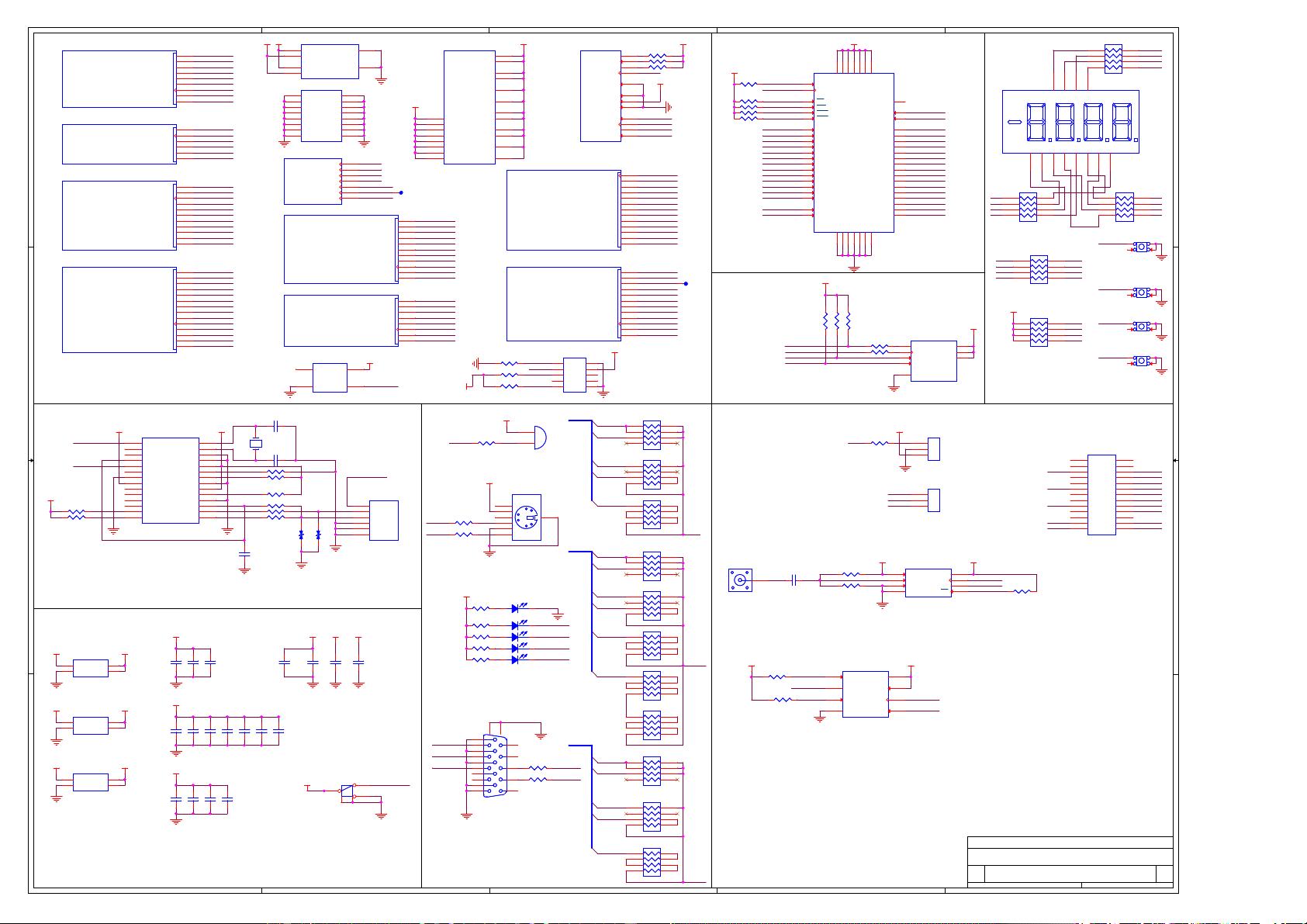

首页cyclone_IV原理图

资源详情

资源评论

资源推荐

A

A

B

B

C

C

D

D

E

E

4 4

3 3

2 2

1 1

SDRAM

FPGA&CLOCK

AD&SPI&IrDA

USB_UART

POWER&SWITCH

LED&BELL

FPGA FLASH

EXT FUNCTION

0.5K

1K

2K

4K

8K

0.5K

1K

2K

4K

8K

0.5K

1K

2K

4K

8K

PS2&VGA

数码管&KEY

16K

SDRAM_DQ12

V_G3

SDRAM_CS_N

SDRAM_A10

SDRAM_A2

SDRAM_A3

txd

V_B1

V_B2

V_B3

DS_C

DS_DP

SDRAM_CAS_N

SDRAM_RAS_N

EPCS_ASDI

EPCS_nCS

EPCS_DATA

SDRAM_DQ13

SDRAM_DQ10

SDRAM_DQ9

SDRAM_DQ8

SDRAM_DQMH

SDRAM_CLK

SDRAM_A11

SDRAM_A9

SDRAM_A7

SDRAM_A6

SDRAM_A5

SDRAM_A4

SDRAM_DQ11

DS_B

SDRAM_DQ15

SDRAM_DQ14

FLASH_DI

SDRAM_CKE

V_G0

V_G1

V_G2

V_G4

V_G5

V_R0

V_R1

V_R2

V_R3

V_R4

ADCLK

DS_A

ADDAT

ADCSN

IRDA

DS_EN1

DS_EN3

DS_EN2

DS_EN4

DS_F

DS_D

DS_E

FLASH_CLK

SDRAM_A12

SDRAM_A8

V_B4

SDRAM_BA0

SDRAM_BA1

SDRAM_A0

SDRAM_A1

BP1

rxd

PS2_DAT

PS2_CLK

H_SYNC

V_SYNC

V_B0

SDRAM_DQ7

SDRAM_DQ6

SDRAM_DQ5

SDRAM_DQ4

SDRAM_DQ2

SDRAM_DQ3

SDRAM_DQ0

SDRAM_DQ1

SDRAM_DQML

SDRAM_WE_N

FLASH_CS

DS_G

EPCS_ASDI

EPCS_nCS

F_TCK

F_TMS

F_TDI

F_TDO

EP_DCLK

F_TMS

F_TCK

F_TDO

F_TDI

EP_DCLK

CLK

CLK

SDRAM_CKE

EPCS_DATA

SDRAM_CLK

SDRAM_A0

SDRAM_A1

SDRAM_A2

SDRAM_A3

SDRAM_A4

SDRAM_A5

SDRAM_A6

SDRAM_A7

SDRAM_A8

SDRAM_A9

SDRAM_A10

SDRAM_A11

SDRAM_A12

SDRAM_BA0

SDRAM_BA1

SDRAM_DQ0

SDRAM_DQ1

SDRAM_DQ2

SDRAM_DQ3

SDRAM_DQ4

SDRAM_DQ5

SDRAM_DQ6

SDRAM_DQ7

SDRAM_DQ8

SDRAM_DQ9

SDRAM_DQ10

SDRAM_DQ11

SDRAM_DQ12

SDRAM_DQ14

SDRAM_DQ15

SDRAM_DQ13

SDRAM_DQML

SDRAM_DQMH

SDRAM_CS_n

SDRAM_WE_n

SDRAM_CAS_n

SDRAM_RAS_n

TXD

RXD

+5V_USB

BP1

DS_DP

DS_G

DS_C

PS2_DAT

PS2_CLK

GREEN

BLUE

V_R[4:0]

V_R4

V_R3

V_R2

V_R0

V_R1

RED

V_G5

V_G4

V_G3

V_G1

V_G2

GREEN

V_B4

V_B3

V_B2

V_B0

V_B1

BLUE

H_SYNC

V_SYNC

RED

DS_EN4

DS_EN2

DS_EN1

DS_EN3

DS_DP

DS_G

DS_D

DS_C

+5V_USB

uKEY2

Key3

uKEY1

RSTn

RSTn Key4

Key3

Key2

Key1

uKEY3

uKEY3

uKEY2

uKEY1

RSTn

uKEY3

uKEY2

uKEY1

DS_F

DS_B

DS_E

DS_A

BLUE

V_G0

Key4

ADCLK

ADDAT

ADCSn

FLASH_CLK

FLASH_DI

FLASH_CS

FLASH_DO

FLASH_WP

Key1

Key2

V_B[4:0]

tmp1

FLASH_DO

DS_D

A_IN

GREEN

A_IN

GND

IrDA

V_G[5:0]

+3.3V+5V

BP1

SDRAM_A3

SDRAM_A2

SDRAM_A1

SDRAM_A0

SDRAM_A10

SDRAM_BA1

SDRAM_BA0

gnd

gnd

gnd

gnd SDRAM_CS_N

+3.3V

+5V +3.3V

+1.2V

+2.5V+5V

+5V

+3.3V

+5V +3.3V +2.5V +1.2V

+3.3V

+2.5V

+2.5V

+2.5V

+2.5V

+3.3V

+3.3V

+1.2V

+3.3V

+5V+5V

+5V

+1.2V

+3.3V

+3.3V

+3.3V

+5V_USB

+3.3V

+5V

+5V

+3.3V +3.3V

+3.3V

+3.3V+3.3V

+2.5V

Title

Size Document Number Rev

Date: Sheet of

<Doc>

1.20

<Title>

C

1 1Thursday, August 01, 2013

Title

Size Document Number Rev

Date: Sheet of

<Doc>

1.20

<Title>

C

1 1Thursday, August 01, 2013

Title

Size Document Number Rev

Date: Sheet of

<Doc>

1.20

<Title>

C

1 1Thursday, August 01, 2013

C18

0.1u

C18

0.1u

U7

EPCS4SI8N

U7

EPCS4SI8N

nCS

1

DATA

2

VCC

3

GND

4

ASDI

5

DCLK

6

VCC

7

VCC

8

R3922R3922

R301KR301K

RP4

1K

RP4

1K

1

2

3

4 5

6

7

8

RP16

2K

RP16

2K

1

2

3

4 5

6

7

8

U2

PL2303

U2

PL2303

TXD

1

DTR_N

2

RTS_N

3

VDD_232

4

RXD

5

RL_N

6

GND

7

VDD

8

DSR_N

9

DCD_N

10

CTS_N

11

SHTD_N

12

EE_CLK

13

EE_DATA

14

DP

15

DM

16

VDD_3V3

17

GND_3V3

18

RESET

19

VDD

20

GND

21

TRI_STATE

22

LD_MODE

23

VDD_PLL

24

GND_PLL

25

PLL_TEST

26

OSC1

27

OSC2

28

J3

CON26A

J3

CON26A

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

C12

0.1u

C12

0.1u

R23

4.7k

R23

4.7k

R18

4.7k

R18

4.7k

U1M

EP4CE10E22C8

U1M

EP4CE10E22C8

GNDA1

36

GNDA2

108

VCCA1

35

VCCA2

107

VCCD_PLL1

37

VCCD_PLL2

109

C17

0.1u

C17

0.1u

R40

4.7K

R40

4.7K

RP10

1K

RP10

1K

1

2

3

4 5

6

7

8

C14

0.1u

C14

0.1u

BANK 1

U1A

EP4CE10E22C8

BANK 1

U1A

EP4CE10E22C8

IO_1

1

IO_2

2

IO_3

3

IO, DIFFIO_L1n, (DATA1,ASDO)

6

IO, VREFB1N0

7

IO, DIFFIO_L2p, (FLASH_nCE,nCSO)

8

IO, DIFFIO_L4p, (DQS0L/CQ1L,DPCLK0)

10

IO, DIFFIO_L4n

11

IO, (DATA0)

13

D5D5

RP1

1K

RP1

1K

1

2

3

4 5

6

7

8

D1D1

J16J16

11

12

13

14

15

1

2

3

4

5

6

7

8

9

17

16

10

R4 4.7kR4 4.7k

RP15

2K

RP15

2K

1

2

3

4 5

6

7

8

R291KR291K

R35 100R35 100

G2

OSC

G2

OSC

NC

1

GND

2

VCC

4

CLK

3

J15

PS2-6PIN_1

J15

PS2-6PIN_1

1

2

3

4

5

6

S

C6

10u

C6

10u

D4D4

VD2VD2

R2

4.7k

R2

4.7k

R16

25

R16

25

R13

4.7k

R13

4.7k

BANK 5

U1E

EP4CE10E22C8

BANK 5

U1E

EP4CE10E22C8

IO_73

73

IO_74

74

IO_75

75

IO, RUP3

76

IO, RDN3

77

IO, VREFB5N0

80

IO_83

83

IO, DIFFIO_R8n

84

IO, DIFFIO_R8p, (DQS1R/CQ1R#,DPCLK4)

85

IO, DIFFIO_R7n, (DEV_OE)

86

IO, DIFFIO_R7p, (DEV_CLRn)

87

RP3

2K

RP3

2K

1

2

3

4 5

6

7

8

C5

10u

C5

10u

R7 4.7kR7 4.7k

U8

TLC549C

U8

TLC549C

REF+

1

ANAIN

2

REF-

3

GND

4

CS

5

DOUT

6

I/OCLK

7

VCC

8

R12

4.7k

R12

4.7k

R19

4.7k

R19

4.7k

BANK 7

U1G

EP4CE10E22C8

BANK 7

U1G

EP4CE10E22C8

IO, DIFFIO_T20p, (DQS0T/CQ1T,DPCLK6)

110

IO, DIFFIO_T19p

111

IO, PLL2_CLKOUTn

112

IO, PLL2_CLKOUTp

113

IO, RUP4, (DQ1T)

114

IO, RDN4, (DQ1T)

115

IO, VREFB7N0

119

IO, DIFFIO_T16n, (DQ1T)

120

IO, DIFFIO_T16p

121

IO, DIFFIO_T13p

124

IO_125

125

IO, DIFFIO_T12n

126

IO, DIFFIO_T12p

127

C3

20p

C3

20p RP2

2K

RP2

2K

1

2

3

4 5

6

7

8

TP1

TP-S40

TP1

TP-S40

R281KR281K D3D3

C15

0.1u

C15

0.1u

BANK 4

U1D

EP4CE10E22C8

BANK 4

U1D

EP4CE10E22C8

IO, DIFFIO_B12p

54

IO, DIFFIO_B12n

55

IO, DIFFIO_B15p, (DQ1B)

58

IO, DIFFIO_B16p, (DQ1B)

59

IO, DIFFIO_B16n, (DQ1B)

60

IO_64

64

IO, VREFB4N0

65

IO, RUP2, (DQ1B)

66

IO, RDN2, (DQ1B)

67

IO, DIFFIO_B20n, (DQS0B/CQ1B,DPCLK3)

68

IO_69

69

IO, DIFFIO_B21p

70

IO, DIFFIO_B21n

71

IO, DIFFIO_B22p

72

S4

SWPB

S4

SWPB

1 3

42

R3822R3822

U6

MT48LC16M16A2TG-75

U6

MT48LC16M16A2TG-75

VDD

1

DQ0

2

VDDQ

3

DQ1

4

DQ2

5

VSSQ

6

DQ3

7

DQ4

8

VDDQ

9

DQ5

10

DQ6

11

VSSQ

12

DQ7

13

VDD

14

DQML

15

WE

16

CAS

17

RAS

18

CS

19

BA0

20

BA1

21

A10

22

A0

23

A1

24

A2

25

A3

26

VDD

27

VSS

28

A4

29

A5

30

A6

31

A7

32

A8

33

A9

34

A11

35

A12

36

CKE

37

CLK

38

DQMH

39

NC

40

VSS

41

DQ8

42

VDDQ

43

DQ9

44

DQ10

45

VSSQ

46

DQ11

47

DQ12

48

VDDQ

49

DQ13

50

DQ14

51

VSSQ

52

DQ15

53

VSS

54

R5 4.7kR5 4.7k

RP11

1K

RP11

1K

1

2

3

4 5

6

7

8

R31

4.7K

R31

4.7K

R8 4.7kR8 4.7k

C8

10u

C8

10u

R37

4.7k

R37

4.7k

R1

4.7k

R1

4.7k

C2

10u

C2

10u

R32

100

R32

100

SW1SW1

BANK 6

U1F

EP4CE10E22C8

BANK 6

U1F

EP4CE10E22C8

IO, DIFFIO_R4n, (INIT_DONE)

98

IO, DIFFIO_R4p, (CRC_ERROR)

99

IO_100

100

IO, DIFFIO_R3n, (nCEO)

101

IO, DIFFIO_R3p, (CLKUSR)

103

IO, (DQS0R/CQ1R,DPCLK5)

104

IO, VREFB6N0

105

IO, DIFFIO_R1n

106

R22

27

R22

27

S3

SWPB

S3

SWPB

1 3

42

D2D2

U1I

EP4CE10E22C8

U1I

EP4CE10E22C8

CLK1, DIFFCLK_0n

23

CLK2, DIFFCLK_1p

24

CLK3, DIFFCLK_1n

25

CLK4, DIFFCLK_2p

91

CLK5, DIFFCLK_2n

90

CLK6, DIFFCLK_3p

89

CLK7, DIFFCLK_3n

88

BANK 8

U1H

EP4CE10E22C8

BANK 8

U1H

EP4CE10E22C8

IO, DIFFIO_T11n

128

IO, DIFFIO_T11p

129

IO, DIFFIO_T10n, (DATA2), (DQ1T)

132

IO, DIFFIO_T10p, (DATA3), (DQ1T)

133

IO, DIFFIO_T8n, (DQ1T)

135

IO, VREFB8N0

136

IO, (DATA5), (DQ1T)

137

IO, (DATA6)

138

IO, DIFFIO_T5p

141

IO, DIFFIO_T2p, (DQS1T/CQ1T#,DPCLK7)

142

IO, DIFFIO_T1n, (DQ1T)

143

IO, DIFFIO_T1p, (DM1T)

144

S2

SWPB

S2

SWPB

1 3

42

R24

27

R24

27

U9

W25Q32

U9

W25Q32

nCS

1

DO

2

nWP

3

GND

4

DI

5

CLK

6

nHold

7

VCC

8

LS1LS1

RP9

2K

RP9

2K

1

2

3

4 5

6

7

8

RP6

2K

RP6

2K

1

2

3

4 5

6

7

8

a

g

d

b

c

f

e

a

g

d

b

c

f

e

dp1

12

D

2

E

1

C

4

F

10

dp3

8

dp2

9

G

5

dp4

6

B

7

A

11

DP

3

RP14

1K

RP14

1K

1

2

3

4 5

6

7

8

R3

4.7k

R3

4.7k

U4

1117

U4

1117

GND

1

IN

3

OUT

2

OUT

4

S1

SWPB

S1

SWPB

1 3

42

R104.7kR104.7k

BANK 3

U1C

EP4CE10E22C8

BANK 3

U1C

EP4CE10E22C8

IO, DIFFIO_B1p

38

IO, DIFFIO_B1n

39

IO, (DQS1B/CQ1B#,DPCLK2)

42

IO, PLL1_CLKOUTp

43

IO, PLL1_CLKOUTn

44

IO, VREFB3N0

46

IO, DIFFIO_B9p, (DQ1B)

49

IO, DIFFIO_B9n, (DQ1B)

50

IO, DIFFIO_B10p, (DQ1B)

51

IO, DIFFIO_B11p

52

IO, DIFFIO_B11n

53

C1

20p

C1

20p

RP13

1K

RP13

1K

1

2

3

4 5

6

7

8

G1G1

R36 100R36 100

U3

1117

U3

1117

GND

1

IN

3

OUT

2

OUT

4

C21

0.1u

C21

0.1u

C7

10u

C7

10u

R261KR261K

R27 100R27 100

C16

0.1u

C16

0.1u

D6

CON3

D6

CON3

1

2

3

C22

0.1u

C22

0.1u

RP12

1K

RP12

1K

1

2

3

4 5

6

7

8

C20

0.1u

C20

0.1u

U1K

EP4CE10E22C8

U1K

EP4CE10E22C8

VCCINT

5

VCCINT

29

VCCINT

45

VCCINT

61

VCCINT

78

VCCINT

102

VCCINT

116

VCCINT

134

VCCIO1

17

VCCIO2

26

VCCIO3

40

VCCIO3

47

VCCIO4

56

VCCIO4

62

VCCIO5

81

VCCIO6

93

VCCIO7

117

VCCIO7

122

VCCIO8

130

VCCIO8

139

C4

0.1u

C4

0.1u

C10

10u

C10

10u

R251KR251K

J17

COAX_CONN

J17

COAX_CONN

1

C9

10u

C9

10u

R34

4.7K

R34

4.7K

VD1VD1

C19

0.1u

C19

0.1u

J1

Header 5X2

J1

Header 5X2

1 2

3 4

5 6

7 8

9 10

U1J

EP4CE10E22C8

U1J

EP4CE10E22C8

TDI

15

TDO

20

TCK

16

TMS

18

MSEL0

94

MSEL1

96

MSEL2

97

nCE

21

DCLK

12

CONF_DONE

92

nCONFIG

14

nSTATUS

9

C13

0.1u

C13

0.1u

J4J4

VBUS

1

D-

2

D+

3

GND

4

SHIELD

5

SHIELD

6

R9 4.7kR9 4.7k

R114.7kR114.7k

C11

0.1u

C11

0.1u

RP8

2K

RP8

2K

1

2

3

4 5

6

7

8

U1L

EP4CE10E22C8

U1L

EP4CE10E22C8

GND

19

GND

27

GND

41

GND

48

GND

57

GND

63

GND

82

GND

95

GND

118

GND

123

GND

131

GND

140

GND

4

GND

22

GND

79

TGND

145

TP2

TP-S40

TP2

TP-S40

R6 4.7kR6 4.7k

R20

1.5k

R20

1.5k

D8

CON3

D8

CON3

1

2

3

RP7

1K

RP7

1K

1

2

3

4 5

6

7

8

R15

25

R15

25

U5

1117

U5

1117

GND

1

IN

3

OUT

2

OUT

4

R33 100R33 100

R21

4.7k

R21

4.7k

R17

100

R17

100

R14

4.7k

R14

4.7k

RP5

2K

RP5

2K

1

2

3

4 5

6

7

8

BANK 2

U1B

EP4CE10E22C8

BANK 2

U1B

EP4CE10E22C8

IO, DIFFIO_L6n

28

IO, DIFFIO_L8p, (DQS1L/CQ1L#,DPCLK1)

30

IO, VREFB2N0

31

IO, RUP1

32

IO, RDN1

33

IO_34

34

zesd003

- 粉丝: 2

- 资源: 11

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- stc12c5a60s2 例程

- Android通过全局变量传递数据

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论2