没有合适的资源?快使用搜索试试~ 我知道了~

首页ASIC 设计-FPGA 原型验证

ASIC 设计-FPGA 原型验证

工程学习文档,很实用,很好的资料,不是本人资料,但是阅读了3遍,结合实际项目很有帮助!

资源详情

资源评论

资源推荐

Goke Microelectronics

I

ASIC 设计-FPGA 原型验证

版本

修改内容

修改人

时间

1.0

2014.07

1.1

2014.09

ASIC Design Team

ASIC 设计-FPGA 原型验证

II

目录

1 ASIC 验证技术 ...................................................................................................... 1

1.1 ASIC 设计流程 ............................................... 1

1.2 FPGA 验证技术 ............................................... 3

1.3 Altera 与 Xilinx 工具对比 .................................... 3

1.4 VHDL 与 Verilog 对比 ......................................... 5

1.5 Verilog 良好编程习惯 ........................................ 6

2 基于 ALTERA 的 ASIC 验证 ................................................................................. 9

2.1 Stratix IV FPGA 资源与架构 .................................. 9

2.2 QuartusII 设计工具 ......................................... 10

2.3 ASIC 设计转换 .............................................. 11

2.3.1 PLL 设计 ............................................................................................ 11

2.3.1 RAM 设计 .......................................................................................... 16

2.4 时序约束 ................................................... 19

2.4.1 QSF&Tcl ............................................................................................. 22

2.4.2 LogicLock ........................................................................................... 23

2.5 综合布局布线 ............................................... 23

2.5.1 综合设置 ............................................................................................. 24

2.5.2 增量编译 ............................................................................................. 25

2.5.3 VQM & QXP ...................................................................................... 30

2.5.4 时序分析 ............................................................................................ 30

2.6 下载设计文件 ............................................... 32

2.7 Debug ...................................................... 32

2.7.1 In-System Memory Content Editor ..................................................... 33

2.7.2 ChipPlanner ......................................................................................... 34

2.7.3 SignalTapII .......................................................................................... 38

2.7.4 Keep Signals ....................................................................................... 43

2.8 Example 工程 ............................................... 45

3 基于 XILINX 的 ASIC 验证 ................................................................................. 49

3.1 Vertex-7 FPGA 资源与架构 ................................... 49

3.2 设计工具 ISE 与 Vivado ...................................... 49

3.3 ASIC 设计转换 .............................................. 54

3.3.1 时钟资源 ............................................................................................ 54

3.3.2 PLL 设计 ............................................................................................ 58

3.3.3 RAM 设计 .......................................................................................... 61

Goke Microelectronics

III

3.4 时序约束 ................................................... 64

3.5 综合布局布线 ............................................... 70

3.5.1 Blackbox ............................................................................................. 70

3.5.2 Keep Signals ....................................................................................... 71

3.5.3 Strategies ............................................................................................. 72

3.5.4 Incremental Compile ........................................................................... 75

3.5.5 时序分析 ............................................................................................ 77

3.5.6 Generate Bitstream .............................................................................. 81

3.6 下载设计文件 ............................................... 84

3.6.1 下载 bit 文件 ..................................................................................... 84

3.6.2 下载 mcs 文件 ................................................................................... 87

3.7 Debug ...................................................... 88

3.8 Example 工程 ............................................... 94

3.8.1 导入 ISE & Synplify 工程 ................................................................. 94

3.8.2 Working with Tcl ................................................................................. 95

3.9 Gate Clock 处理 ............................................ 99

3.10 多片 FPGA 验证 ............................................ 101

4 DDR 相关技术 .................................................................................................... 104

4.1 DDR Controller ............................................ 108

4.2 DDR PHY ................................................... 111

4.2.1 Altera PHY ........................................................................................ 111

4.2.2 Xilinx PHY ....................................................................................... 113

5 硬件技术 .............................................................................................................. 117

5.1 PCB 设计注意事项 .......................................... 117

5.2 电磁兼容与信号完整性 ...................................... 117

5.2.1 端接匹配 .......................................................................................... 118

5.2.2 防止地弹 .......................................................................................... 118

5.2.3 减小串扰 .......................................................................................... 118

5.2.4 降低电磁干扰 .................................................................................. 119

5.3 FPGA 开发板使用注意事项 ................................... 120

总结 ............................................................................................................................ 121

Goke Microelectronics

1

1 ASIC 验证技术

1.1 ASIC 设计流程

ASIC 分为全定制和半定制。全定制设计需要设计者完成所有电路的设计,

因此需要大量人力物力,灵活性好但开发效率低下。如果设计较为理想,全定制

能够比半定制的 ASIC 芯片运行速度更快。半定制使用库里的标准逻辑单元

(Standard Cell),设计时可以从标准逻辑单元库中选择 SSI、MSI、数据通路、存

储器甚至系统级模块(如乘法器、微控制器等)和 IP 核,这些逻辑单元已经布局完

毕,而且设计得较为可靠,设计者可以较方便地完成系统设计。现代 ASIC 常包

含处理器,类似 ROM、RAM、EEPROM、Flash 的存储单元和其他模块. 这样的

ASIC 常被称为 SoC(片上系统)。

由于 SoC 设计复杂度不断增加,使得缩短面市时间的压力越来越重。虽然充

分利用 IP 核大大减少了 SoC 的设计时间,但 SoC 验证仍然非常复杂耗时。 SoC

和 ASIC 的最大不同之处在于它的系统特性,除了大量硬件模块之外,SoC 还需要

大量的固件和软件,如操作系统、驱动程序、通讯协议以及应用程序 等。这使得

传统的软件仿真工具已经无法完全解决验证的问题。而且随着越来越多的需要处

理大量实时数据的应用(如视频)出现,验证技术就要求能够在接近实时频率的

条件下进行验证。现在越来越多的 ASIC 设计者自己设计 FPGA 验证板来进行

ASIC 设计验证。用 FPGA 验证 ASIC 的好处是可以使软件的开发调试和 ASIC

的开发调试并行的进行。

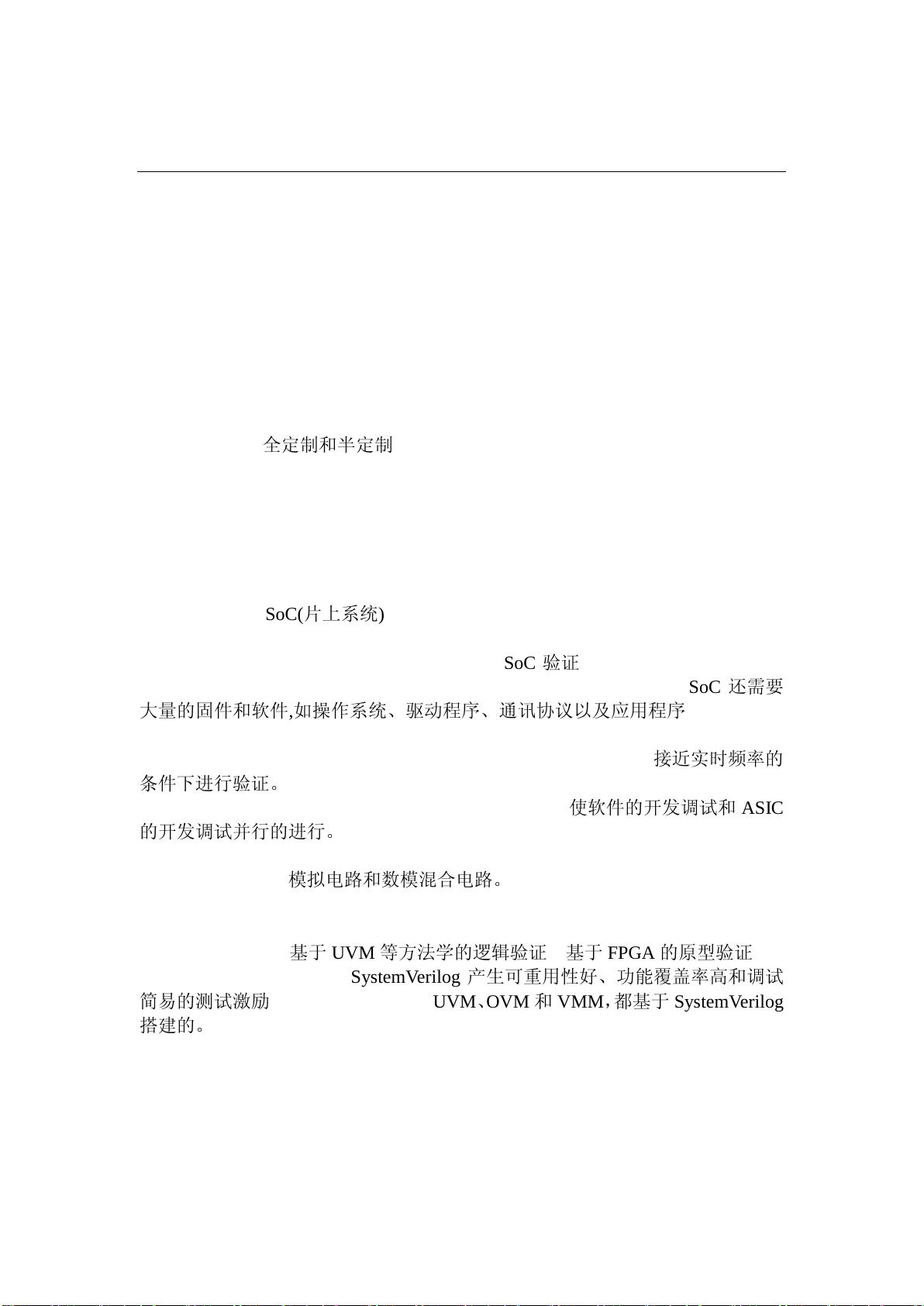

图 1-1 为典型的半定制设计流程,一般用来设计数字 IC 电路。全定制的设

计,一般用于设计模拟电路和数模混合电路。

本文主要讨论设计流程中的仿真验证,RTL 仿真工具一般用到的有 Cadence

的 NC-verilog,Synopsys 的 VCS 和 Mentor 的 ModelSim。

RTL 验证包括基于 UVM 等方法学的逻辑验证和基于 FPGA 的原型验证。基

于方法学的验证主要使用 SystemVerilog 产生可重用性好、功能覆盖率高和调试

简易的测试激励。常见的验证平台有 UVM、OVM 和 VMM,都基于 SystemVerilog

搭建的。UVM 是在 OVM 和 VMM 基础上推出的验证方法学的新的标准。2006

年,Synopsys 公司推出了验证方法学手册(VMM),这个是 RVM 从 vera 语言过

度到 SystemVerilog 的方法学。2008 年,Cadence 公司和 Mentor 公司共同推出了

OVM。2010 年,ACCELLERA 采用了 OVM 作为基础,推出了 UVM 验证方法

ASIC 设计-FPGA 原型验证

2

学。同时引入了 VMM 的一些概念,作为业界方法学统一的一个雏形。基于 FPGA

的原型验证,主要有基于 Altera 和 Xilinx 的 FPGA 验证平台。

需求分析

算法设计

架构设计

RTL设计

仿真验证

综合

门级验证

布局布线(P&R)

寄生参数提取

版图物理验证

Tapeout

芯片测试

设计流程

设计工具

Matlab C C++

SystemC C

C++

VHDL Verilog

VCS NC-Verilog ModelSim

SystemVerilog UVM FPGA

DesignCompiler

BuildGates

Formality

LEC

PrimeTime

Pearl

静态时序分析

Astro ICC

Encounter

Star-RCXT Assure-RCX

Calibre-xRC

Hercules

Dracula Calibre

图 1-1 数字 IC 设计流程

剩余123页未读,继续阅读

lhl_7713

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- stc12c5a60s2 例程

- Android通过全局变量传递数据

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论2