没有合适的资源?快使用搜索试试~ 我知道了~

首页AD9520芯片中文数据手册

AD9520芯片中文数据手册

AD9520芯片中文数据手册,文中详细介绍AD9520的使用,中文介绍哦!

资源详情

资源评论

资源推荐

AD9520-0

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademark

s are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2008 Analog Devices, Inc. All rights reserved.

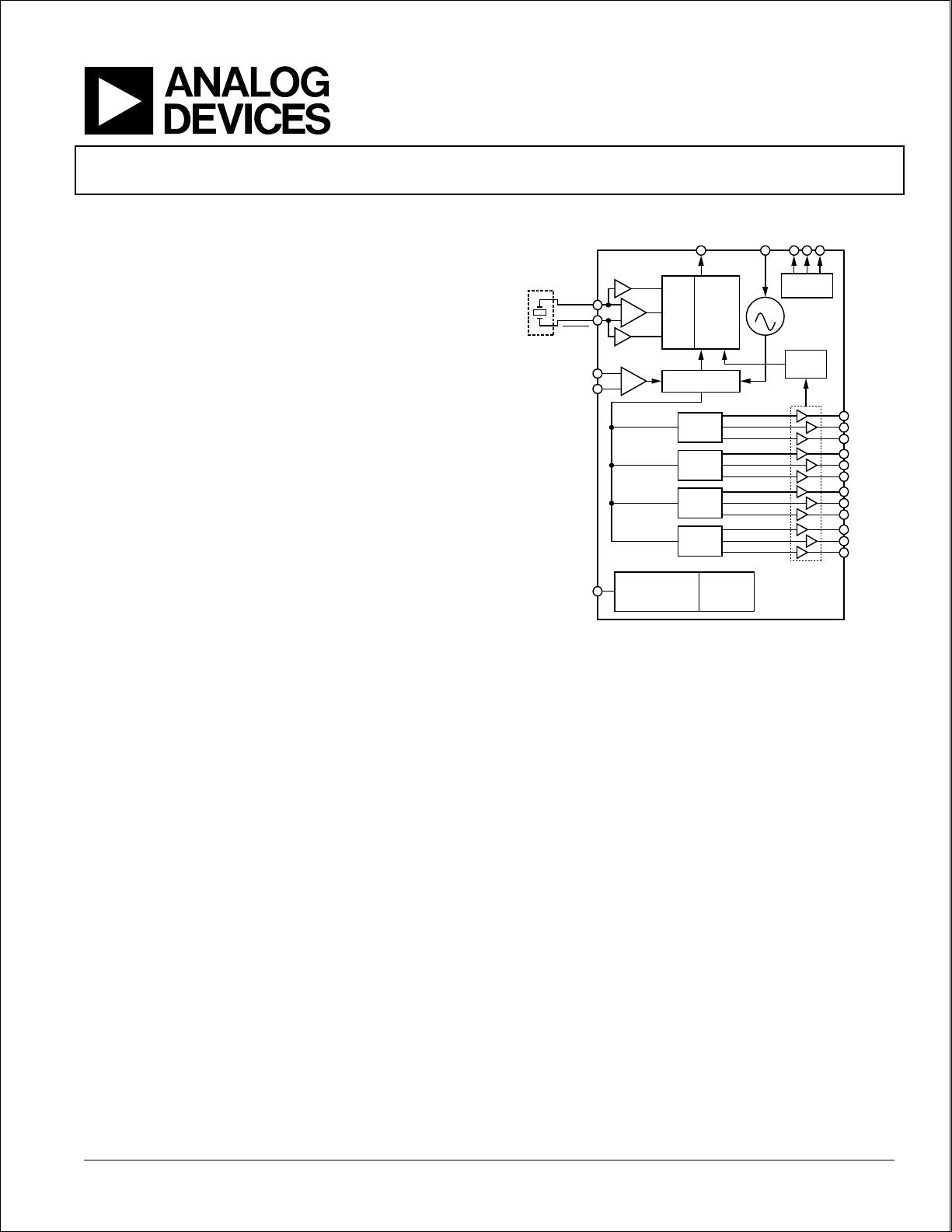

功能框图

OPTIONAL

REF1

REF2

CLK

LF

SWITCHOVER

AND MONITOR

PLL

DIVIDER

AND MUXES

ZERO

DELAY

CP

VCO

STATUS

MONITOR

SPI/I

2

C CONTROL

PORT AND

DIGITAL LOGIC

EEPROM

AD9520

OUT0

OUT1

OUT2

DIV/

Φ

OUT3

OUT4

OUT5

DIV/

Φ

OUT6

OUT7

OUT8

DIV/

Φ

OUT9

OUT10

OUT11

DIV/

Φ

LVPECL/

CMOS

REFIN

REFIN

07213-001

1

AD9520在本数据手册中泛指AD9520系列的所有器件。但是,使用AD9520-0时,它仅指AD9520系列的该特定器件。

12路LVPECL/24路CMOS输出时钟

发生器,集成2.8 GHz VCO

概述

AD9520-01提供多路输出时钟分配功能,具有亚皮秒级抖动

性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。

片内VCO的调谐频率范围为2.53 GHz至2.95 GHz。也可以使

用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

图1

AD9520串行接口支持SPI和I2C®端口。封装内EEPROM可

以通过串行接口进行编程,存储用于上电和芯片复位的用

户定义寄存器设置。

AD9520具有12路LVPECL输出,分为四组。任何一路1.6

GHz LVPECL输出都可以重新配置为两路250 MHz CMOS输

出。

每组输出具有一个分频器,其分频比(从1至32)和相位(粗

调延迟)均可以设置。

AD9520提供64引脚LFCSP封装,可以采用3.3 V单电源供电。

外部VCO的工作电压最高可达5.5 V。独立的输出驱动器电

源可以为2.375 V至3.465 V。

AD9520的额定工作温度范围为−40°C至+85°C标准工业温

度范围。

ADI中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI不对翻译中存在的差异或由此产生的错误负责。如需确认任何词语的准确性,请参考ADI提供

的最新英文版数据手册。

特性

低相位噪声锁相环(PLL)

片内VCO调谐范围:2.53 GHz至2.95 GHz

支持最高2.4 GHz的外部3.3 V/5 V VCO/VCXO

1路差分或2路单端参考输入

支持最高250 MHz的CMOS、LVDS或LVPECL参考

参考输入接受16.67 MHz至33.3 MHz晶振

可选参考时钟倍频器

参考监控功能

自动和手动参考切换/保持模式,支持可选的恢复式/非恢

复式切换

参考间无毛刺切换

从保持模式自动恢复

可选数字或模拟锁定检测

可选零延迟工作

12路1.6 GHz LVPECL输出分为4组

每组3路输出,具有一个带相位延迟的1至32分频器

加性输出抖动低至225 fs rms

分组输出的通道间偏斜:<16 ps

可以将每路LVPECL输出配置为2路CMOS输出(fOUT ≤ 250

MHz)

上电时所有输出自动同步

可以根据需要手动同步多路输出

SPI和I²C兼容型串行控制端口

64引脚LFCSP封装

非易失性EEPROM存储配置设置

应用

低抖动、低相位噪声时钟分配

SONET、10Ge、10G FC和其它10 Gbps协议的时钟产生和转换

前向纠错(G.710)

为高速ADC、DAC、DDS、DDC、DUC、MxFE提供时钟

高性能无线收发器

自动测试设备(ATE)和高性能仪器仪表

宽带基础设施

AD9520-0

Rev 0 | Page 2 of 84

目录

特性....................................................................................................1

应用....................................................................................................1

概述....................................................................................................1

功能框图...........................................................................................1

修订历史...........................................................................................3

技术规格...........................................................................................4

电源要求......................................................................................4

PLL特性 .......................................................................................4

时钟输入......................................................................................7

时钟输出......................................................................................7

时序特性......................................................................................8

时序图.....................................................................................9

时钟输出加性相位噪声(仅分配;

未使用VCO分频器) ............................................................... 10

时钟输出绝对相位噪声(使用内部VCO)........................... 11

时钟输出绝对时间抖动(使用内部VCO

的时钟产生).............................................................................11

时钟输出绝对时间抖动(使用内部

VCO的时钟净化).................................................................... 11

时钟输出绝对时间抖动(使用外部

VCXO的时钟产生).................................................................12

时钟输出加性时间抖动(未使用

VCO分频器) ............................................................................12

时钟输出加性时间抖动(使用VCO分频器) ......................13

串行控制端口—SPI模式 .......................................................13

串行控制端口—I

2

C模式 .......................................................14

PD, SYNC和RESET引脚........................................................15

串行端口设置引脚:SP1、SP0 ........................................... 15

LD、STATUS和REFMON引脚 ...........................................15

功耗 ...........................................................................................16

绝对最大额定值...........................................................................17

热阻 ...........................................................................................17

ESD警告....................................................................................17

引脚配置和功能描述 ..................................................................18

典型工作特性 ...............................................................................21

术语................................................................................................. 26

详细框图........................................................................................ 27

工作原理........................................................................................ 28

工作配置.........................................................................................28

模式0:内部VCO和时钟分配..............................................28

模式1:时钟分配或外部VCO <1600 MHz ........................30

模式2:高频时钟分配—CLK或外部

VCO > 1600 MHz .....................................................................32

锁相环(PLL) .............................................................................34

PLL配置 .....................................................................................34

鉴频鉴相器(PFD) ...................................................................34

电荷泵(CP) ...............................................................................35

片内VCO ...................................................................................35

PLL外部环路滤波器 ...............................................................35

PLL参考输入.............................................................................35

参考切换....................................................................................36

参考分频器R.............................................................................36

VCO/VCXO反馈分频器N:P、A、B、R.........................36

数字锁定检测(DLD) ..............................................................38

模拟锁定检测(ALD) ..............................................................38

电流源数字锁定检测(CSDLD) ............................................38

外部VCXO/VCO时钟输入(CLK/CLK) ..............................39

保持 ............................................................................................39

外部/手动保持模式.................................................................39

自动/内部保持模式.................................................................39

频率状态监控器.......................................................................41

VCO校准 ...................................................................................42

零延迟操作.....................................................................................43

内部零延迟模式.......................................................................43

外部零延迟模式.......................................................................43

时钟分配.........................................................................................44

工作模式....................................................................................44

CLK或VCO直接至LVPECL输出..........................................44

时钟分频....................................................................................45

VCO分频器...............................................................................45

通道分频器 ...............................................................................45

同步输出—SYNC功能............................................................47

LVPECL输出驱动器................................................................49

CMOS输出驱动器 ...................................................................49

AD9520-0

Rev. 0 | Page 3 of 84

修订历史

2008年9月—修订版0:初始版

复位模式....................................................................................... 49

上电复位.................................................................................. 49

通过RESET引脚进行硬件复位........................................... 49

通过串行端口进行软复位................................................... 50

通过串行端口软复位到EEPROM中

的设置(EEPROM引脚= 0时)............................................... 50

关断模式....................................................................................... 50

通过PD关断芯片 ................................................................... 50

PLL关断 ................................................................................... 50

分配关断.................................................................................. 50

各时钟输出独立关断............................................................50

各时钟通道独立关断............................................................50

串行控制端口 .............................................................................. 51

SPI/I

2

C端口选择 ....................................................................... 51

I

2

C串行端口操作...................................................................... 51

I

2

C总线特性 ............................................................................ 51

数据传输过程......................................................................... 52

数据传输格式......................................................................... 53

I

2

C串行端口时序 ................................................................... 53

SPI串行端口操作...................................................................... 54

引脚描述.................................................................................. 54

SPI工作模式............................................................................ 54

通信周期—指令加数据........................................................ 54

写操作 ...................................................................................... 54

读操作 ...................................................................................... 54

SPI指令字(16位) .................................................................. 55

SPI MSB/LSB优先传输........................................................ 55

EEPROM操作 ............................................................................ 58

写入EEPROM ....................................................................... 58

读取EEPROM ....................................................................... 58

EEPROM缓冲段编程.......................................................... 59

寄存器段定义组................................................................... 59

IO_UPDATE(操作代码0x80) ............................................ 59

End-of-Data(操作代码0xFF).............................................. 59

Pseudo-End-of-Data(操作代码0xFE) ............................... 59

热性能 ......................................................................................... 61

寄存器映射................................................................................. 62

寄存器映射描述........................................................................ 67

应用信息..................................................................................... 82

使用AD9520进行频率规划 ............................................... 82

在ADC时钟应用中使用AD9520输出.............................. 82

LVPECL时钟分配 ................................................................ 82

CMOS时钟分配.................................................................... 83

外形尺寸..................................................................................... 84

订购指南................................................................................ 84

AD9520-0

Rev. 0 | Page 4 of 84

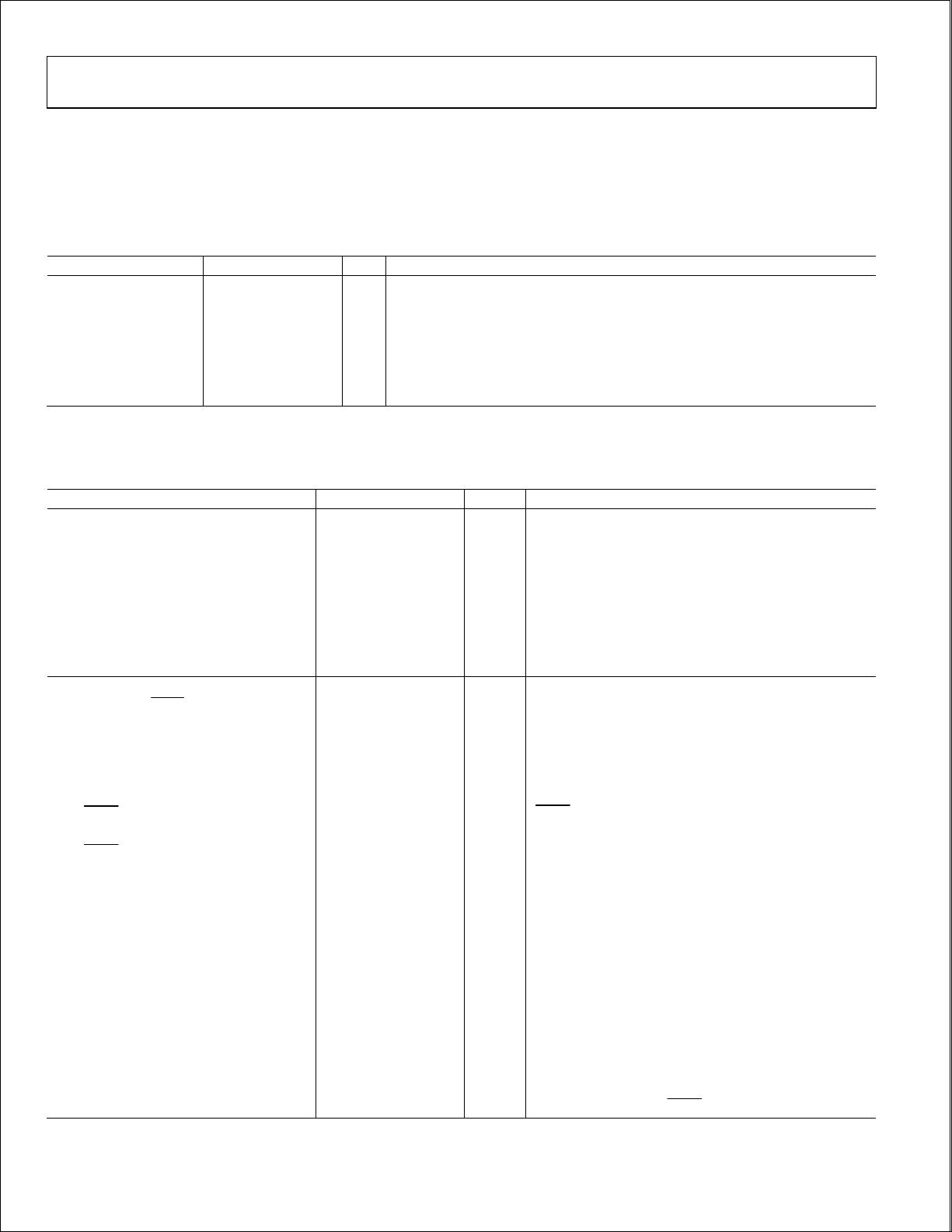

技术规格

电源要求

表1

最小值 典型值 最大值 单位

单位

测试条件/注释

测试条件/注释

VS 3.135 3.3 3.465 V 3.3 V ± 5%

VS_DRV 2.375 VS V 标称值为2.5 V至3.3 V ± 5%

VCP VS 5.25 V 标称值为3.3 V至5.0 V ± 5%

RSET引脚电阻 4.12 kΩ 设置内部偏置电流;接地

CPRSET引脚电阻 5.1 kΩ

设置内部电荷泵电流范围,标称值4.8 mA (CP_lsb = 600 μA);实际

电流计算如下:CP_lsb = 3.06/CPRSET;接地

BYPASS引脚电容 220 nF 内部LDO调节器的旁路电容;LDO稳定工作所必需的;接地

PLL特性

表2

2530 2950 MHz 见图13

52 MHz/V 见图8

VCP −

0.5

V 使用内部VCO时,VCP ≤ VS

1 MHz/V

−51 dBc/Hz f = 2550 MHz

−108 dBc/Hz f = 2550 MHz

−127 dBc/Hz f = 2550 MHz

参考输入

差模(REFIN、REFIN)

差分模式(让未驱动的输入交流接地,可以

支持单端输入)

输入频率 0 250 MHz

低于约1 MHz的频率应直流耦合;注意匹配

V

CM

(自偏置电压)

输入灵敏度 280 mV p-p

REFIN自偏置电压 1.34 1.60 1.75 V REFIN的自偏置电压

1

REFIN自偏置电压

1.30 1.50 1.60 V

REFIN的自偏置电压

1

REFIN输入电阻 4.0 4.8 5.9 kΩ 自偏置

1

REFIN输入电阻

4.4 5.3 6.4 kΩ 自偏置

1

双路单端模式(REF1、REF2) 两路单端CMOS兼容型输入

输入频率(交流耦合,直流偏移关闭)

10 250 MHz 压摆率必须大于50 V/μs

输入频率(交流耦合,直流偏移开启)

250 MHz

压摆率必须大于50 V/μs,并且必须满足输

入幅度灵敏度要求;见输入灵敏度

输入频率(直流耦合) 0 250 MHz 压摆率大于50 V/μs;CMOS电平

输入灵敏度(交流耦合,直流偏移关闭)

0.55 3.28 V p-p V

IH

不应超过V

S

输入灵敏度(交流耦合,直流偏移开启)

1.5 2.78 V p-p V

IH

不应超过V

S

输入逻辑高电平,直流偏移关闭 2.0 V

输入逻辑低电平,直流偏移关闭 0.8 V

输入电流 −100 +100 µA

输入电容 2 pF

除非另有说明,典型值的测量条件为:VS = VS_DRV = 3.3 V ± 5%;VS ≤ VCP ≤ 5.25 V;TA = 25°C;RSET = 4.12 kΩ;

CPRSET = 5.1 kΩ。最小值和最大值的测量条件为整个VS和TA(−40°C至+85°C)范围内。

最小值 典型值 最大值参数

VCO(片内)

频率范围

VCO增益(K

VCO

)

调谐电压(V

T

)

推频(开环)

1 kHz偏移时的相位噪声

100 kHz偏移时的相位噪声

1 MHz偏移时的相位噪声

各引脚,REFIN (REF1)/REFIN (REF2)

AD9520-0

Rev. 0 | Page 5 of 84

晶体振荡器

晶振频率范围 16.67 33.33 MHz

最大晶体动态电阻 30 Ω

鉴频鉴相器(PFD)

PFD输入频率 100 MHz 防反冲脉冲宽度 = 1.3 ns、2.9 ns

45 MHz 防反冲脉冲宽度 = 6.0 ns

参考输入时钟倍频器频率 0.004 50 MHz 防反冲脉冲宽度 = 1.3 ns、2.9 ns

防反冲脉冲宽度 1.3 ns 0x017[1:0] = 01b

2.9 ns 0x017[1:0] = 00b; 0x017[1:0] = 11b

6.0 ns 0x017[1:0] = 10b

电荷泵(CP)

I

CP

吸/源电流 可编程

高值 4.8 mA

CPRSET = 5.1 kΩ时;更改CPRSET可以获得更高的I

CP

低值 0.60 mA

绝对精度 2.5 % 电荷泵电压设置为V

CP

/2

0.5 V < V

CP

< VCP − 0.5 V

V

CP

= VCP/2 V

CPRSET范围 2.7 10 kΩ

I

CP

高阻抗模式漏电流 1 nA

吸电流与源电流匹配 1 %

0.5 V < VCP< VCP − 0.5 V;VCP为CP(电荷泵)引脚

上的电压;VCP为VCP电源引脚上的电压

1.5 %

I

CP

与温度 2 %

预分频器(N分频器的一部分)

预分频器输入频率

P = 1 FD 300 MHz

P = 2 FD 600 MHz

P = 3 FD 900 MHz

P = 2 DM (2/3) 600 MHz

P = 4 DM (4/5) 1000 MHz

P = 8 DM (8/9) 2400 MHz

P = 16 DM (16/17) 3000 MHz

P = 32 DM (32/33) 3000 MHz

预分频器输出频率 300 MHz

PLL N分频器延迟

000 O

001 410 ps

010 530 ps

011 650 ps

100 770 ps

101 890 ps

110 1010 ps

111 1130 ps

PLL R分频器延迟

000 O

001 370 ps

010 490 ps

011 610 ps

100 730 ps

101 850 ps

110 970 ps

111 1090 ps

最小值 典型值 最大值 单位 测试条件/注释

参数

I

CP

与V

CP

寄存器0x019[5:3];见表53

寄存器0x019[2:0];见表53

CPRSET = 5.1 kΩ时;更改CPRSET可以获得更低的I

CP

A、B计数器输入频率(预分频器输入频率除以P)

剩余83页未读,继续阅读

u010592589

- 粉丝: 1

- 资源: 5

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 27页智慧街道信息化建设综合解决方案.pptx

- 计算机二级Ms-Office选择题汇总.doc

- 单链表的插入和删除实验报告 (2).docx

- 单链表的插入和删除实验报告.pdf

- 物联网智能终端项目设备管理方案.pdf

- 如何打造品牌的模式.doc

- 样式控制与页面布局.pdf

- 武汉理工Java实验报告(二).docx

- 2021线上新品消费趋势报告.pdf

- 第3章 Matlab中的矩阵及其运算.docx

- 基于Web的人力资源管理系统的必要性和可行性.doc

- 基于一阶倒立摆的matlab仿真实验.doc

- 速运公司物流管理模式研究教材

- 大数据与管理.pptx

- 单片机课程设计之步进电机.doc

- 大数据与数据挖掘.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论2