没有合适的资源?快使用搜索试试~ 我知道了~

首页ug902-vivado-high-level-synthesis.pdf

资源详情

资源评论

资源推荐

Revision History

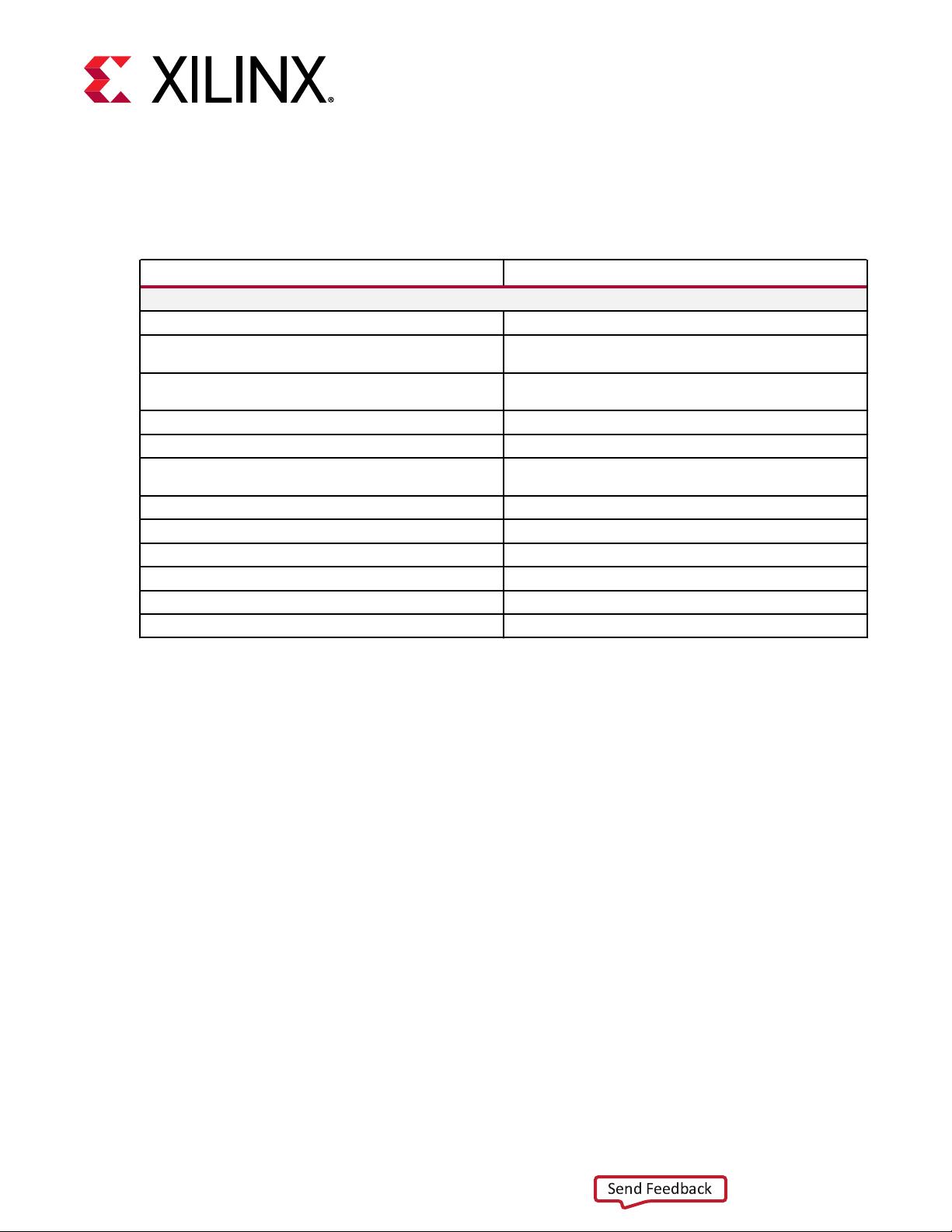

The following table shows the revision history for this document.

Section Revision Summary

12/20/2018 Version 2018.3

Schedule Viewer Updated information on the schedule viewer.

Optimizing the Design Clarified information on dataflow and loops throughout

section.

C++ Arbitrary Precision Fixed-Point Types: Reference

Information

Added note on using header files.

HLS Math Library Updated information on how hls_math.h is used.

The HLS Math Library, Fixed-Point Math Functions Updated functions.

HLS Video Library, HLS Video Functions Library Moved the HLS video library to the Xilinx GitHub (https://

github.com/Xilinx/xfopencv)

HLS SQL Library, HLS SQL Library Functions Updated hls::db to hls::alg functions.

System Calls Added information on using the __SYNTHESIS__ macro.

Arrays Added information on array sizing behavior.

Command Reference Updated commands.

config_dataflow, config_rtl Added the option -disable_start_propagation

Class Methods, Operators, and Data Members Added guidance on specifying data width.

Revision History

UG902 (v2018.3) December 20, 2018 www.xilinx.com

High-Level Synthesis 2

Send Feedback

Table of Contents

Revision History...............................................................................................................2

Chapter 1: High-Level Synthesis............................................................................ 5

High-Level Synthesis Benefits....................................................................................................5

High-Level Synthesis Basics....................................................................................................... 6

Understanding Vivado HLS...................................................................................................... 12

Using Vivado HLS...................................................................................................................... 19

Data Types for Efficient Hardware.......................................................................................... 71

Managing Interfaces.................................................................................................................77

Optimizing the Design............................................................................................................119

Verifying the RTL..................................................................................................................... 176

Exporting the RTL Design.......................................................................................................189

Chapter 2: High-Level Synthesis C Libraries................................................196

Arbitrary Precision Data Types Library.................................................................................196

HLS Stream Library................................................................................................................. 211

HLS Math Library.....................................................................................................................220

HLS Video Library.................................................................................................................... 231

HLS IP Libraries........................................................................................................................231

HLS Linear Algebra Library.................................................................................................... 254

HLS DSP Library.......................................................................................................................265

HLS SQL Library....................................................................................................................... 267

Chapter 3: High-Level Synthesis Coding Styles..........................................269

Unsupported C Constructs.....................................................................................................269

C Test Bench.............................................................................................................................273

Functions..................................................................................................................................280

Loops........................................................................................................................................ 282

Arrays........................................................................................................................................289

Data Types................................................................................................................................299

C Builtin Functions.................................................................................................................. 324

Hardware Efficient C Code..................................................................................................... 325

UG902 (v2018.3) December 20, 2018 www.xilinx.com

High-Level Synthesis 3

Send Feedback

C++ Classes and Templates....................................................................................................343

Assertions.................................................................................................................................351

SystemC Synthesis.................................................................................................................. 354

Chapter 4: High-Level Synthesis Reference Guide...................................373

Command Reference.............................................................................................................. 373

GUI Reference..........................................................................................................................447

Interface Synthesis Reference............................................................................................... 451

AXI4-Lite Slave C Driver Reference........................................................................................469

HLS Video Functions Library.................................................................................................. 482

HLS Linear Algebra Library Functions.................................................................................. 482

HLS DSP Library Functions.....................................................................................................491

HLS SQL Library Functions..................................................................................................... 504

C Arbitrary Precision Types.................................................................................................... 507

C++ Arbitrary Precision Types................................................................................................ 521

C++ Arbitrary Precision Fixed-Point Types........................................................................... 541

Comparison of SystemC and Vivado HLS Types..................................................................564

Appendix A: Additional Resources and Legal Notices........................... 571

Xilinx Resources.......................................................................................................................571

Documentation Navigator and Design Hubs...................................................................... 571

References................................................................................................................................572

Please Read: Important Legal Notices................................................................................. 572

UG902 (v2018.3) December 20, 2018 www.xilinx.com

High-Level Synthesis 4

Send Feedback

Chapter 1

High-Level Synthesis

The Xilinx

®

Vivado

®

High-Level Synthesis (HLS) tool transforms a C specicaon into a register

transfer level (RTL) implementaon that you can synthesize into a Xilinx eld programmable gate

array (FPGA). You can write C specicaons in C, C++, or SystemC, and the FPGA provides a

massively parallel architecture with benets in performance, cost, and power over tradional

processors. This chapter provides an overview of high-level synthesis.

Note: For more informaon on FPGA architectures and Vivado HLS basic concepts, see the Introducon to

FPGA Design Using High-Level Synthesis (UG998).

High-Level Synthesis Benefits

High-level synthesis bridges hardware and soware domains, providing the following primary

benets:

• Improved producvity for hardware designers

Hardware designers can work at a higher level of abstracon while creang high-performance

hardware.

• Improved system performance for soware designers

Soware developers can accelerate the computaonally intensive parts of their algorithms on

a new compilaon target, the FPGA.

Using a high-level synthesis design methodology allows you to:

• Develop algorithms at the C-level

Work at a level that is abstract from the implementaon details, which consume development

me.

• Verify at the C-level

Validate the funconal correctness of the design more quickly than with tradional hardware

descripon languages.

• Control the C synthesis process through opmizaon direcves

Create specic high-performance hardware implementaons.

• Create mulple implementaons from the C source code using opmizaon direcves

UG902 (v2018.3) December 20, 2018 www.xilinx.com

High-Level Synthesis 5

Send Feedback

剩余572页未读,继续阅读

JimmyMcgilI

- 粉丝: 25

- 资源: 2

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0