没有合适的资源?快使用搜索试试~ 我知道了~

首页DDR基础知识和PCB布线设计

DDR基础知识和PCB布线设计

需积分: 29 13 下载量 117 浏览量

更新于2023-03-16

评论

收藏 3.19MB DOC 举报

详细介绍了DDR的基础知识和详细的器件特性,准确的讲解了如何进行DDR1~DRR4的布线问题和实际操作流程

资源详情

资源评论

资源推荐

基本概念:

DDR=Double Data Rate 双倍速率同步动态随机存储器 。严格的说 DDR 应该叫 DDR

SDRAM。

DDR 与 SDRAM 的区别:

SDRAM 是 Synchronous Dynamic Random Access Memory 的缩写,即同步动态随机存

取存储器。SDRAM 只在时钟周期的上升沿传输指令、地址和数据。而 DDR 内存的数据线

供有特殊的电路,可以让它在时钟的上、下沿都传输数据。

DDR 与 SDRAM 的功能区别:

(1) 初始化。SDRAM 在开始使用前要进行初始化,这项工作主要是对模式寄存器进行设置,

即 MRS。DDR SDRAM 与 SDRAM 一样,在开机时也要进行 MRS,不过由于操作功能的

增多,DDR SDRAM 在 MRS 之前还增加了一个扩展模式寄存器设置(EMRS)过程。这个扩

展模式寄存器对 DLL 的有效与禁止、输出驱动强度等功能实施控制。

(2) 时钟。前面介绍 SDRAM 时已经看到,SDRAM 的读/写采用单一时钟。在 DDR

SDRAM 工作中要用差分时钟,也就是两个时钟,一个是 CLK,另一个是与之反相的

CK#。CK#并不能被理解为第二个触发时钟(可以在讲述 DDR 原理时简单地这么比喻),它

能起到触发时钟校准的作用。由于数据是在 CLK 的上下沿触发的,造成传输周期缩短了一

半,因此必须要保证传输周期的稳定以确保数据的正确传输,这就要求对 CLK 的上下沿间

距要有精确的控制。但因为温度、电阻性能的改变等原因,CLK 上下沿间距可能发生变化,

此时与其反相的 CK#就起到纠正的作用(CLK 上升快下降慢,CK#则是上升慢下降快)。而

由于上下沿触发的原因,也使 CL=1.5 或 2.5 成为可能,并容易实现。【注:CL(CAS

Latency):为 CAS 的延迟时间,这是纵向地址脉冲的反应时间,也是在一定频率下衡量

支持不同规范的内存的重要标志之一】

(3) 数据选取(DQS)脉冲。DQS 是 DDR SDRAM 中的重要信号,其功能主要用来在一个时

钟周期内准确地区分出每个传输周期,并使数据得以准确接收。每一块 DDR SDRAM 芯片

都有一个双向的 DQS 信号线。在写入时,它用来传送由北桥发来的 DQS 信号;在读取时,

则由芯片生成 DQS 向北桥发送。可以说,DQS 就是数据的同步信号。【注:北桥是个人

电脑主板芯片组两枚大规模芯片中的一枚。北桥被用来处理高速信号,通常处理 CPU(处

理器),RAM(内存),AGP 端口或 PCI Express,和南桥芯片之间的通信。南桥芯片负

责 I/O 总线之间的通信,如 PCI 总线、USB、LAN、ATA、SATA、音频控制器、键盘控制

器、实时时钟控制器、高级电源管理等,这些技术一般相对来说比较稳定,所以不同芯片

组中可能南桥芯片是一样的,不同的只是北桥芯片。】

(4) 写入延时。在写入时,与 SDRAM 的 0 延时不一样,DDR SDRAM 的写入延迟已经不

是 0 了。在发出写入命令后,DQS 与写入数据要等一段时间才会送达。这个周期被称为

DQS 相对于写入命令的延迟时间。

为什么会有这样的延迟呢?原因也在于同步,毕竟在一个时钟周期内进行两次传送需要很

高的控制精度,它必须要等接收方做好充分的准备才行。tDQSS 是 DDR 内存写入操作的

一个重要参数,太短的话恐怕接收有误,太长则会造成总线空闲。tDQSS 最短不能小于

0.75 个时钟周期,最长不能超过 1.25 个时钟周期。

(5) 突发长度与写入掩码。在 DDR SDRAM 中,突发长度只有 2、4、8 三种选择,没有了

SDRAM 的随机存取的操作(突发长度为 1)和全页式突发方式。同时,突发长度的定义也与

SDRAM 的不一样了,它不再指所连续寻址的存储单元数量,而是指连续的传输周期数。

对于突发写入,如果其中有不想存入的数据,仍可以运用 DM 信号进行屏蔽。DM 信

号和数据信号同时发出,接收方在 DQS 的上升沿与下降沿来判断 DM 的状态,如果 DM 为

高电平,那么之前从 DQS 脉冲中部选取的数据就被屏蔽了。

(6)延迟锁定回路(DLL)。DDR SDRAM 对时钟的精确性有着很高的要求,而 DDR

SDRAM 有两个时钟,一个是外部的总线时钟,一个是内部的工作时钟。在理论上,DDR

SDRAM 的这两个时钟应该是同步的,但由于种种原因,如温度、电压波动而产生延迟使

两者很难同步,更何况时钟频率本身也有不稳定的情况。这就需要根据外部时钟动态修正

内部时钟的延迟来实现内部时钟与外部时钟的同步,为此专门设置了 DLL。利用这种电路,

可使内部时钟与外部时钟保持同步。

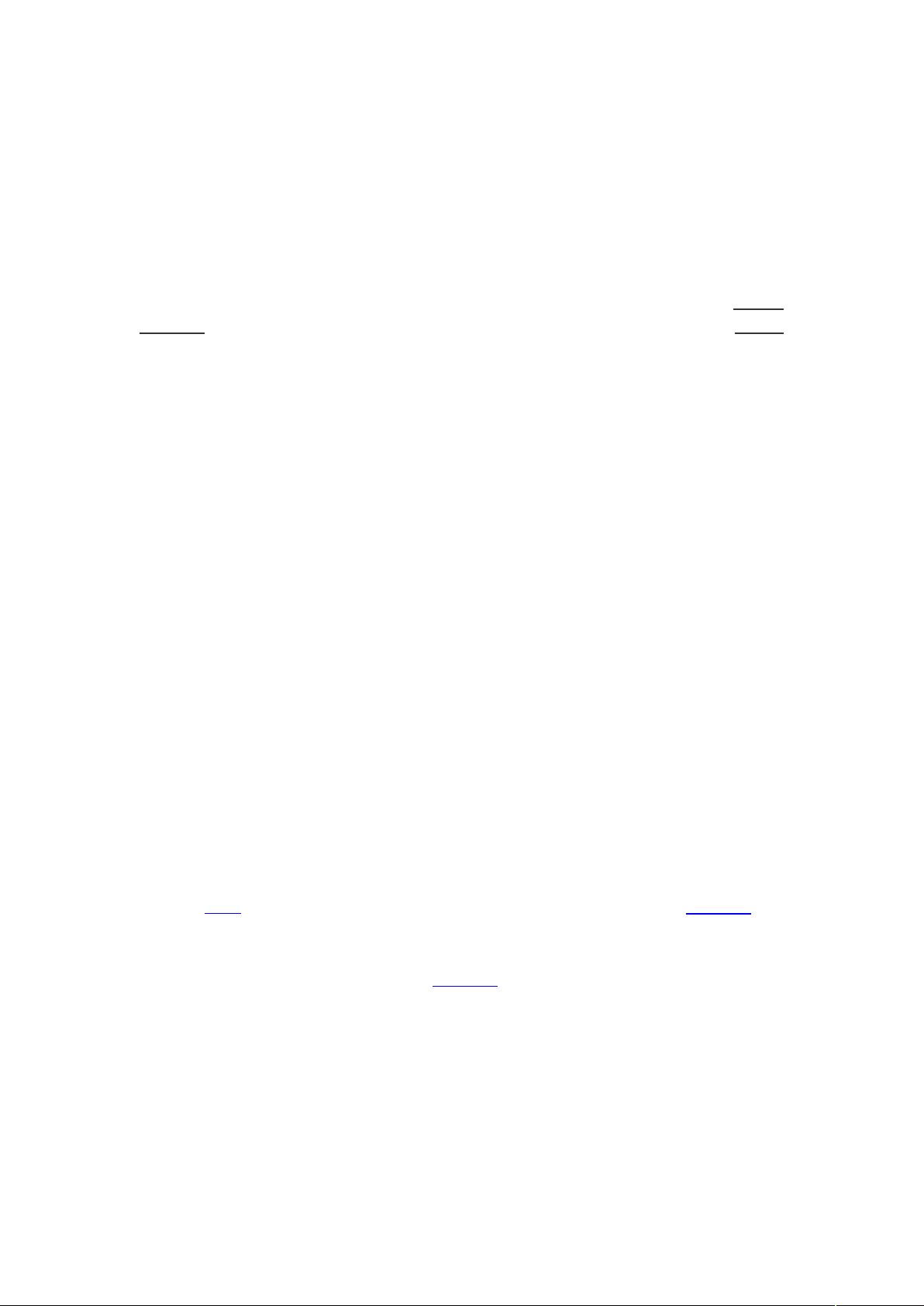

SDRAM、DDR、DDR2、DDR3、DDR4 速率上的各自特点:

SDRAM(Synchronous Dynamic Random Access Memory):為同步動態隨機存取記憶

體,字首的 Synchronous 告訴了大家這種記憶體的特性,也就是同步。1996 年底,

SDRAM 開始在系統中出現,不同於早期的技術,SDRAM 是為了與中央處理器的計時同

步化所設計,這使得記憶體控制器能夠掌握準備所要求的資料所需的準確時鐘週期,因此

中央處理器從此不需要延後下一次的資料存取。舉例而言,PC66 SDRAM 以 66 MT/s 的

傳輸速率運作;PC100 SDRAM 以 100 MT/s 的傳輸速率運作;PC133 SDRAM 以 133

MT/s 的傳輸速率運作,以此類推。

SDRAM 亦可稱為 SDR SDRAM(Single Data Rate SDRAM),Single Data Rate 為單倍

數據傳輸率,SDR SDRAM 的核心、I/O、等效時脈皆相同,舉例而言,PC133 規格的記

憶體,其核心、I/O、等效時脈都是 133MHz。而 Single Data Rate 意指 SDR SDRAM 在 1

個周期內只能讀寫 1 次,若需要同時寫入與讀取,必須等到先前的指令執行完畢,才能接

著存取。

DDR SDRAM(Double Data Rate SDRAM):為雙通道同步動態隨機存取記憶體,是新

一代的 SDRAM 技術。別於 SDR(Single:Data Rate)單一周期內只能讀寫 1 次,DDR 的

雙倍數據傳輸率指的就是單一周期內可讀取或寫入 2 次。在核心時脈不變的情況下,傳輸

效率為 SDR SDRAM 的 2 倍。第一代 DDR 記憶體 Prefetch 為 2bit,是 SDR 的 2 倍,運作

時 I/O 會預取 2bit 的資料。舉例而言,此時 DDR 記憶體的傳輸速率約為 266~400 MT/s

不等,像是 DDR 266、DDR 400 都是這個時期的產品。【prefetch:意为预加载。

DDR,DDR2 是四位预取(4-bit Prefetch),DDR3 和 DDR4 都是八位预取(8-bit

Prefetch)。而 8-bit Prefetch 可以使得内核时钟是 DDR 时钟的四分之一,这也是

Prefetch 的根本意义所在。故此 DDR 的每一个存储单元 cell 为 DQ 的带宽(及 IO 口的位

数)】

DDR2 SDRAM(Double Data Rate Two SDRAM):為雙通道兩次同步動態隨機存取記憶

體。DDR2 記憶體 Prefetch 又再度提昇至 4 bit(DDR 的兩倍),DDR2 的 I/O 時脈是 DDR

的 2 倍,也就是 266、333、400MHz。舉例:核心時脈同樣有 133~200MHz 的顆粒,I/O

時脈提升的影響下,此時的 DDR2 傳輸速率約為 533~800 MT/s 不等,也就是常見的

DDR2 533、DDR2 800 等記憶體規格。

DDR3 SDRAM(Double Data Rate Three SDRAM):為雙通道三次同步動態隨機存取記

憶體。DDR3 記憶體 Prefetch 提昇至 8 bit,即每次會存取 8 bits 為一組的數據。DDR3 傳

輸速率介於 800~1600 MT/s 之間。此外,DDR3 的規格要求將電壓控制在 1.5V,較

DDR2 的 1.8V 更為省電。DDR3 也新增 ASR(Automatic Self-Refresh)、SRT(Self-

Refresh Temperature)等兩種功能,讓記憶體在休眠時也能夠隨著溫度變化去控制對記憶

體顆粒的充電頻率,以確保系統資料的完整性。

DDR4 SDRAM(Double Data Rate Fourth SDRAM):DDR4 提供比 DDR3/ DDR2 更低

的供電電壓 1.2V 以及更高的頻寬,DDR4 的傳輸速率目前可達 2133~3200 MT/s。DDR4

新增了 4 個 Bank Group 資料組的設計,各個 Bank Group 具備獨立啟動操作讀、寫等動

作特性,Bank Group 資料組可套用多工的觀念來想像,亦可解釋為 DDR4 在同一時脈工

作周期內,至多可以處理 4 筆資料,效率明顯好過於 DDR3。 另外 DDR4 增加了

DBI(Data Bus Inversion)、CRC(Cyclic Redundancy Check)、CA parity 等功能,讓

DDR4 記憶體在更快速與更省電的同時亦能夠增強信號的完整性、改善資料傳輸及儲存的

可靠性。

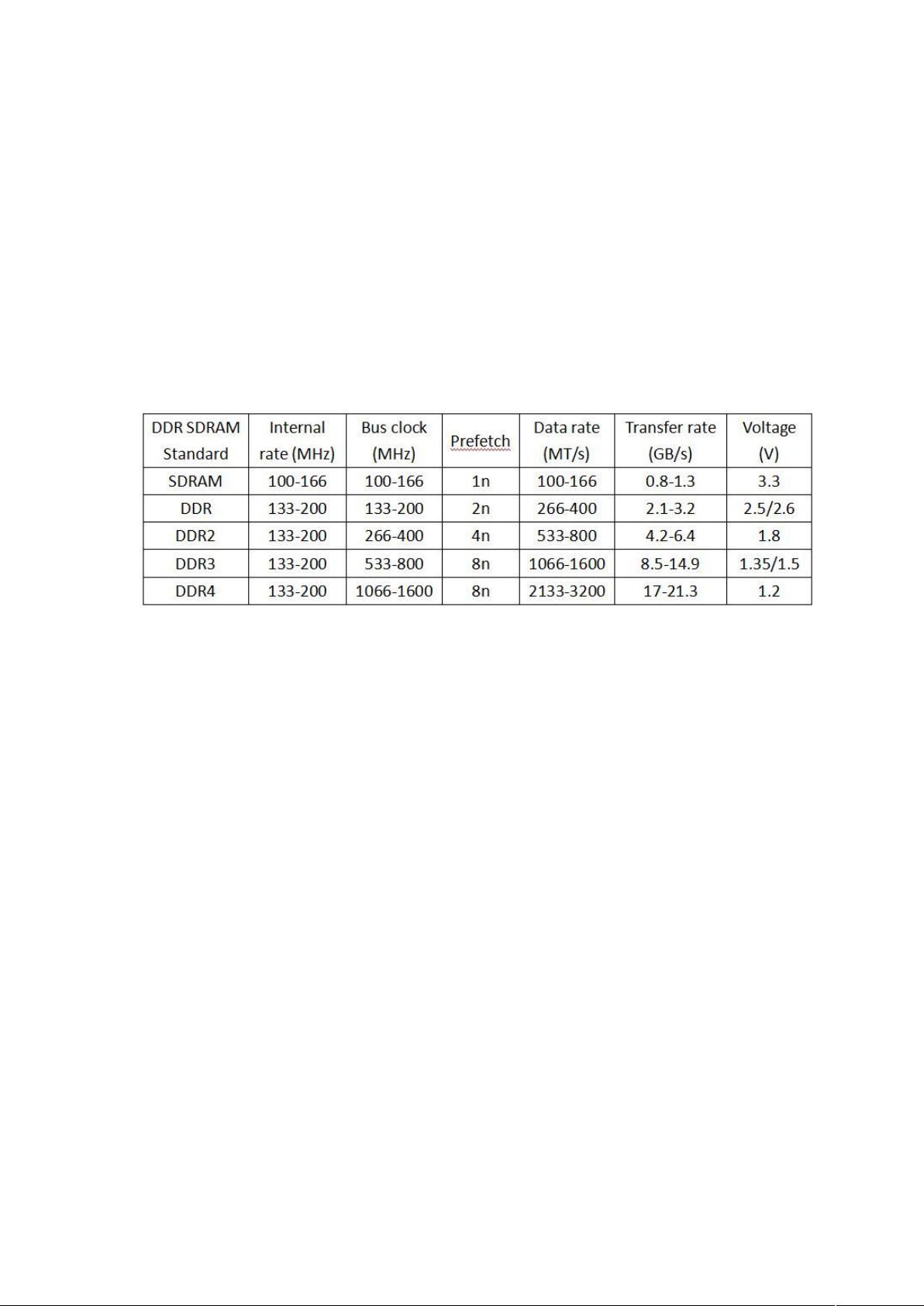

DDR prefetch 与 Burst

1、Prefetch 介绍

首先,简单介绍一下 Prefetch 技术。所谓 prefetch,就是预加载,这是 DDR 时代提出的技

术。在 SDR 中,并没有这一技术,所以其每一个 cell 的存储容量等于 DQ 的宽度(芯片数

据 IO 位宽)。

进入 DDR 时代之后,就有了 prefetch 技术,DDR 是两位预取(2-bit Prefetch),有的公

司则贴切的称之为 2-n Prefetch(n 代表芯片位宽)。DDR2 是四位预取(4-bit

Prefetch),DDR3 和 DDR4 都是八位预取(8-bit Prefetch)。而 8-bit Prefetch 可以使得

内核时钟是 DDR 时钟的四分之一,这也是 Prefetch 的根本意义所在。

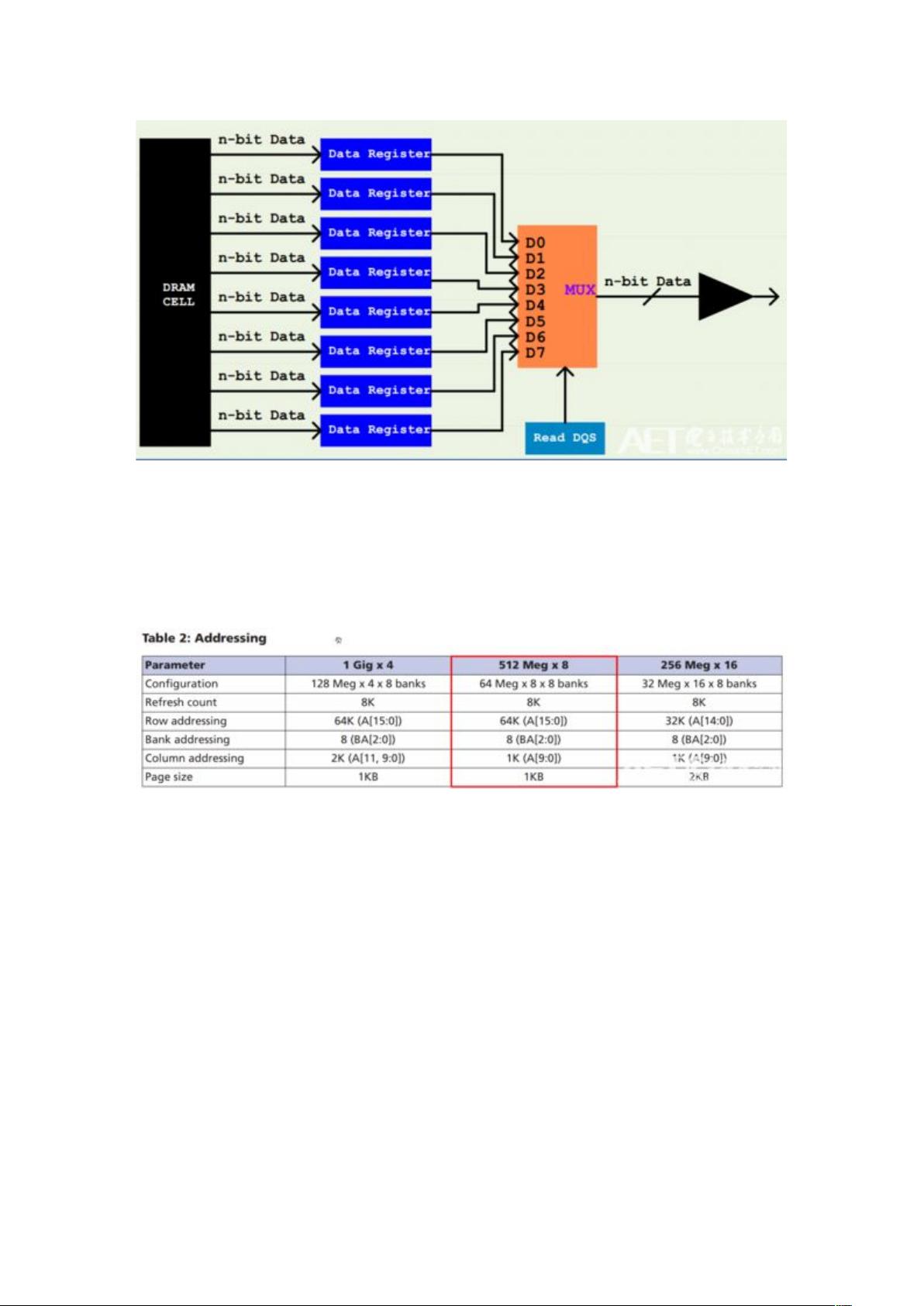

补充说明:芯片位宽的另一种说法是配置模式(Configuration),在 DDR3 时代,一般有

x4,x8,x16。下面以 DDR3 为例,下图是个简单 一个简单 Read 预取示意图,Write 可以

看做是 个逆向过程。

当 DDR3 为 x8 Configuration 时,一个 Cell 的容量为 8x8bits,即 8 个字节。换一句话说,

在指定 bank、row 地址和 col 地址之后,可以往该地址内写入(或读取)8 Bytes。

2、如何计算 DDR3 SDRAM 的容量

以 Mircon 的某型号 DDR3 SDRAM 为例:

以图中红色部分的内容作为分析案例(8 个 bank,x8 的 Conguration):

计算方式一(错误):

64K*8*1K*8(Row Addressing * Bank Addressing * Column Addressing * x8

Configuration)= 4Gb(512 Megx8)。

大部分材料给出的都是这种错误的计算方法,误导了很多的初学者。这种计算方法咋一看

好像是对的。但是,仔细推敲一下,便可以发现,按照计算方式一的逻辑,则认为每一个

Cell 的容量是 1bit*8(x8 Configuration),即 8bit。这与我们在第一部分所讨论的结果

(一个 Cell 的容量为 64bits,x8 Configuration 下)不符。

当然,从某种角度来说,计算方式一也是正确的,因为分离出的 Column Address 的位数

实际上是和 prefetch 对应的。比如 DDR3 8-bit Prefetch 对 3bits 的 Column

Address,DDR2 4-bit Prefetch 对应的是 2bits 的 Column Address。只是如果直接按照计

算方式一来计算的话,对于初次接触 DDR 的人来说,理解起来存在一定的困难,这也是

我写这一篇博文的原因。

剩余16页未读,继续阅读

frederickvon

- 粉丝: 0

- 资源: 7

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- stc12c5a60s2 例程

- Android通过全局变量传递数据

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0