DDR 部分布板指南

1.1 元件摆放指南

1.2 DDR Memory 附近的元件摆放

1.2.1 时钟(O)

时钟 CLK/CLK#按差分对布线,与之串联的电阻尽可能靠近主芯片摆放。

时钟差分对的并联电阻尽可能靠近 DDR 摆放(针对一片 DDR 的情况),如果是两片 DDR,则靠近串联电阻摆放。

1.2.2 地址线和控制信号线(CS,RAS,CAS,WE,CKE,ADDRESS)(O)

地址线上和控制信号线的串联电阻应靠近主芯片摆放。

地址线上和控制信号线的上拉电阻则靠近 DDR 摆放。

1.2.3 DQS 线(O)

DQS 线上的串联电阻尽量靠近主芯片摆放。

DQS 信号的上拉电阻则应靠近 DDR 摆放。

1.3 SDRAM 附近的元件摆放

参考 DDR 元件的摆放。

1.4 布线指南

1.4.1 总体规划

如果与信号连接的负载在一个以上,则必须考虑采用 T 状布线,并且要使得所有的分支布线尽量保持等长。

布线中把 DATA 的串联电阻尽量放置在主芯片与 MEMORY 之间,而 DQM 与 DQS 对主芯片来说为输出信号,因此

尽可能靠近主芯片摆放,达不到的的情况下也要与 DATA 信号的串联电阻要求一致。

VTT 的终端电阻要尽量靠近它们各自的信号,他们可以在走线的中间放置,建议靠近 MEMORY 的管脚放置。

所有的旁路电容都应该放置在相关的电源引脚的旁边。

对于存储器的时钟线(CLK/CLK#)和数据选通信号(DQS)以及 DQM 信号,需要特别的注意的是,它们需要靠近到

电源或者地层布线,也最好能做到包地处理。

对于约为信号阻抗为 60 欧的 PCB 来讲,线宽:间距:线宽为 1:1:1,建议为 8mil。

1.4.1 DATA,DQS,DQM 信号

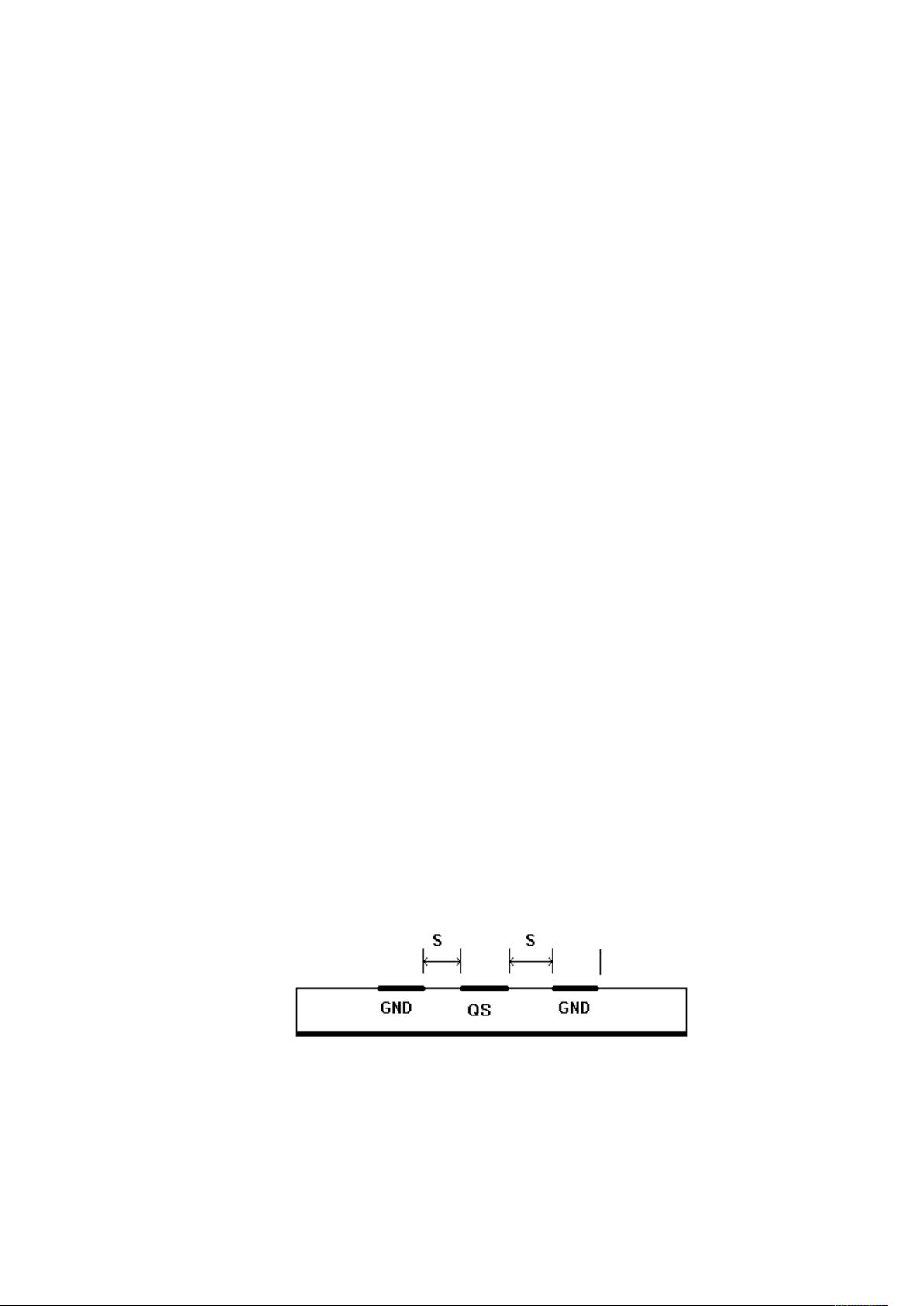

DQS 信号在布线时应该特别小心,对它的信号有以下要求:首先要做包地处理,地线应尽量包全整个信号,并且每

隔 1”要打过孔缝到地上,如果有可能的话,DQS 信号与其它信号的间距与线宽比为 3:1,如下图所示。

建议 Data/DQM 的间距最少为 2:1。

memory 的数据组划分如下(10 个)信号:(建议将一个 LMI 接口的数据线做为一组,不只这 10 个)

Data0-Data1-Data2-Data3-DQM-DQS-Data4-Data5-Data6-Data7

数据信号与 DQS 信号的长度关系为:LQS – 0.05 inch <= LDATA <= LQS + 0.05 inch

因此 DQS 线的最长与最短布线关系为:

评论0