没有合适的资源?快使用搜索试试~ 我知道了~

首页LPDDR4_Spec.pdf

资源详情

资源评论

资源推荐

COMMITTEE LETTER BALLOT

Solid State Technology Association

3103 North 10th Street

Arlington, Virginia 22201

Ballot Template Version draft rev. 8/11

© JEDEC 2011

Committee: JC-42.6

Committee Item Number: 1824.42B

Subject: Proposed LPDDR4 Specification Revision B

Background: Reference Material: JESD209-4A

This ballot material contains the following items.

1. Item which was approved by JC42.6 Committee.

2. Item which was approved by tg426_8 LPDDR4 TG.

3. The ballot draft about LPDDR4 single channel device which was

approved to send voting machine by TG on 2016/6/30.

4. 254 ball UFS/eMMC MCP Two-Channel FBGA Ballout

Renumbering to figures, tables and chapters/sections was not done yet.

Keywords: LPDDR4, SDRAM, Specification, Data Sheet, JESD209-4

LPDDR4 Specification Revision B Item 1824.42B

Page 2 of 310

P R O P O S E D

Reference: Update history

1. The update portion from JESD209-4A is described below.

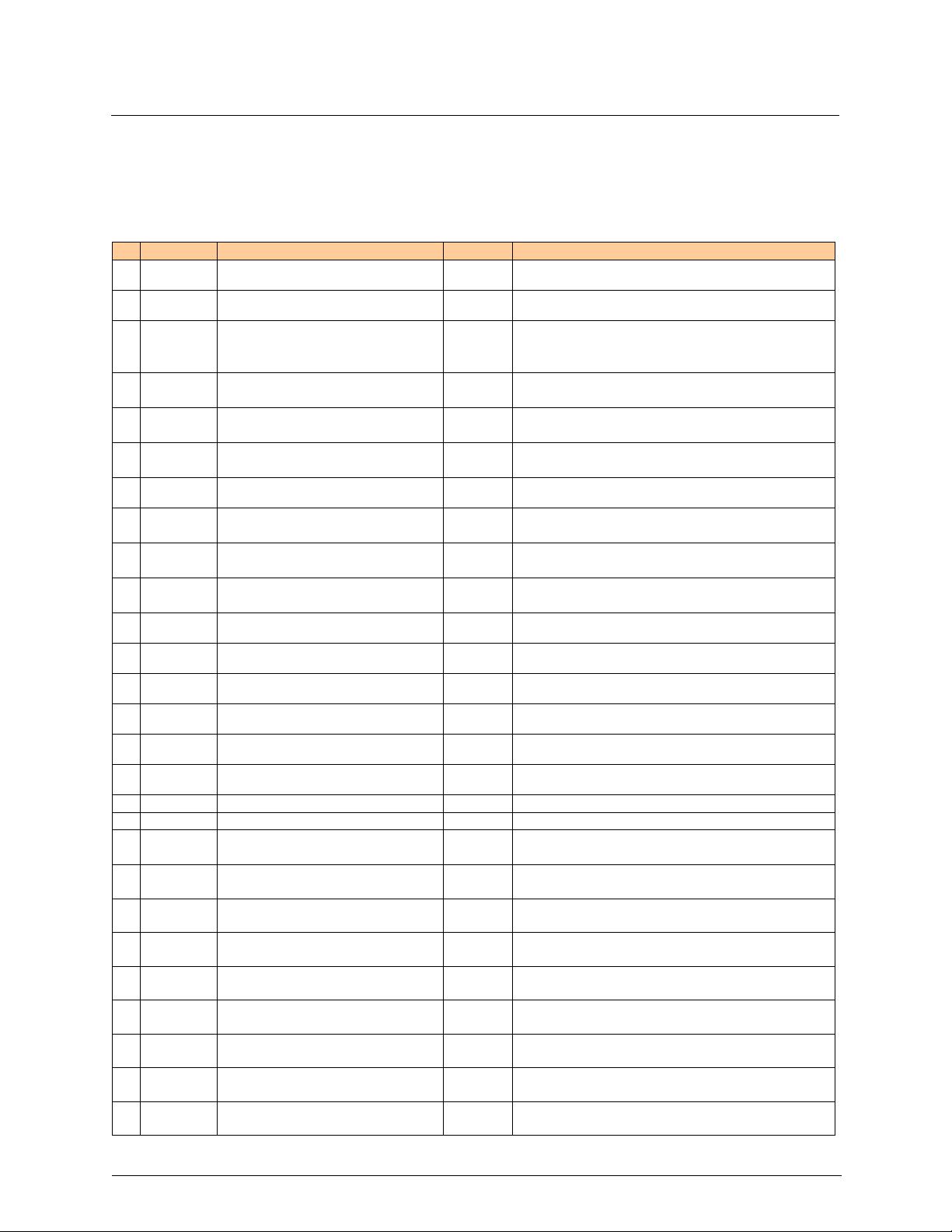

Table 00 - Modification from JESD209-4A

Note: Modification parts are marked by a RED side bar.

# Itme # Subject Page Reference

11831.95Scope 5

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

2 1831.95 Pad Order for single channel 7

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

31831.95

272-ball 15mm x 15mm 0.4mm pitch,

Quad-Channel POP FBGA (top view)

Using Variation VFFCDB for MO-273

8

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

41831.95

200-ball x32 Discrete Package, 0.80mm

x 0.65mm using MO-311

9-10

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

51831.95

203 ball Discrete Two-Channel FBGA

(top view) using MO-311

11

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

61831.95

432-ball x64 HDI Discrete Package,

0.50mm x 0.50mm (MO-313)

12

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

71831.95x64 Non HDI Discrete Package 13

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

81831.95

275 ball MCP Two-Channel FBGA (top

view) using MO-276

14

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

967.00A

254 ball eMMC MCP Two-Channel

FBGA (top view) using MO-276

15

JC63^20151221^67.00A^Mediatek_Micron_Samsung_SK_Hynix^

LPDDR4_2ch_254b_MCP.doc

10 67.00A

254 ball UFS MCP Two-Channel FBGA

(top view) using MO-276

16

JC63^20151221^67.00A^Mediatek_Micron_Samsung_SK_Hynix^

LPDDR4_2ch_254b_MCP.doc

11 1831.95 Pad Definition and Description 17

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

12 1831.95 Functional Description 18

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

13 1814.71A LPDDR4 SDRAM Addressing 19-20

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/46507

14 1831.95 LPDDR4 SDRAM Addressing 19-22

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

15 1819.18C Simplified LPDDR4 State Diagram 23-25

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/46552

16 1831.66 Mode Register Definition 30

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/49876

17 1819.58A MR0 Register Information 31

https://vote.jedec.org/a_votingmachine/documents/RB15381-.pdf

18 1814.94A MR1 Register Information 32

https://vote.jedec.org/a_votingmachine/documents/RB15383-.pdf

19 1814.94A Burst Sequence 33

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/46553

20 1831.95 MR3 Register Information 36

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

21 XXXX.XX MR4 Register Information 37

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/44920

22 1831.95 MR8 Register Information 40

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

23 1819.05 MR11 Register Information 41

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/48677

24 1819.06 MR12 Register Information 42-43

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/46554

25 1831.95 MR16 Register Information 48

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

26 1831.95 MR17 Register Information 49

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

27 1831.66 MR30 Register Information 58

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/49876

Page 3 of 310

LPDDR4 Specification Revision B Item 1824.42B

P R O P O S E D

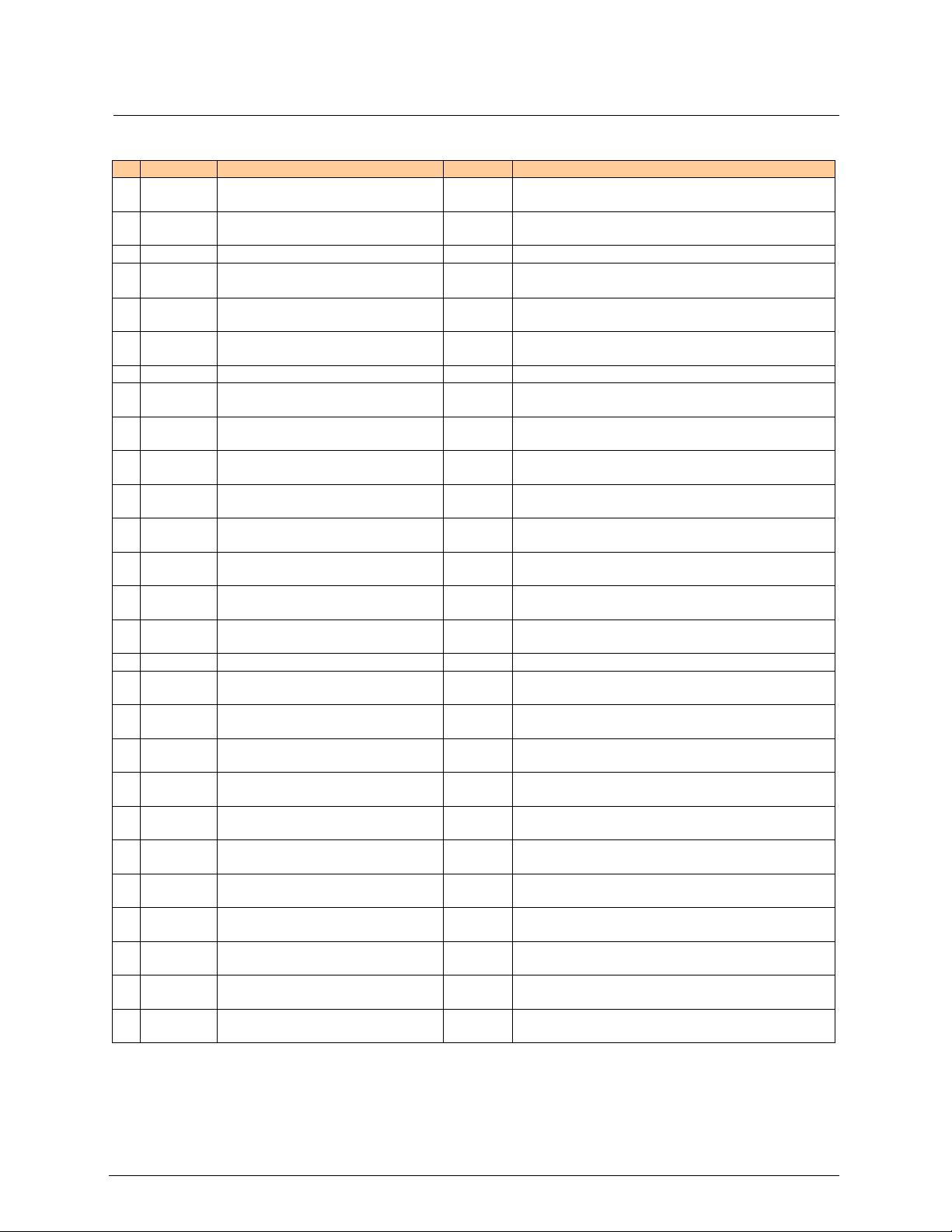

Table 00 - Modification from JESD209-4A (Cont’d)

# Itme # Subject Page Reference

28 1831.66 MR39 Register Information 60

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/49876

29 1831.70 Read AC Timing 76

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/48780

30 1824.75A Write Timing 81-83

https://vote.jedec.org/a_votingmachine/documents/

31 1831.87

Write and Masked Write operation DQS

controls (WDQS Control)

88-93

https://vote.jedec.org/a_votingmachine/documents/

RB16157-.pdf

32 18xx.xx Masked Write Timing constraints 121-122

ttp://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/48256

33 1824.64 Masked Write Timing constraints 121-122

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/47293

34 1831.23 Auto-PRECHARGE Operation 132-133

https://vote.jedec.org/a_votingmachine/documents/

35 1819.32C Refresh command

140, 143,

146

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/47852

36 18xx.xx Refresh Diagram 142

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/46630

37 XXXX.XX Refresh Requirement from SRX to SRE 147-149

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/50160

38 1831.95 Refresh Requirement 147-148

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

39 XXXX.XX Self Refresh Operation 149

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/46570

40 1831.95 SELF REFRESH ABORT 152

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

41 1819.52B MODE REGISTER READ(MRR) 154

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/46516

42 1831.03

MRR/MRW Timing Constraints: DQ ODT

is Disable

160-161

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/50427

43 1814.90A Command Bus Training 180-185

https://vote.jedec.org/a_votingmachine/documents/

44 1819.65B Frequency Set Point 186-187

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/50144

45 1831.95 Frequency Set Point 186

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

46 1831.95 Mode Reister Write-WR Leveling Mode 192

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

47 1819.95A Input Clock Frequency Stop and Change 194

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/46517

48 1831.73 FIFO Write and ReadTiming Diagram 203-206

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/48626

49 XXXX.XX

Timing Constraints for Training

Commands

219

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/50000

50 1831.95 Thermal Offset 220

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

51 1831.95 ZQ Calibration 223

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

52 1831.95

Multi-Channel Considerations for Dual

Channel Devices

224

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

53 1831.60A Non-target DRAM 238-242

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/49898

54 XXXX.XX Power-down 244

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/50254

LPDDR4 Specification Revision B Item 1824.42B

Page 4 of 310

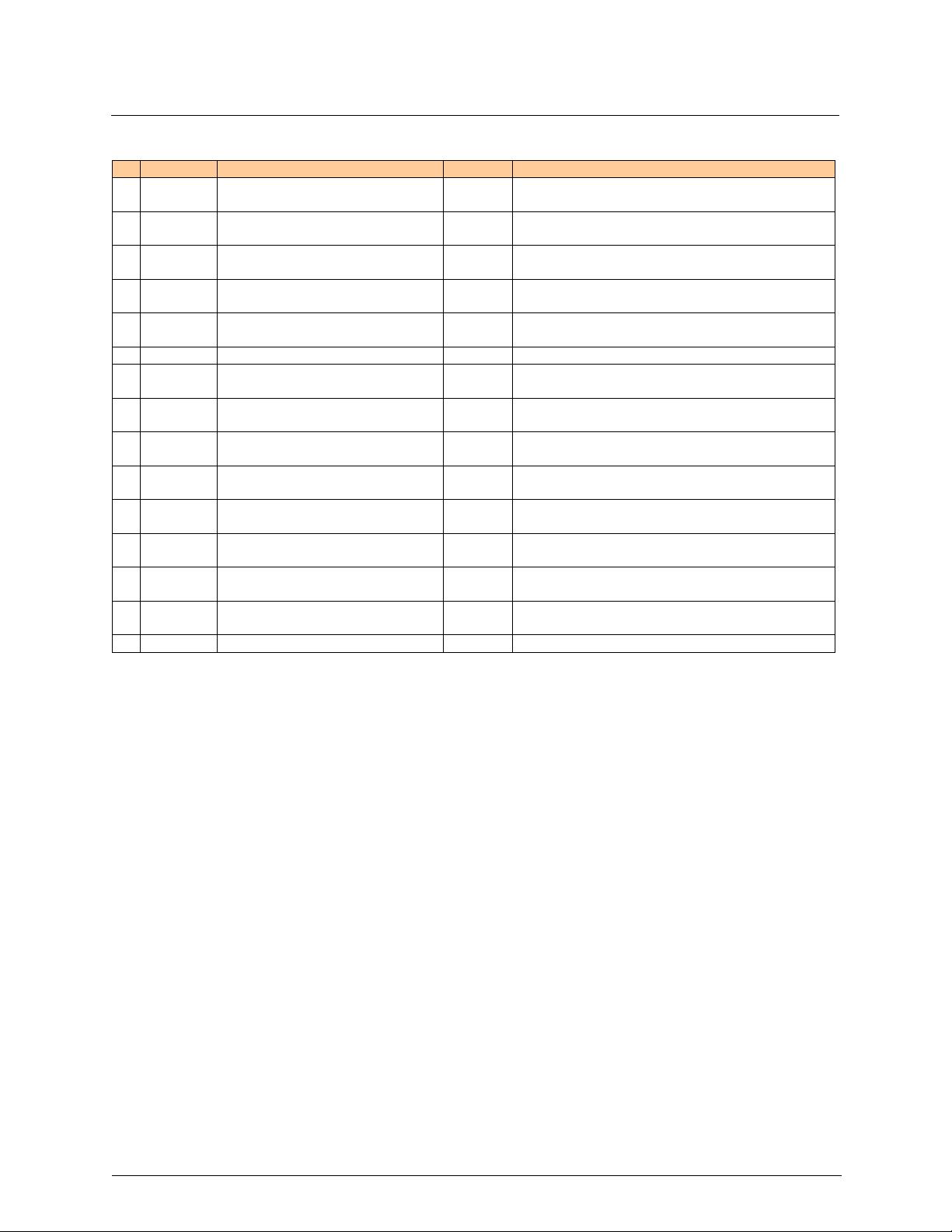

P R O P O S E D

Table 00 - Modification from JESD209-4A (Cont’d)

# Itme # Subject Page Reference

55 XXXX.XX

LPDDR4 VDDQ off during power down &

self refresh with power down mode

244

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/46570

56 1819.30 Input Clock Stop and Frequency Change 251-252

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/50802

57 1814.21A Truth Tables 253-254

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/48679

58 1819.61 Post Package Repair (PPR) 258-259

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/46519

59 1824.26 Recommended DC Operating Conditions 261

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/46551

60 1824.03A

1.1V High speed LVCMOS

265

https://vote.jedec.org/a_votingmachine/documents/

61 1831.22 Clock input definition 267-271

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/46279

62 1831.22 DQS input definition 272-276

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/45406

63 1831.95 IDD Specifications 294

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51118

64 1831.68 Clock Specification 295-296

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/49899

65 18xx.xx CA Timing Table 301

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/48197

66 1824.42 Data Timing 302-310

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/48198

67 XXXX.XX DBI timing parameter 304

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/51125

68 1831.72 Symbol of DQ to DQ offset 307, 310

http://members.jedec.org/file_upload/filegallery/download-

document/index/document_id/48625

69 1824.73 tDQS2DQ Rank to Rank 309, 310

https://vote.jedec.org/a_votingmachine/documents/

Page 5 of 310

LPDDR4 Specification Revision B Item 1824.42B

P R O P O S E D

1. Scope

This document defines the LPDDR4 standard, including features, functionalities, AC and DC

characteristics, packages, and ball/signal assignments. The purpose of this specification is to define the

minimum set of requirements for a JEDEC compliant 16 bit per channel SDRAM device with either one or

two channels. LPDDR4 dual channel device density ranges from 4 Gb through 32 Gb and single channel

density ranges from 2 Gb through 16 Gb. This document was created using aspects of the following

standards: DDR2 (JESD79-2), DDR3 (JESD79-3), DDR4 (JESD79-4), LPDDR (JESD209), LPDDR2

(JESD209-2) and LPDDR3 (JESD209-3).

Each aspect of the standard was considered and approved by committee ballot(s). The accumulation of

these ballots was then incorporated to prepare the LPDDR4 standard.

Reference: http://members.jedec.org/file_upload/filegallery/download-document/index/document_id/51118

剩余309页未读,继续阅读

zhuyujian321

- 粉丝: 5

- 资源: 16

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 数据结构1800题含完整答案详解.doc

- 医疗企业薪酬系统设计与管理方案.pptx

- 界面与表面技术界面理论与表面技术要点PPT学习教案.pptx

- Java集合排序及java集合类详解(Collection、List、Map、Set)讲解.pdf

- 网页浏览器的开发 (2).pdf

- 路由器原理与设计讲稿6-交换网络.pptx

- 火电厂锅炉过热汽温控制系统设计.doc

- 企业识别CIS系统手册[收集].pdf

- 物业管理基础知识.pptx

- 第4章财务预测.pptx

- 《集成电路工艺设计及器件特性分析》——实验教学计算机仿真系.pptx

- 局域网内共享文件提示没有访问权限的问题借鉴.pdf

- 第5章网络营销策略.pptx

- 固井质量测井原理PPT教案.pptx

- 毕业实习总结6篇.doc

- UGNX建模基础篇草图模块PPT学习教案.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0