没有合适的资源?快使用搜索试试~ 我知道了~

首页数字系统实验-电子钟.docx

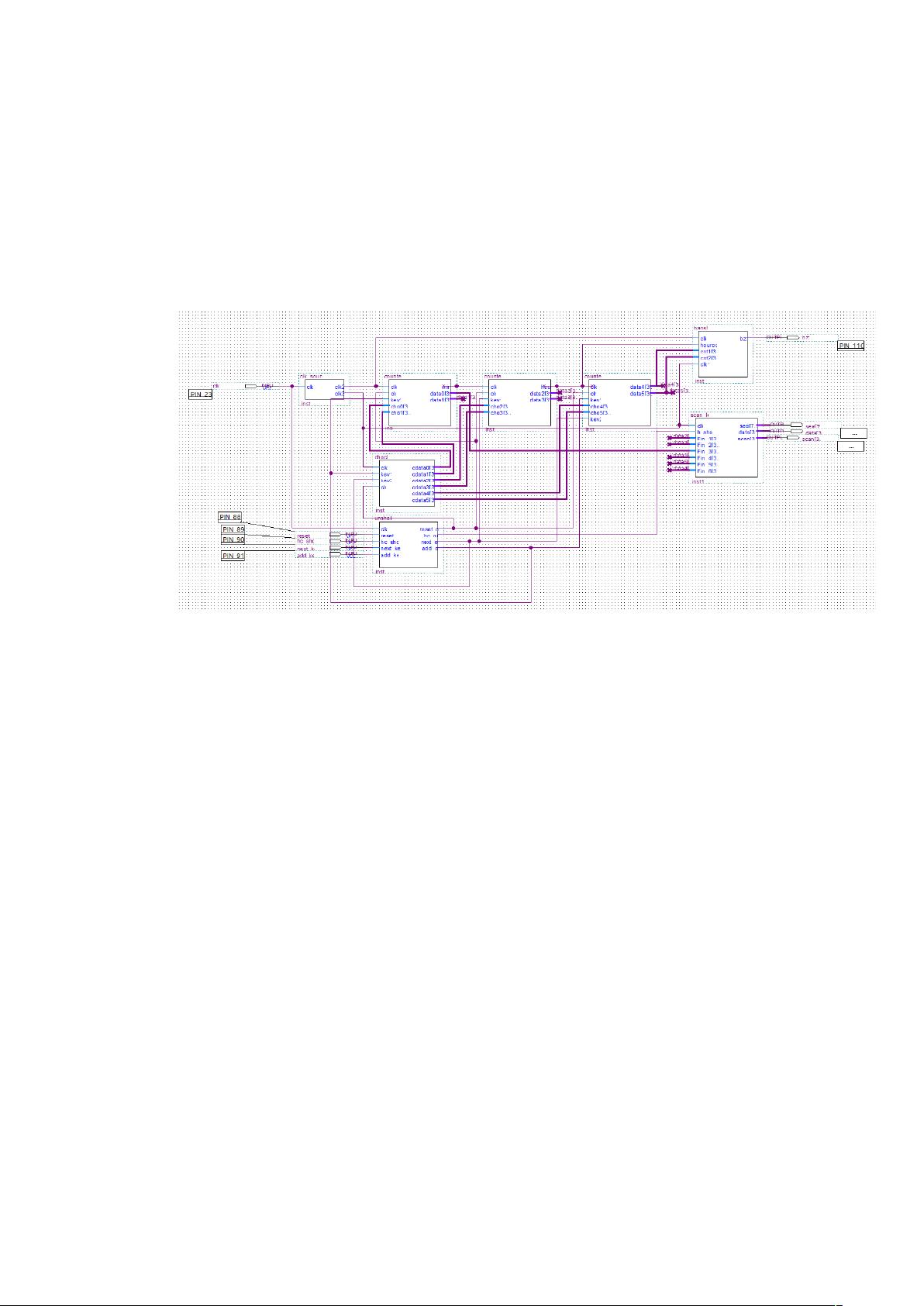

使用Quartus II开发、基于VHDL语言实现的电子时钟,在睿智四代AX4010板子上进行验证。实现的功能有:时分秒显示、重置、按键消抖、整点报时。 补充说明: 1.代码可能还不完善,供参考学习使用。 2.顶层连线图中部分连线是采用了“隔空连线”的方法,就是右键管脚直接绑定,这样可以使顶层图连线尽可能少,以减少线的交叉。所以需要读懂每个接口的输入输出。

资源详情

资源评论

资源推荐

目录

一、功能实现......................................................................................................2

二、源代码..........................................................................................................3

2.1 顶层图设计.............................................................................................3

2.2 时钟分频模块.........................................................................................3

2.3 秒计时模块.............................................................................................4

2.4 分计时模块.............................................................................................5

2.5 时计时模块.............................................................................................7

2.6 置数模块.................................................................................................8

2.7 按键消抖模块.......................................................................................10

2.8 报时模块...............................................................................................12

2.9 LED 灯管显示模块..............................................................................14

三、仿真............................................................................................................16

3.1 时钟 19:59:58 仿真...............................................................................16

3.2 时钟 23:59:58 仿真...............................................................................16

四、下载验证....................................................................................................17

4.1 管脚设计图...........................................................................................17

4.2 编译结果图...........................................................................................17

4.3 下载验证图...........................................................................................18

一、功能实现

1. 时分秒时钟显示;

2. 定点报时功能,x 点钟报时 x 次;

3. 时钟清零。按下按钮就可使时钟时、分、秒数字请零;

4. 按键消抖功能;

5. 置数功能。能够通过按按钮对时、分、秒进行置数。

二、源代码

2.1 顶层图设计

2.2 时钟分频模块

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

entity clk_sourse is

port(

clk:in std_logic;

clk2:out std_logic;

clk3:out std_logic

);

end clk_sourse;

architecture a of clk_sourse is

signal clk0:std_logic;

signal clk1:std_logic;

begin

clk2<=clk1;

clk3<=clk0;

process(clk)

variable cnt:integer range 0 to 50000000;

variable cnt1:integer range 0 to 5000;

begin

if(clk'event and clk='1')then

cnt:=cnt+1;

cnt1:=cnt1+1;

if(cnt=50000000)then

clk1<=not clk1;

cnt:=0;

end if;

if(cnt1=5000)then

clk0<=not clk0;

cnt1:=0;

end if;

end if;

end process;

end a;

2.3 秒计时模块

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

entity counter1 is

port(

clk:in std_logic;

clr:in std_logic;

key1:in std_logic;

min:out std_logic;

chg0:in std_logic_vector(3 downto 0);

chg1:in std_logic_vector(3 downto 0);

data0:out std_logic_vector(3 downto 0);

data1:out std_logic_vector(3 downto 0)

);

end counter1;

architecture a of counter1 is

signal cnt0:std_logic_vector(3 downto 0):="0000";

signal cnt1:std_logic_vector(3 downto 0):="0000";

剩余17页未读,继续阅读

DwD-

- 粉丝: 457

- 资源: 2

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

- MW全能培训汽轮机调节保安系统PPT教学课件.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0