没有合适的资源?快使用搜索试试~ 我知道了~

首页CycloneIV 器件中的时钟网络与PLL

CycloneIV 器件中的时钟网络与PLL

需积分: 9 12 下载量 190 浏览量

更新于2023-03-16

评论

收藏 1.5MB PDF 举报

FPGA中的PLL配置与功能实现,介绍了PLL的工作原理,一个配置实例。

资源详情

资源评论

资源推荐

CYIV-51005-2.3

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos

are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its

semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and

services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service

described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying

on any published information and before placing orders for products or services.

Cyclone IV 器件手册,

卷1

2011 年 11 月

Subscribe

ISO

9001:2008

Registered

5. Cyclone IV 器件中的时钟网络与 PLL

本章节介绍了 Cyclone

®

IV 器件系列中具有高级特性的层次时钟网络与锁相环 (PLL),

包括了实时重配置 PLL 计数器时钟频率和相移功能的详尽说明,这些功能使您能够扫

描 PLL 输出频率,以及动态调整输出时钟相移。

1 Quartus

®

II 软件在未使用外部器件情况下使能 PLL 及其功能。

本章节包含以下几部分内容:

■ 时钟网络 (第5-1页)

■ Cyclone IV 器件中的 PLL( 第 5-18 页 )

■ Cyclone IV PLL 硬件概述 ( 第 5-20 页 )

■ 时钟反馈模式 ( 第 5-23 页 )

■ 硬件特性 ( 第 5-26 页 )

■ 可编程带宽 ( 第 5-32 页 )

■ 相移的实现 ( 第 5-32 页 )

■ PLL 级联 ( 第 5-33 页 )

■ PLL 重配置 ( 第 5-34 页 )

■ 扩频时钟 ( 第 5-41 页 )

■ PLL 规范 ( 第 5-41 页 )

时钟网络

Cyclone IV GX 器件提供了多达 12 个专用时钟管脚 (

CLK[15..4]

),以用于驱动全局时

钟 (GCLKs)。Cyclone IV GX 器件的每一侧 ( 左侧除外 ) 支持四个专用时钟管脚,这些

时钟管脚能够驱动高达 30 个 GCLK。

Cyclone IV E 器件提供了多达 15 个专用时钟管脚 (

CLK[15..1]

),以用于驱动高达 20

个 GCLK。Cyclone IV E 器件的左侧支持三个专用时钟管脚,在顶端、底部及右侧支持

四个专用时钟管脚 (EP4CE6 与 EP4CE10 器件除外 )。EP4CE6 和 EP4CE10 器件仅在器件

左侧支持三个专用时钟管脚,在器件右侧支持四个专用时钟引脚。

November 2011

CYIV-51005-2.3

5–2 Chapter 5: Cyclone IV 器件中的时钟网络与 PLL

时钟网络

Cyclone IV 器件手册, Altera 公司 2011 年 11 月

卷 1

f 要了解关于每一个器件密度中的 GCLK 网络数量的详细信息,请参考

Cyclone IV FPGA

Device Family Overview

章节。

GCLK 网络

GCLK 驱动整个器件,并对器件各象限提供时钟。 器件中的所有资源 (I/O 单元、逻辑

阵列模块 (LAB)、专用乘法器模块以及 M9K 存储器模块 ) 都能够将 GCLK 用作时钟资

源。 这些全局网络资源可用于控制信号,例如:由外部管脚驱动的时钟使能及清零信

号。另外,内部逻辑也能够驱动 GCLK,以用于内部生成的 GCLK 和异步清零、时钟使

能,或者其它具有高扇出的控制信号。

第 5-4 页的表5-1和表5-2和第 5-7 页的表 5-3 列出了时钟源到 GCLK 网络的连接。

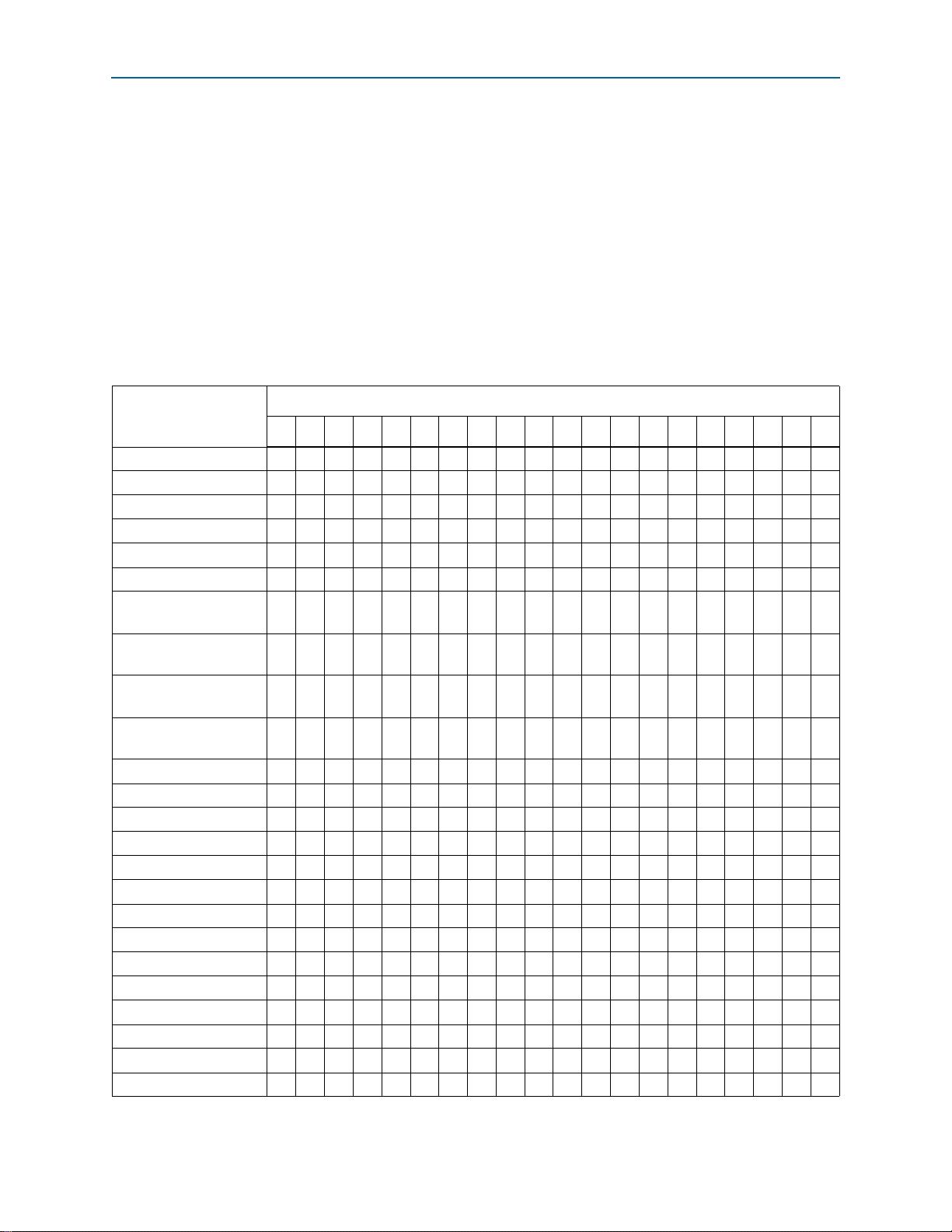

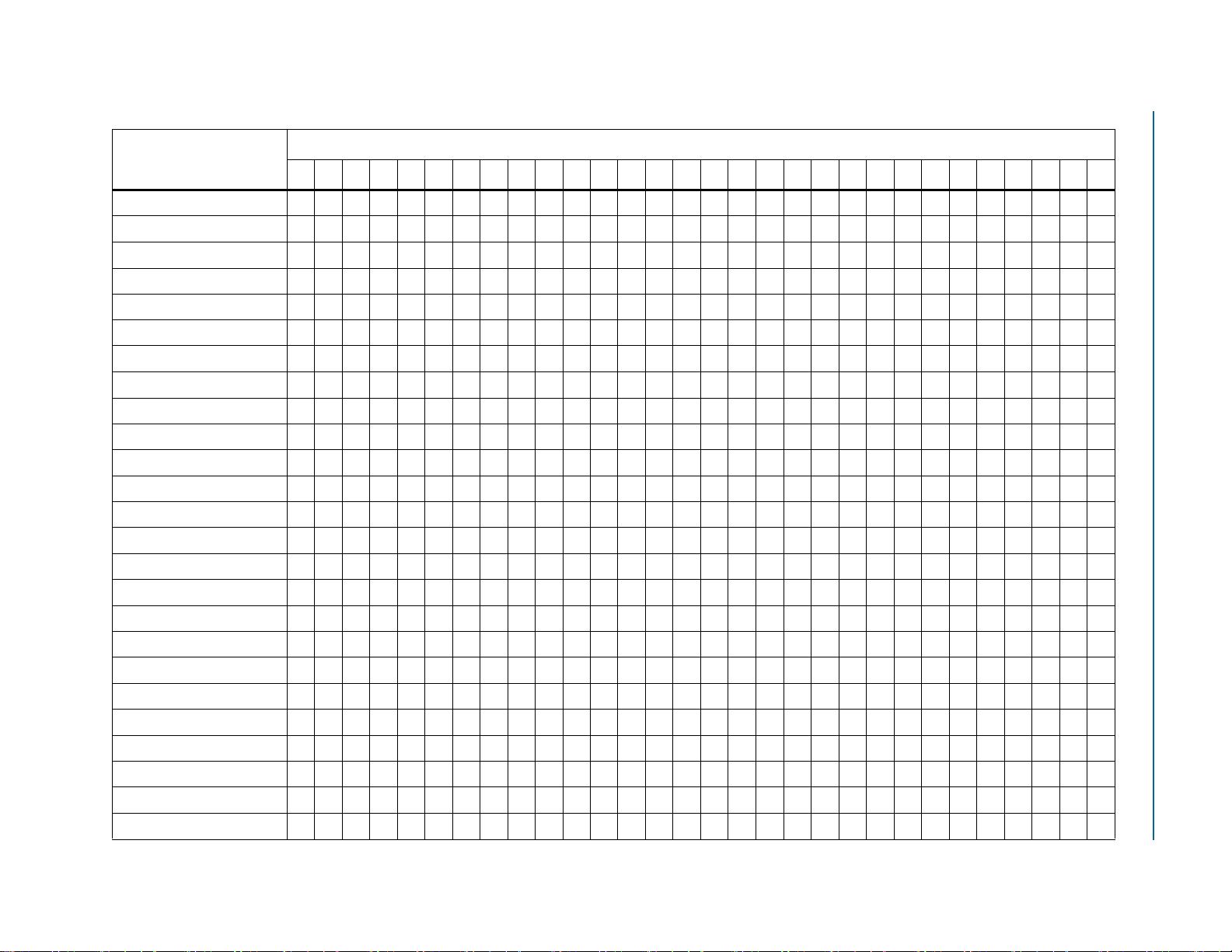

表 5-1. EP4CGX15, EP4CGX22 和 EP4CGX30G 的 CLK 网路连接

(1)

,

(2)

(1/2)

GCLK 网络时钟源

GCLK 网络

012345678910111213141516171819

CLK4/DIFFCLK_2n

—————

v

—

v

—

v

——————————

CLK5/DIFFCLK_2p

——————

vv

————————————

CLK6/DIFFCLK_3n

——————

v

—

vv

——————————

CLK7/DIFFCLK_3p

—————

v

——

v

———————————

CLK8/DIFFCLK_5n

——————————

v

—

v

—

v

—————

CLK9/DIFFCLK_5p

———————————

vv

———————

CLK10/DIFFCLK_4n/RE

FCLK1n

———————————

v

—

vv

—————

CLK11/DIFFCLK_4p/RE

FCLK1p

——————————

v

——

v

——————

CLK12/DIFFCLK_7p/RE

FCLK0p

———————————————

v

—

v

—

v

CLK13/DIFFCLK_7n/RE

FCLK0n

————————————————

vv

——

CLK14/DIFFCLK_6p

————————————————

v

—

vv

CLK15/DIFFCLK_6n

———————————————

v

——

v

—

PLL_1_C0

v

——

v

———————————

v

——

v

—

PLL_1_C1

—

v

——

v

———————————

v

——

v

PLL_1_C2

v

—

v

————————————

v

—

v

——

PLL_1_C3

—

v

—

v

————————————

v

—

v

—

PLL_1_C4

——

v

—

v

————————————

v

—

v

PLL_2_C0

v

——

v

——————

v

——

v

——————

PLL_2_C1

—

v

——

v

——————

v

——

v

—————

PLL_2_C2

v

—

v

———————

v

—

v

———————

PLL_2_C3

—

v

—

v

———————

v

—

v

——————

PLL_2_C4

——

v

—

v

———————

v

—

v

—————

PLL_3_C0

—————

v

——

v

——————

v

——

v

—

PLL_3_C1

——————

v

——

v

——————

v

——

v

Chapter 5: Cyclone IV 器件中的时钟网络与 PLL 5–3

时钟网络

Altera 公司 2011 年 11 月 Cyclone IV 器件手册,

卷 1

PLL_3_C2

—————

v

—

v

———————

v

—

v

——

PLL_3_C3

——————

v

—

v

———————

v

—

v

—

PLL_3_C4

———————

v

—

v

———————

v

—

v

PLL_4_C0

(3)

—————

v

——

v

—

v

——

v

——————

PLL_4_C1

(3)

——————

v

——

v

—

v

——

v

—————

PLL_4_C2

(3)

—————

v

—

v

——

v

—

v

———————

PLL_4_C3

(3)

——————

v

—

v

——

v

—

v

——————

PLL_4_C4

(3)

———————

v

—

v

——

v

—

v

—————

DPCLK2

————————————————

v

———

DPCLK3

(4)

——————————————————

v

—

DPCLK4

(4)

—————————————————

v

——

DPCLK5

———————————————————

v

DPCLK6

(4)

————————

v

———————————

DPCLK7

——————

v

—————————————

DPCLK8

—————————

v

——————————

DPCLK9

(4)

———————

v

————————————

DPCLK10

——————————————

v

—————

DPCLK11

(4)

————————————

v

———————

DPCLK12

(4)

—————————————

v

——————

DPCLK13

———————————

v

————————

表5-1注释:

(1) 该表中的 EP4CGX30 信息是指所有的 EP4CGX30 封装 ( 除了 F484 封装 )。

(2)

PLL_1

与

PLL_2

是多用 PLL,而

PLL_3

和

PLL_4

是通用 PLL。

(3)

PLL_4

仅在 F324 封装中的 EP4CGX22 与 EP4CGX30 器件中可用。

(4) 该管脚适用于 EP4CGX22 与 EP4CGX30 器件。

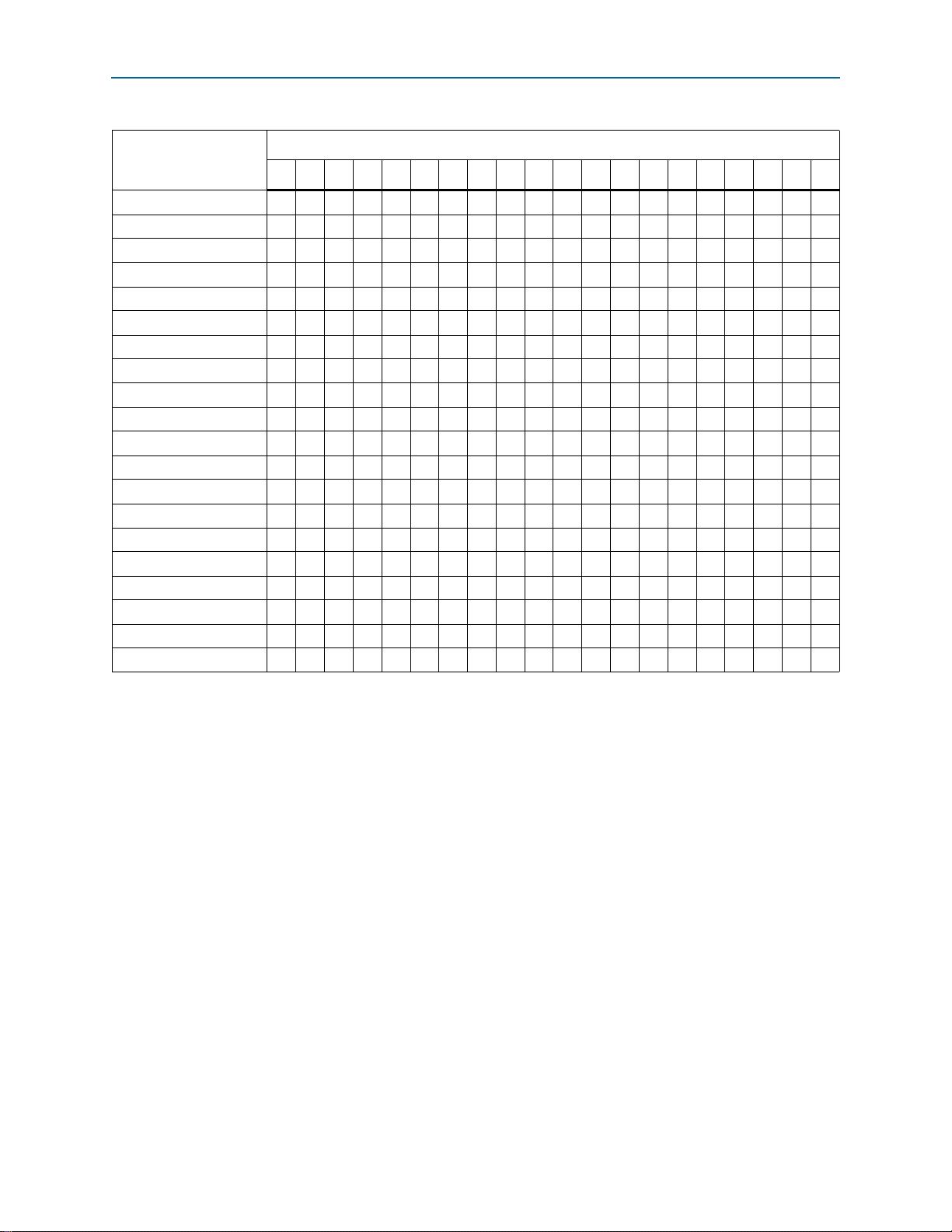

表 5-1. EP4CGX15, EP4CGX22 和 EP4CGX30G 的 CLK 网路连接

(1)

,

(2)

(2/2)

GCLK 网络时钟源

GCLK 网络

012345678910111213141516171819

5–4 Chapter 5: Cyclone IV 器件中的时钟网络与 PLL

时钟网络

Cyclone IV 器件手册, Altera 公司 2011 年 11 月

卷 1

表 5-2. EP4CGX30、EP4CGX50、EP4CGX75,EP4CGX110 和 EP4CGX150 器件的 GCLK 网络连接

(1)

,

(2)

(1/4)

GCLK 网络时钟源

GCLK 网络

01234567891011121314151617181920212223242526272829

CLKIO4/DIFFCLK_2n

————————————

v

—

v

—

v

—————————————

CLKIO5/DIFFCLK_2p

—————————————

vv

——

v

————————————

CLKIO6/DIFFCLK_3n

—————————————

v

—

vv

—————————————

CLKIO7/DIFFCLK_3p

————————————

v

——

v

—

v

————————————

CLKIO8/DIFFCLK_5n

——————————————————

v

—

v

—

v

———————

CLKIO9/DIFFCLK_5p

———————————————————

vv

——

v

——————

CLKIO10/DIFFCLK_4n/RE

FCLK3n

———————————————————

v

—

vv

——————

CLKIO11/DIFFCLK_4p/RE

FCLK3p

——————————————————

v

——

v

—

v

——————

CLKIO12/DIFFCLK_7p/RE

FCLK2p

————————————————————————

v

—

v

—

v

—

CLKIO13/DIFFCLK_7n/RE

FCLK2n

—————————————————————————

vv

——

v

CLKIO14/DIFFCLK_6p

—————————————————————————

v

—

vv

—

CLKIO15/DIFFCLK_6n

————————————————————————

v

——

v

—

v

PLL_1_C0

v

——

v

—

v

——————————————————

v

——

v

—

v

PLL_1_C1

—

v

——

v

————————————————————

v

——

v

—

PLL_1_C2

v

—

v

—————————————————————

v

—

v

———

PLL_1_C3

—

v

—

v

—————————————————————

v

—

v

——

PLL_1_C4

——

v

—

vv

————————————————————

v

—

vv

PLL_2_C0

——————

v

——

v

—

v

——————

v

——

v

—

v

——————

PLL_2_C1

———————

v

——

v

————————

v

——

v

———————

PLL_2_C2

——————

v

—

v

—————————

v

—

v

—————————

PLL_2_C3

———————

v

—

v

—————————

v

—

v

————————

PLL_2_C4

————————

v

—

vv

————————

v

—

vv

——————

Chapter 5: Cyclone IV 器件中的时钟网络与 PLL 5–5

时钟网络

Altera 公司 2011 年 11 月 Cyclone IV 器件手册,

卷1

PLL_3_C0

————————————

v

——

v

—

v

——————

v

——

v

—

v

PLL_3_C1

—————————————

v

——

v

————————

v

——

v

—

PLL_3_C2

————————————

v

—

v

—————————

v

—

v

———

PLL_3_C3

—————————————

v

—

v

—————————

v

—

v

——

PLL_3_C4

——————————————

v

—

vv

————————

v

—

vv

PLL_4_C0

————————————

v

——

v

—

vv

——

v

—

v

——————

PLL_4_C1

—————————————

v

——

v

——

v

——

v

———————

PLL_4_C2

————————————

v

—

v

———

v

—

v

—————————

PLL_4_C3

—————————————

v

—

v

———

v

—

v

————————

PLL_4_C4

——————————————

v

—

vv

——

v

—

vv

——————

PLL_5_C0

v

—

v

———————————————————————————

PLL_5_C1

——————————————————————————————

PLL_5_C2

——————————————————————————————

PLL_5_C3

—

v

—

v

——————————————————————————

PLL_5_C4

——

v

—

vv

————————————————————————

PLL_6_C0

v

——

v

—

v

————————————————————————

PLL_6_C1

——————————————————————————————

PLL_6_C2

——————————————————————————————

PLL_6_C3

——————————————————————————————

PLL_6_C4

—

v

——

v

—————————————————————————

PLL_7_C0

(3)

——————

v

——

v

—

v

——————————————————

PLL_7_C1

(3)

——————————————————————————————

PLL_7_C2

(3)

——————————————————————————————

PLL_7_C3

(3)

——————————————————————————————

PLL_7_C4

(3)

———————

v

——

v

———————————————————

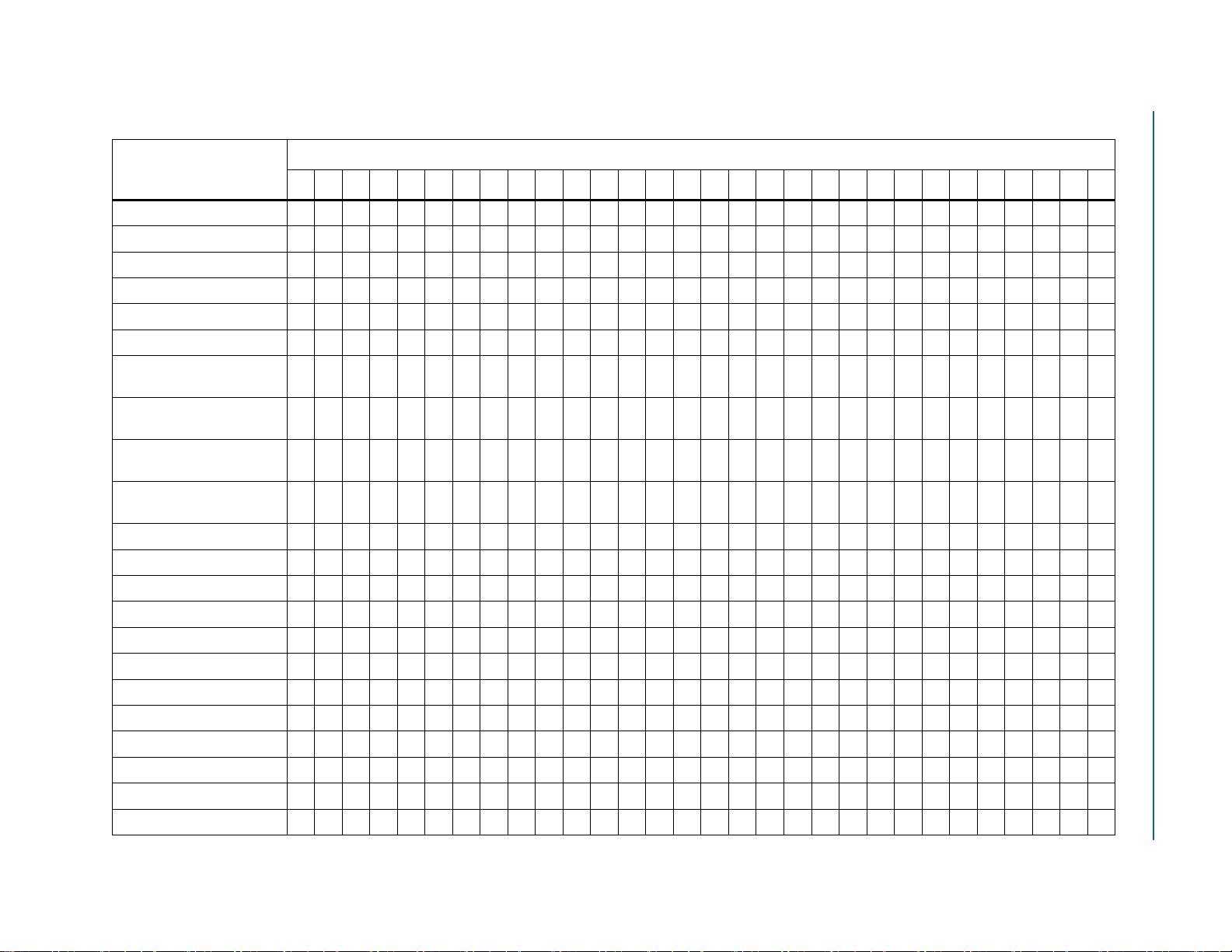

表 5-2. EP4CGX30、EP4CGX50、EP4CGX75,EP4CGX110 和 EP4CGX150 器件的 GCLK 网络连接

(1)

,

(2)

(2/4)

GCLK 网络时钟源

GCLK 网络

01234567891011121314151617181920212223242526272829

剩余41页未读,继续阅读

zhcniko

- 粉丝: 0

- 资源: 6

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 27页智慧街道信息化建设综合解决方案.pptx

- 计算机二级Ms-Office选择题汇总.doc

- 单链表的插入和删除实验报告 (2).docx

- 单链表的插入和删除实验报告.pdf

- 物联网智能终端项目设备管理方案.pdf

- 如何打造品牌的模式.doc

- 样式控制与页面布局.pdf

- 武汉理工Java实验报告(二).docx

- 2021线上新品消费趋势报告.pdf

- 第3章 Matlab中的矩阵及其运算.docx

- 基于Web的人力资源管理系统的必要性和可行性.doc

- 基于一阶倒立摆的matlab仿真实验.doc

- 速运公司物流管理模式研究教材

- 大数据与管理.pptx

- 单片机课程设计之步进电机.doc

- 大数据与数据挖掘.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0