AT89C51微控制器:低功耗高性能解决方案

"这篇文档是关于89C51单片机的一篇英文文献,讨论了该微控制器的低功耗、高性能特性以及其在嵌入式控制应用中的广泛适用性。89C51单片机内置4KB可编程和擦除只读存储器(Flash PEROM)和128字节的RAM,采用Atmel的高密度非易失性内存技术,兼容MCS-51指令集和引脚配置。"

本文档主要涵盖了89C51单片机的一些关键特性和功能,包括:

1. **兼容性**:89C51与MCS-51产品系列兼容,这意味着它遵循了业界标准的MCS-51指令集,这使得开发者能够利用已有的MCS-51开发经验来使用89C51。

2. **内存配置**:89C51具有4KB的在系统可重编程Flash内存,可以进行多次写入和擦除操作,具有1,000次的写/擦除周期,满足程序存储的需求。同时,它还配备有128字节的内部RAM,用于数据处理和临时存储。

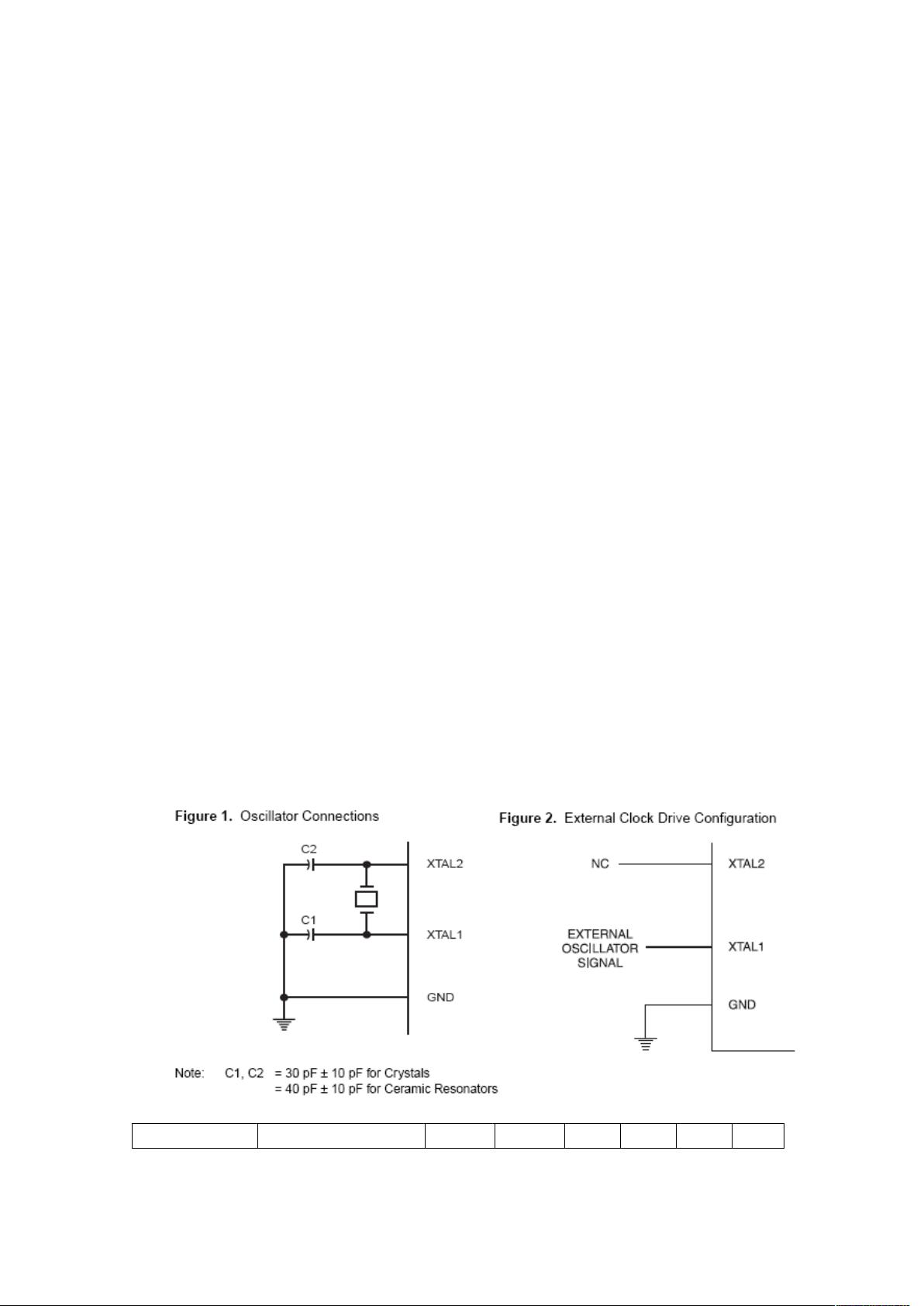

3. **静态操作**:该单片机可以在0Hz到24MHz的频率范围内工作,支持全静态操作,这意味着即使在无时钟输入的情况下也能保持其状态。

4. **安全保护**:具有三级程序存储器锁定功能,保证了代码的安全性,防止未经授权的访问或修改。

5. **输入/输出(I/O)**:提供32条可编程的I/O线路,这些线路可以灵活配置为输入或输出,以适应各种外设连接。

6. **定时器/计数器**:包含两个16位的定时器/计数器,这是许多实时控制应用中不可或缺的组成部分,可以用于脉冲测量、定时任务等。

7. **中断源**:具备六个中断源,提供了灵活的中断处理机制,能够对系统事件作出快速响应。

8. **串行通信**:拥有一个可编程的串行通道,可用于UART(通用异步接收发送器)通信,支持与其他设备的数据交换。

9. **低功耗模式**:支持低功耗闲置模式和电源关闭模式,这两种模式在不牺牲性能的前提下,降低了单片机在非活动状态下的能耗,适合电池供电或者对功耗敏感的应用。

89C51单片机因其丰富的功能集、兼容性和灵活性,在嵌入式控制系统设计中得到了广泛应用,如家用电器、工业自动化、汽车电子等领域。这篇文献对于理解89C51的硬件特性、设计考虑和应用潜力提供了详尽的信息。

2022-07-14 上传

2023-06-29 上传

2021-05-14 上传

2021-05-12 上传

2023-07-10 上传

2023-06-29 上传

Haoyiding

- 粉丝: 0

- 资源: 6

最新资源

- Android应用源码仿支付宝九宫格解锁-IT计算机-毕业设计.zip

- BostonUnderwater:洪水检测网络 - 使用 GoogleMaps 和 Amcharts 集成记录远程洪水

- Elixir_in_action:我对《 Elixir in Action》一书中程序的实现

- 萝拉:萝拉图片网站

- Meta:Python元编程

- 基于Pytorch, 使用强化学习(自博弈+MCTS)训练一个五子棋AI.zip

- AxaTests

- WISE_ML:明智的机器学习模块

- 移动实习——基于移动终端用户画像的大规模数据过滤与性能优化研究 7.17-8.25.zip

- k8s研究

- website:个人网站

- JavaScript-Calculator

- asteroidstest

- 行业文档-设计装置-一种利用牛奶盒制作宣纸配方.zip

- flutter_practice

- nkn-monitoring:PHP(Laravel)上的一个简单的NKN节点监视GUI工具