没有合适的资源?快使用搜索试试~ 我知道了~

首页DDR3 硬件设计和 Layout 设计【中为电子科技工作室】

资源详情

资源评论

资源推荐

爱手册爱翻译 中为电子科技

2 / 13

目录

1 设计检查表 ................................................................................................................................. 3

2 终端匹配电阻功耗计算 ............................................................................................................. 8

3 VREF ............................................................................................................................................ 8

4 VTT 电压轨 ................................................................................................................................. 8

5 DDR 布线 .................................................................................................................................... 9

5.1 数据线 — MDQ[0:63], MDQS[0:8], MDM[0:8], MECC[0:7] .......................................... 9

5.2 Layout 建议 .................................................................................................................. 10

6 仿真 .......................................................................................................................................... 12

7 扩展阅读................................................................................................................................... 13

8 历史版本................................................................................................................................... 13

9 声明 .......................................................................................................................................... 13

爱手册爱翻译 中为电子科技

3 / 13

这是一篇关于 DDR3 SDRAM IP core 的设计向导,出自飞思卡尔,为了实现 PCB 的灵活

设计,我们可以采用合适的拓扑结构简化设计时的板级关联性。

飞思卡尔强烈推荐系统/板级工程师在 PCB 制板前进行设计验证,包括信号完整性、时

序等等。

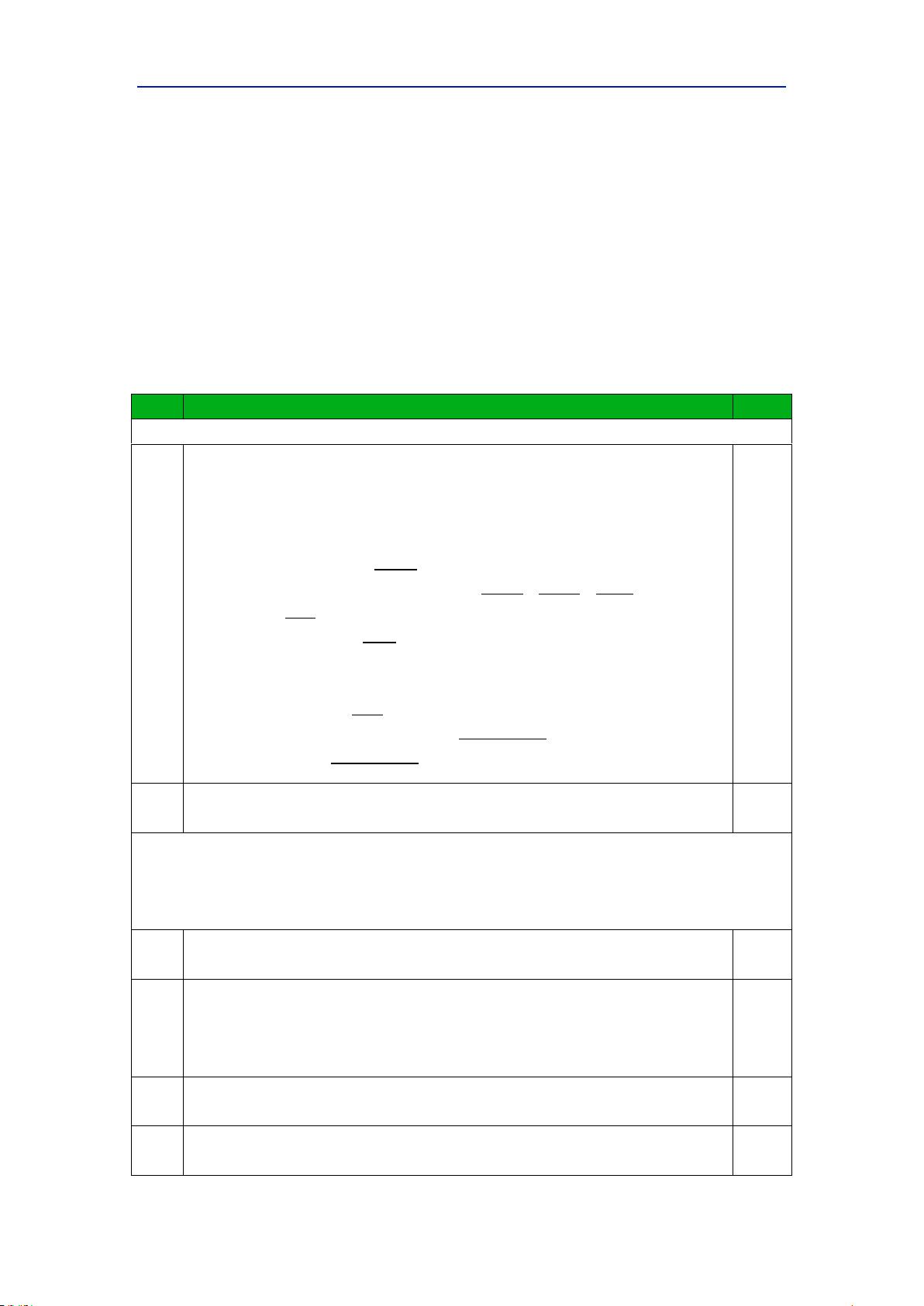

1 设计检查表

如表 1,罗列了 DDR 设计检查清单,推荐逐一检查,并在最右侧作出决策。

表 1 DDR3 检查清单

序号

描述

是/否

仿真

1

是否最优化了①终端匹配电阻值、②信号线拓扑、③走线长度等?这些项目

最好通过仿真进行优化!

假如在 DDR 和控制器间应用了 ODT(on-die termination)技术,那么在数据

总线上就不需要额外的终端匹配电阻了。

DDR 分组要求如下:

■ 数据组:MDQS(8:0),(8:0),MDM(8:0),MDQ(63:0),MECC(7:0)

■ 地址/命令组:MBA(2:0),MA(15:0),,,

■ 控制组:(3:0),MCKE(3:0),MODT(3:0)

■ 时钟组:MCK(5:0),(5:0)

数据组走线共计 72 位(64bit + 8bit ECC<ECC 是 Error Checking and Correcting

的简写,即是错误检查和纠正,这种技术多用在服务器中>)。有些产品可能

只有 32 位数据线并且、MCKE 和 MODT 也少一些。有些产品包含支持

DIMMs 注册的信号线 MAPAR_OUT 和,其中 MAPAR_OUT 应归

类为地址/命令组,作为一个异步信号。

2

所有 DDR 芯片信号的终端匹配方案是否满足 AC 参数(电平、转换速率、过

冲和下冲等)。

终端匹配方案

设计者应该采用主流的终端匹配方案,像商业电脑主板那样的设计,ODT 终端匹配被应用在

数据总线上,地址/命令和控制线也应通过电阻连接到 VTT。当然,其它的终端匹配也是有

效的,但最好通过仿真来验证,确保信号质量满足要求。

3

终端匹配电阻的选择,其功耗是否满足芯片制造商的要求。

功耗计算 Power =

x RT

4

假如数据线组增加了外部终端匹配电阻,请查看数据线组是否与其他 DDR3

信号组远离/隔离。

注:因为在 DDR3 数据组中通常优先选用内部 ODT 终端匹配,额外电阻是不

需要的。当然,假如不用 ODT 电阻,那么就需要增设外部电阻器了。

5

请查看 VTT 电阻 RT 布局是否正确,RT 终端电阻应该直接连接到 DDR 总线末端

和 VTT 电源平面上。

6

DDR 芯片的时钟线是否设置了差分终端匹配(DIMM 模块常用这种匹配方

式),一般终端匹配电阻选取 100 ~ 120Ω 。

剩余12页未读,继续阅读

普通网友

- 粉丝: 5

- 资源: 41

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

- MW全能培训汽轮机调节保安系统PPT教学课件.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论6