VHDL&Verilog安全编码规范与最佳实践

需积分: 10 118 浏览量

更新于2024-07-16

收藏 1.19MB PPTX 举报

该资源是关于VHDL和Verilog两种硬件描述语言的安全编码要求的讲解,适合FPGA开发人员参考。文档详细介绍了这两种语言的基本概念、程序结构以及编码时需要注意的关键点,旨在提高设计质量和可维护性。

VHDL(Very-High-Speed Integrated Circuit Hardware Description Language)是一种用于描述数字系统硬件结构和行为的高级语言,主要用于 FPGA 和 ASIC 设计。Verilog,另一种硬件描述语言,同样用于描述电子系统的硬件行为,且SystemVerilog在其基础上进行了扩展,增加了更多高级特性,如断言、验证平台等,强化了设计模型构建和验证流程。

在VHDL和Verilog的程序结构中,VHDL有库声明、实体、构造体、敏感列表、循环控制、例化、分支控制、结构设计、状态机、运算、时钟、复位及初始化、命名、综合约束和注释等类别。而Verilog的程序结构包括敏感列表、类、循环控制、例化、分支控制、结构设计等。两者在编码规范上有一些共通的要求,例如:

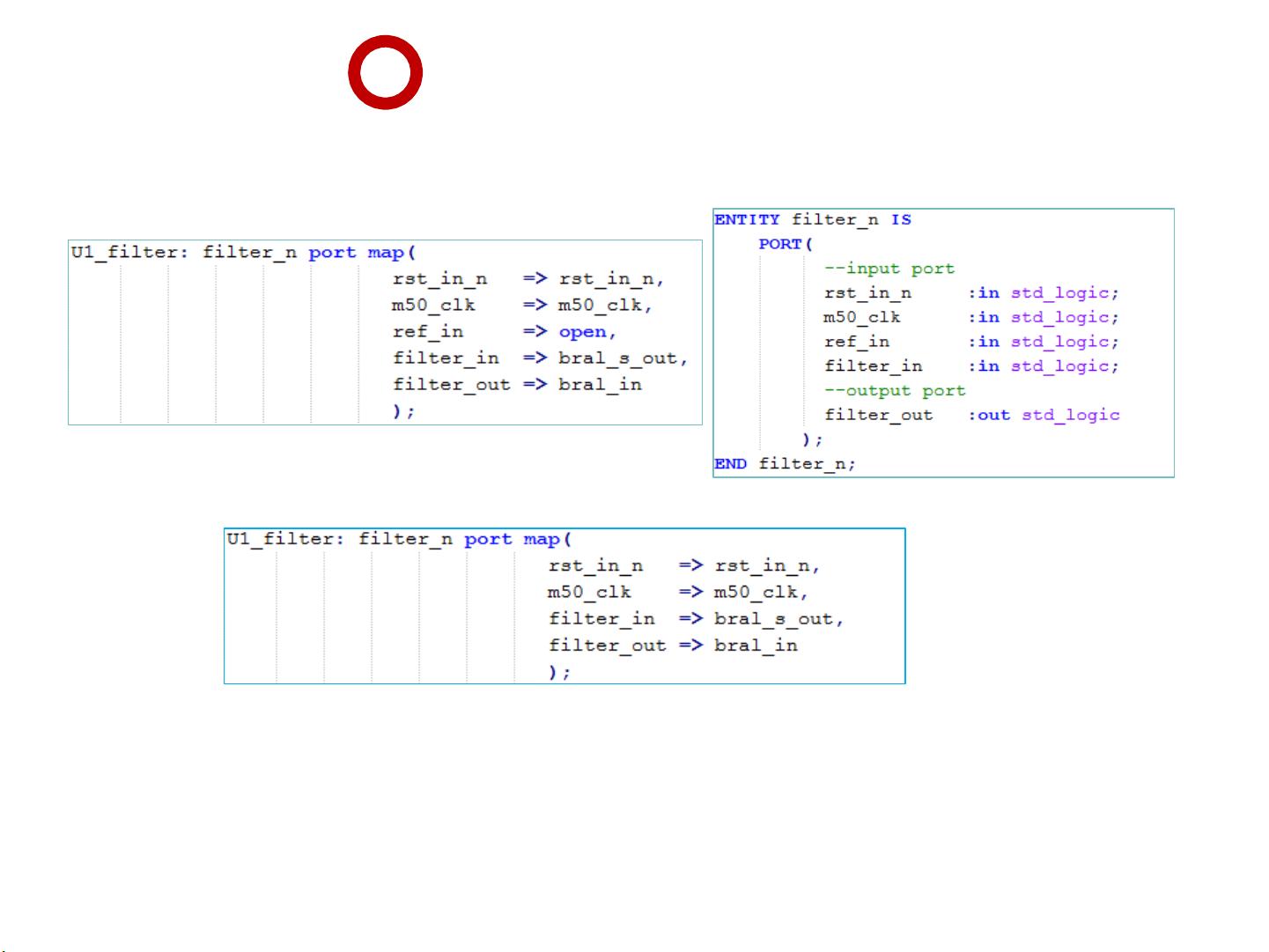

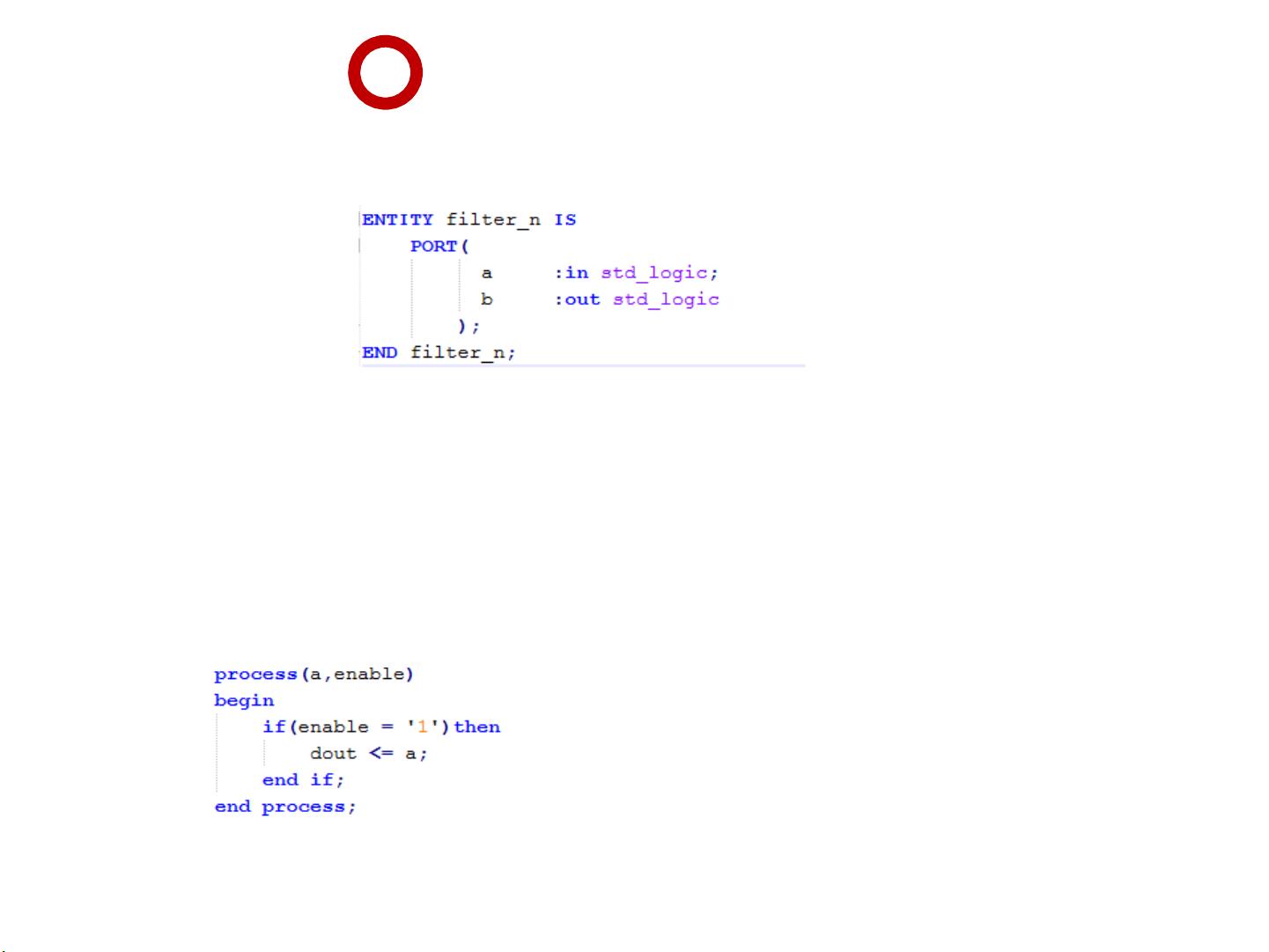

1. **端口例化**:推荐使用名称映射而非位置映射,这样更清晰且减少出错可能。同时,例化时要避免输入端口悬空,确保每个端口都有明确的连接。

2. **结构设计**:内部信号应避免使用三态逻辑,因为这可能导致不确定的行为。输出信号通常不应直接驱动同一模块的内部逻辑,除非是双向端口。设计中应避免产生非预期的锁存器,这通常是因为条件语句(如if-then-else,case-when等)缺少else部分导致。

3. **模块划分**:顶层模块宜实现模块例化,以保持设计的清晰度。模块划分应基于功能独立性,根据不同的设计目标来划分。组合逻辑和可复用逻辑应尽可能在同一模块层次中。

4. **敏感信号列表**:应确保列表完整且正确,以确保模块正确响应输入变化。

5. **状态机设计**:状态机需要处理无效状态,通过综合属性设置确保无效状态的处理有效。定义类型state并声明信号,例如`type state is (s0, s1, s2, s3, s4, s5); signal next_state, current_state : state;`

对于FPGA开发人员来说,遵循这些编码要求可以提高代码的可读性、可维护性和可靠性,降低设计错误的可能性,从而提升整个设计流程的效率。在使用Xilinx ISE、Vivado、Actel Libero、Altera Quartus或Lattice ISE等不同开发环境时,理解并应用这些规则尤其重要。

2021-10-07 上传

2021-10-07 上传

2022-11-13 上传

2021-10-07 上传

2021-03-15 上传

2022-01-18 上传

2021-10-02 上传

2021-10-07 上传

2023-07-26 上传