FPGA实现CAN总线通信节点设计与Verilog软件设计

44 浏览量

更新于2023-05-03

3

收藏 411KB PDF 举报

"基于FPGA的CAN总线通信节点设计,使用SJA1000作为CAN控制器,FPGA作为主控制器,通过Verilog语言实现通信功能。"

在现代自动化控制系统中,CAN(Controller Area Network)总线因其高速、可靠的通信能力而被广泛采用。CAN总线最高通信速率可达1Mbps,支持多个主机同时通信,具备优秀的抗干扰性和错误检测机制。在某些特定项目需求下,使用FPGA(Field-Programmable Gate Array)作为主控制器替代传统的单片机,能更好地满足速度、体积和灵活性的需求。

FPGA的优势在于其可编程性和高集成度,可以简化硬件设计,减少电路板的复杂性,同时缩短产品开发周期。FPGA内部的丰富资源使得它能高效地处理复杂的并行任务,增强了系统的可靠性和扩展性。

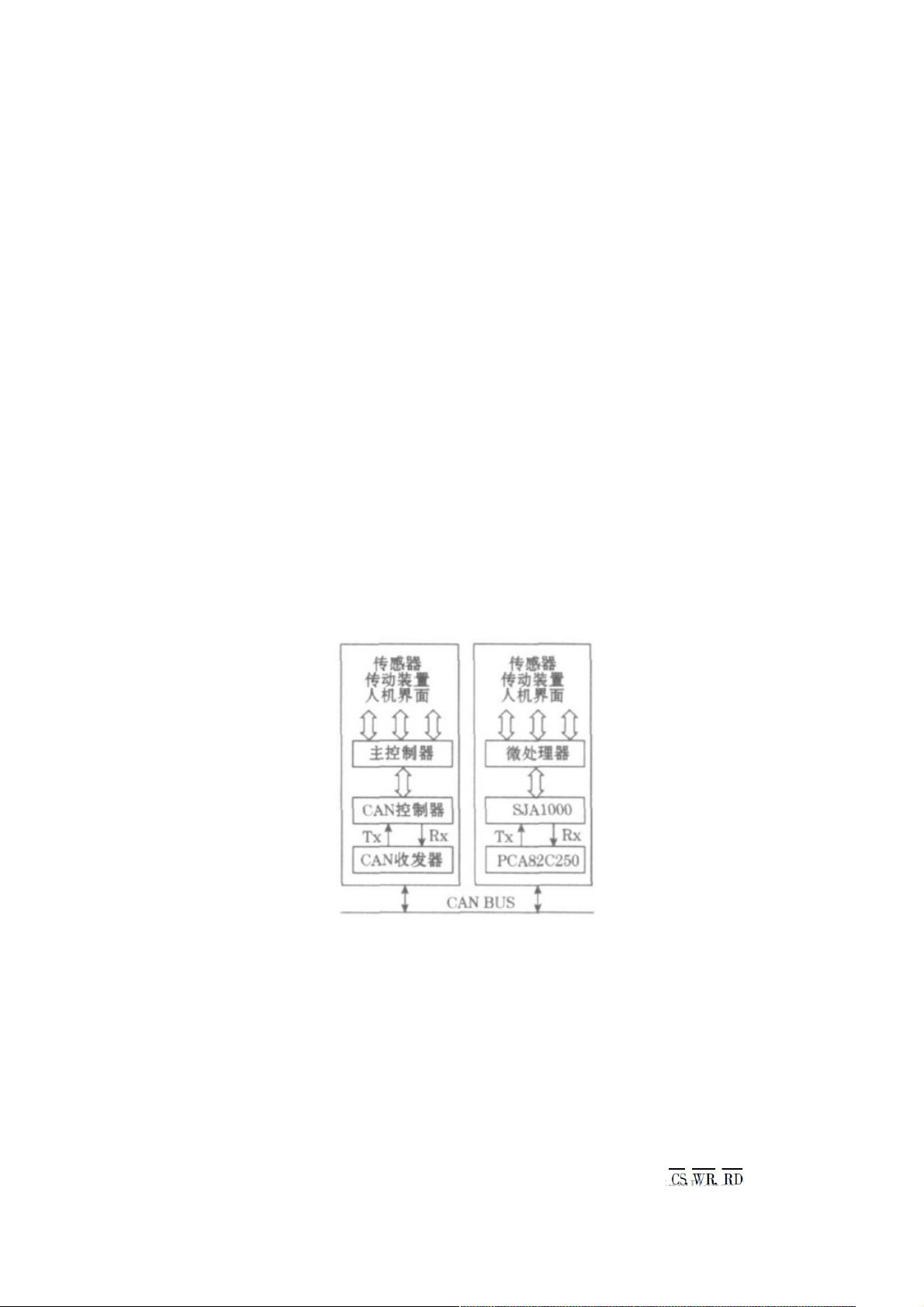

在基于FPGA的CAN总线通信节点设计中,主要分为硬件接口设计和软件设计两个部分。硬件设计包括以下几个关键组件:

1. **CAN总线控制器**:SJA1000是一个常见的CAN控制器,它符合ISO 11898标准,负责执行CAN协议的底层功能,如位仲裁、错误检测和报文过滤。

2. **FPGA主控制器**:FPGA与SJA1000连接,作为系统的核心,处理高层应用逻辑,如数据处理、命令控制和状态管理。FPGA的灵活性使得它可以灵活配置,适应不同应用场景。

3. **CAN收发器**:连接CAN控制器与物理总线,转换逻辑电平信号以适应总线传输。收发器对于确保总线的电气特性至关重要,影响通信距离和网络规模。

在软件设计方面,通常使用硬件描述语言(如Verilog)编程实现CAN节点间的通信功能。Verilog代码定义了FPGA如何与SJA1000交互,控制数据的发送和接收,以及处理协议相关的控制信号。通过编程,可以定制通信协议,实现特定的报文格式和通信策略。

1. **接口设计**:FPGA需要配置适当的输入/输出(I/O)端口,与SJA1000进行数据交换,包括接收数据线、发送数据线、时钟信号、中断请求等。

2. **报文处理**:FPGA根据CAN控制器提供的报文信息,进行数据解析或构建新的报文,以实现节点间的有效通信。

3. **错误管理**:FPGA应能检测并处理由CAN总线控制器报告的错误,如位错误、帧错误等,确保数据的完整性和正确性。

4. **仲裁与同步**:在多主CAN网络中,FPGA还需要处理报文的仲裁过程,确保数据传输的顺序和同步。

通过这样的设计,基于FPGA的CAN总线通信节点不仅提高了通信效率,还降低了系统复杂性,为实时控制和大规模网络部署提供了有效的解决方案。同时,FPGA的可重构性也使得系统能够快速适应未来可能的变化和升级需求。

2020-10-24 上传

2020-10-24 上传

2020-10-24 上传

2021-07-13 上传

2020-10-21 上传

2021-07-13 上传

2010-06-01 上传

2021-07-13 上传

2024-03-15 上传

weixin_38623707

- 粉丝: 5

- 资源: 923

最新资源

- CoreOS部署神器:configdrive_creator脚本详解

- 探索CCR-Studio.github.io: JavaScript的前沿实践平台

- RapidMatter:Web企业架构设计即服务应用平台

- 电影数据整合:ETL过程与数据库加载实现

- R语言文本分析工作坊资源库详细介绍

- QML小程序实现风车旋转动画教程

- Magento小部件字段验证扩展功能实现

- Flutter入门项目:my_stock应用程序开发指南

- React项目引导:快速构建、测试与部署

- 利用物联网智能技术提升设备安全

- 软件工程师校招笔试题-编程面试大学完整学习计划

- Node.js跨平台JavaScript运行时环境介绍

- 使用护照js和Google Outh的身份验证器教程

- PHP基础教程:掌握PHP编程语言

- Wheel:Vim/Neovim高效缓冲区管理与导航插件

- 在英特尔NUC5i5RYK上安装并优化Kodi运行环境