Vivado FIFO Generator 13.2:技术指南与设计流程

需积分: 50 53 浏览量

更新于2023-05-14

收藏 4.04MB PDF 举报

“pg057-fifo-generator.pdf”是Xilinx Vivado Design Suite的一个文档,主要介绍了FIFO Generator v13.2版本的LogiCORE IP产品指南。这份指南涵盖了FIFO核的基本概念、特性、应用、设计指导、设计流程步骤以及详细示例设计等内容。

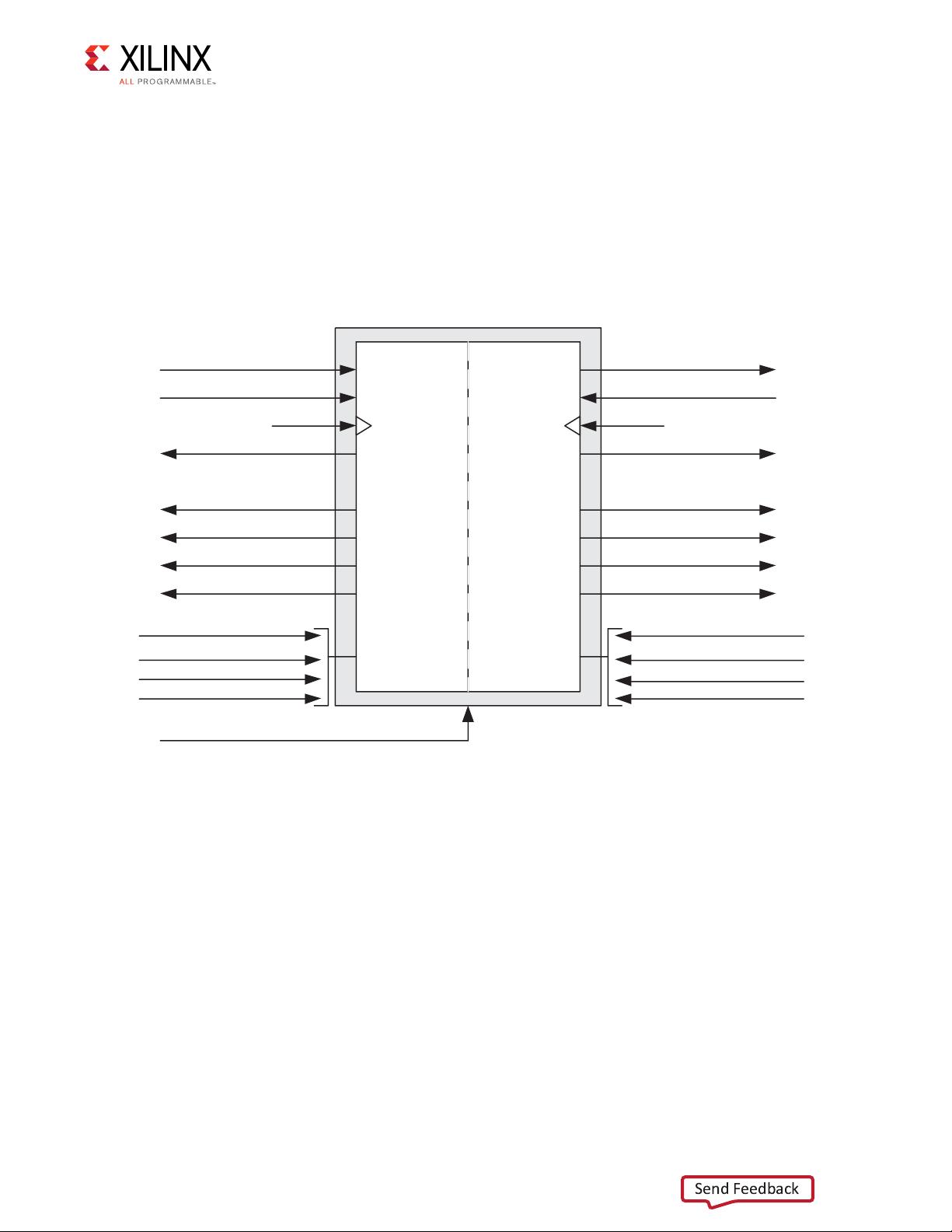

在FPGA设计中,FIFO(First In First Out,先进先出)存储器常用于数据缓冲和通信接口之间数据流的同步。FIFO Generator提供了两种接口类型:本征接口FIFOs和AXI接口FIFOs。本征接口FIFOs直接与硬件逻辑连接,而AXI接口FIFOs则采用了Xilinx的Advanced eXtensible Interface (AXI),提供了一种标准的接口来处理高速数据传输。

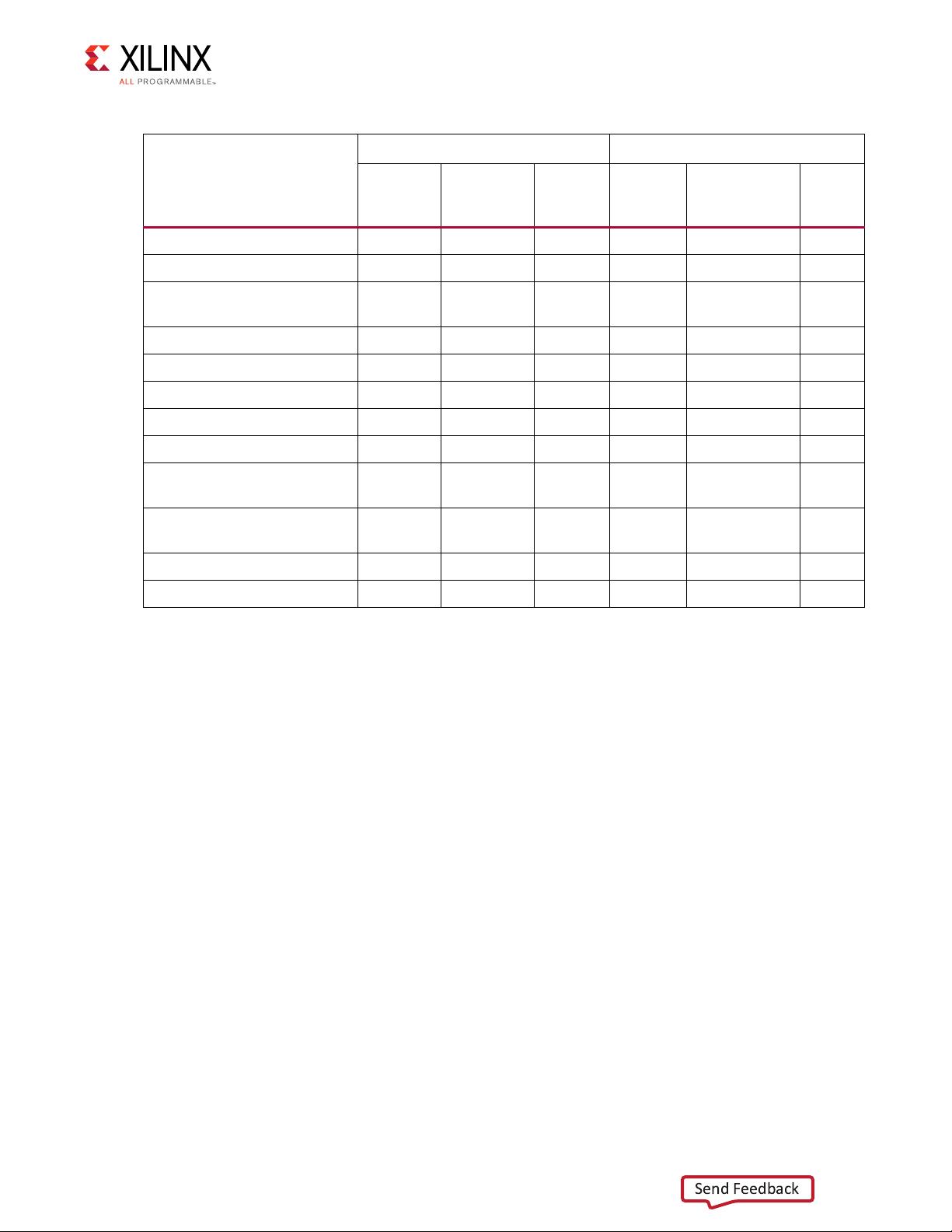

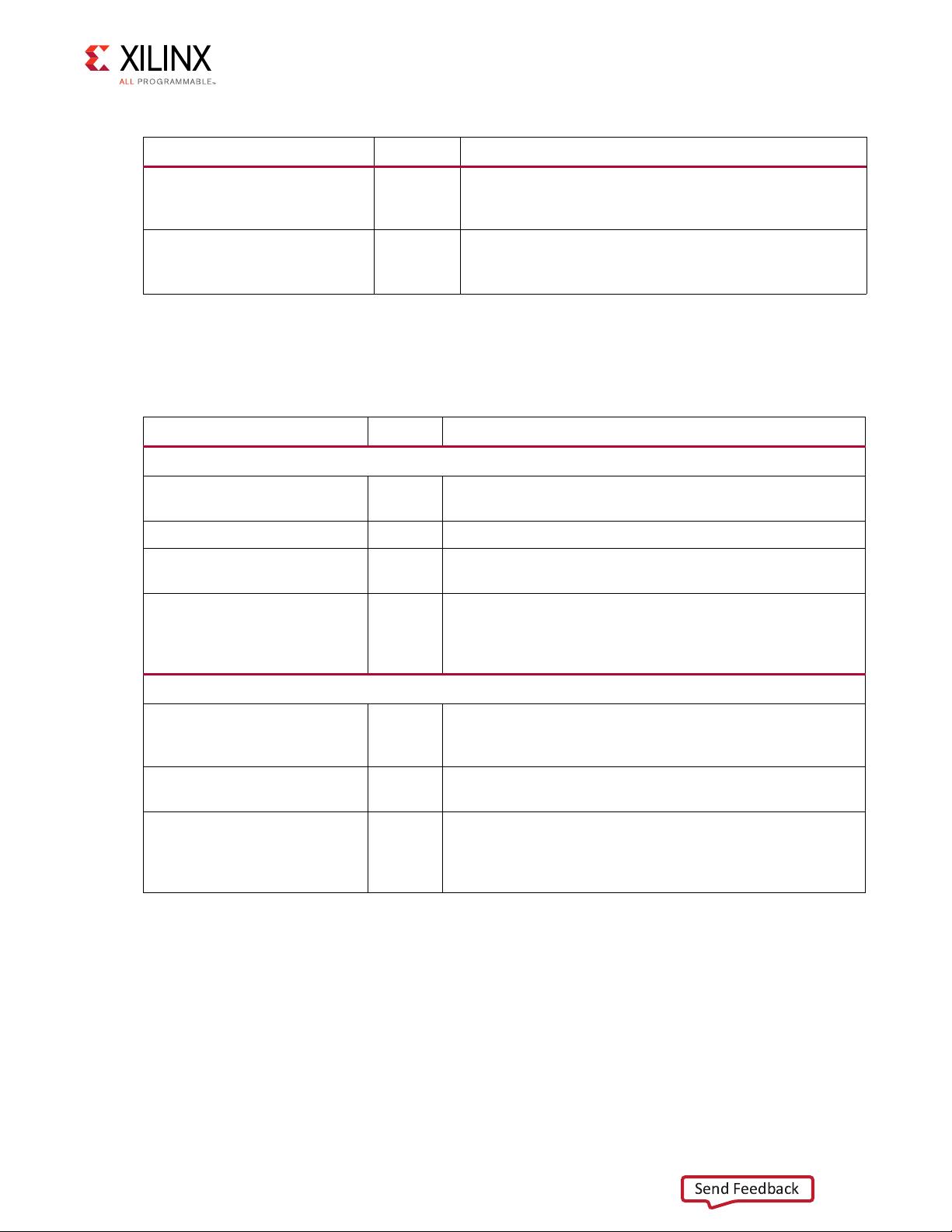

FIFO Generator v13.2的特性总结包括各种性能指标、资源利用率、端口描述等。性能部分详细列出了FIFO在不同条件下的工作表现,资源利用率章节展示了在实现FIFO核时, FPGA资源如查找表(LUTs)、触发器(FFs)等的消耗情况。端口描述部分解释了FIFO核各个输入和输出信号的功能和用途。

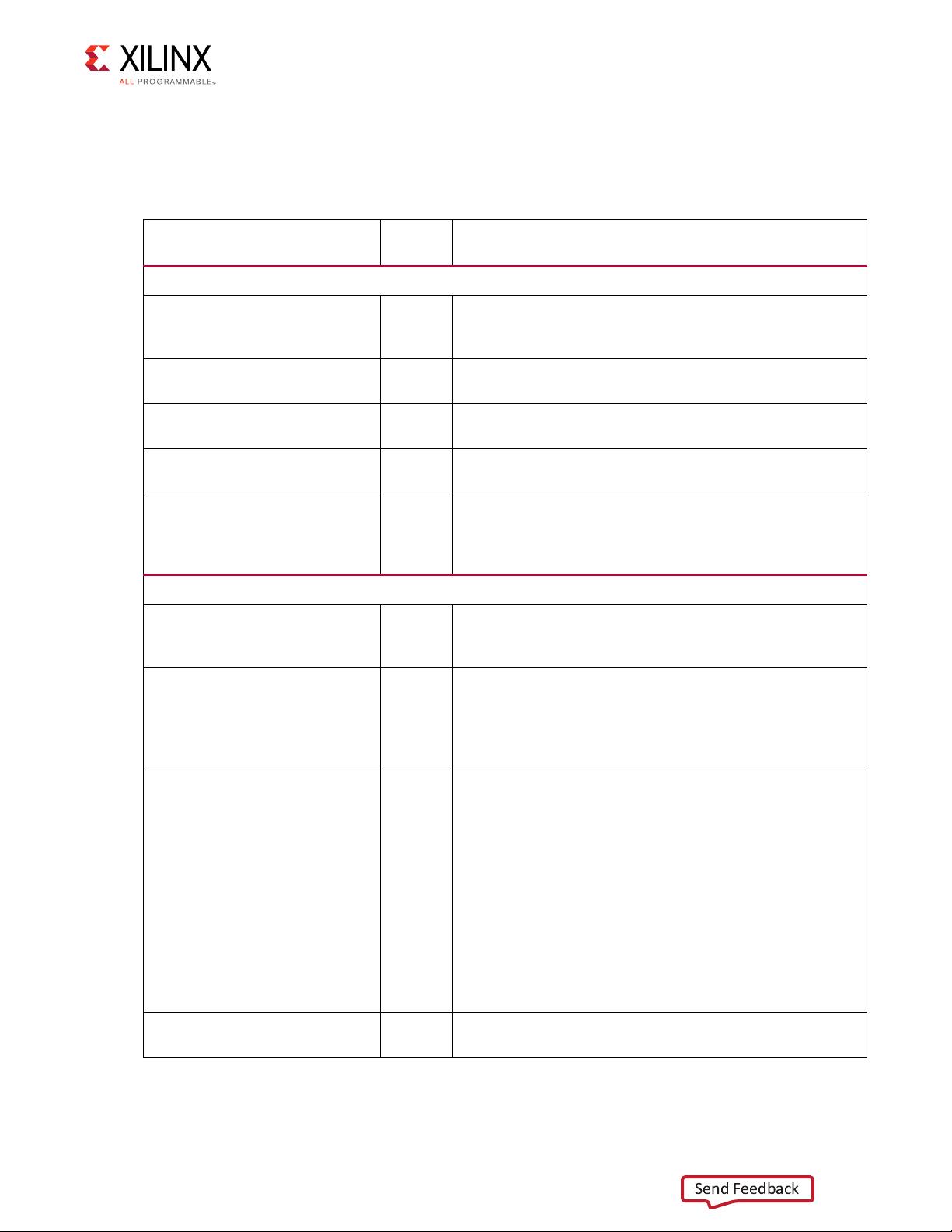

设计指导部分提供了使用FIFO Generator的一般性建议,例如初始化FIFO、FIFO的使用和控制、时钟管理、复位处理、实际FIFO深度计算、延迟以及特殊设计考虑等。这些内容对理解如何在具体项目中正确配置和使用FIFO核至关重要。

设计流程步骤章节详细介绍了定制和生成本征核心或AXI核心的步骤,包括约束设置、仿真、综合和实现过程。这为开发者提供了完整的流程指导,帮助他们将FIFO核集成到自己的设计中。

在详细示例设计章节,用户可以学习如何实施示例设计,以及如何进行仿真验证。测试台部分讨论了测试台功能,以及如何自定义演示测试台,以适应特定的设计需求,并处理可能遇到的消息和警告。

这份文档是针对Xilinx Vivado用户的FIFO Generator使用手册,提供了全面的技术信息和支持,对于理解和使用FIFO核进行FPGA设计非常有帮助。

2022-09-19 上传

2022-09-21 上传

2024-05-10 上传

2024-05-10 上传

2023-07-26 上传

2022-11-19 上传

Gate_coding

- 粉丝: 10

- 资源: 17

最新资源

- 全国江河水系图层shp文件包下载

- 点云二值化测试数据集的详细解读

- JDiskCat:跨平台开源磁盘目录工具

- 加密FS模块:实现动态文件加密的Node.js包

- 宠物小精灵记忆配对游戏:强化你的命名记忆

- React入门教程:创建React应用与脚本使用指南

- Linux和Unix文件标记解决方案:贝岭的matlab代码

- Unity射击游戏UI套件:支持C#与多种屏幕布局

- MapboxGL Draw自定义模式:高效切割多边形方法

- C语言课程设计:计算机程序编辑语言的应用与优势

- 吴恩达课程手写实现Python优化器和网络模型

- PFT_2019项目:ft_printf测试器的新版测试规范

- MySQL数据库备份Shell脚本使用指南

- Ohbug扩展实现屏幕录像功能

- Ember CLI 插件:ember-cli-i18n-lazy-lookup 实现高效国际化

- Wireshark网络调试工具:中文支持的网口发包与分析