ALINX黑金Zynq7000开发平台教程V1.03:入门与实战指南

需积分: 50 162 浏览量

更新于2023-05-15

收藏 20.06MB PDF 举报

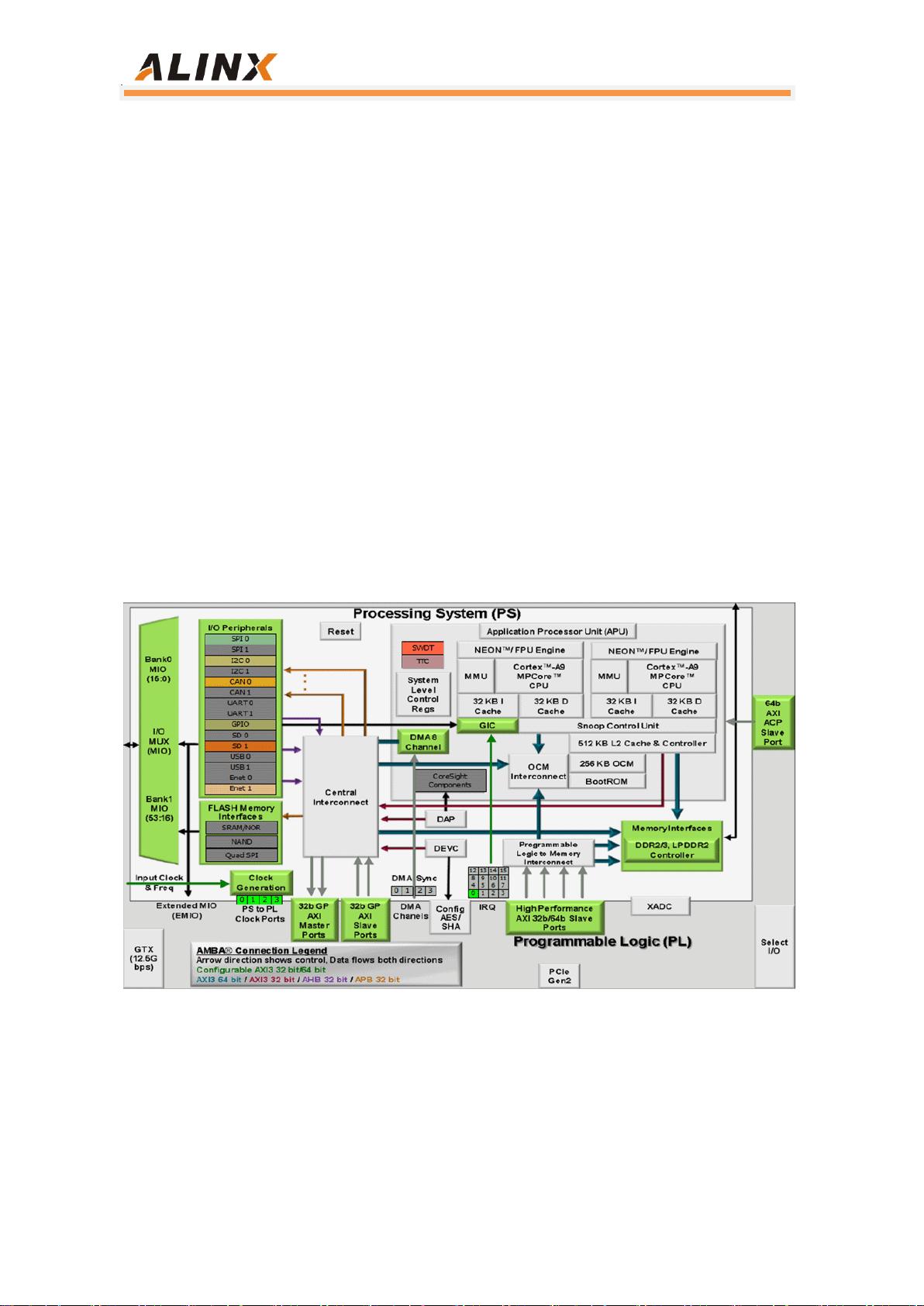

ALINX黑金Zynq7000开发平台是一款针对赛灵思Zynq7000 SoC芯片的高性能开发工具包,由ALINX黑金动力社区开发。这款平台主要包括两个型号的开发板,即AX7010和AX7020,它们集成了双核ARM Cortex-A9处理器和FPGA fabric,这种集成显著提升了处理速度和系统性能。

该配套教程V1.03是一个详尽的指南,旨在帮助用户从入门到深入理解Zynq7000平台的使用。教程分为四个部分:

1. 基础篇:这一部分主要介绍了开发板的上电测试、硬件电路结构、ZYNQ芯片的特性、Vivado软件的安装、Linux系统虚拟机的配置以及PS(处理器子系统)和PL(可编程逻辑子系统)接口的原理。通过这部分的学习,用户能够对开发板及其功能有全面的认识,并了解基本的开发流程。

2. 逻辑篇:此部分专注于将Zynq芯片作为普通的FPGA来使用,通过开发板的硬件资源,引导用户进行纯逻辑设计和Verilog程序的编写实践。通过实际应用案例,使学习者掌握FPGA设计和实现的核心技能。

3. 进阶篇或应用篇:这部分可能包括了更高级的主题,如嵌入式系统设计、系统级编程、软件定义硬件(SDH)应用、以及如何利用Zynq的软硬件协同特性等。

4. 持续更新与支持:ALINX黑金团队承诺持续根据用户的反馈和开发经验进行教程的修正和优化,体现了其对提供最新、最有效的学习资料的重视。截至2017年2月,已经发布了V1.03版本,反映了团队对教程内容的不断完善。

购买并使用ALINX黑金Zynq7000开发平台的用户,不仅可以得到硬件设备的支持,还能获得一套完整且易于理解的教程,这对于想要涉足ARM+FPGA SoC技术的学习者来说,无疑是一个极具价值的资源。通过这个教程,用户将逐步提升自己的Zynq7000开发能力,适应快速发展的半导体技术领域。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2018-12-18 上传

2020-03-11 上传

2021-05-23 上传

2020-04-26 上传

点击了解资源详情

2024-10-27 上传

lucjn

- 粉丝: 13

- 资源: 198

最新资源

- CoreOS部署神器:configdrive_creator脚本详解

- 探索CCR-Studio.github.io: JavaScript的前沿实践平台

- RapidMatter:Web企业架构设计即服务应用平台

- 电影数据整合:ETL过程与数据库加载实现

- R语言文本分析工作坊资源库详细介绍

- QML小程序实现风车旋转动画教程

- Magento小部件字段验证扩展功能实现

- Flutter入门项目:my_stock应用程序开发指南

- React项目引导:快速构建、测试与部署

- 利用物联网智能技术提升设备安全

- 软件工程师校招笔试题-编程面试大学完整学习计划

- Node.js跨平台JavaScript运行时环境介绍

- 使用护照js和Google Outh的身份验证器教程

- PHP基础教程:掌握PHP编程语言

- Wheel:Vim/Neovim高效缓冲区管理与导航插件

- 在英特尔NUC5i5RYK上安装并优化Kodi运行环境