5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

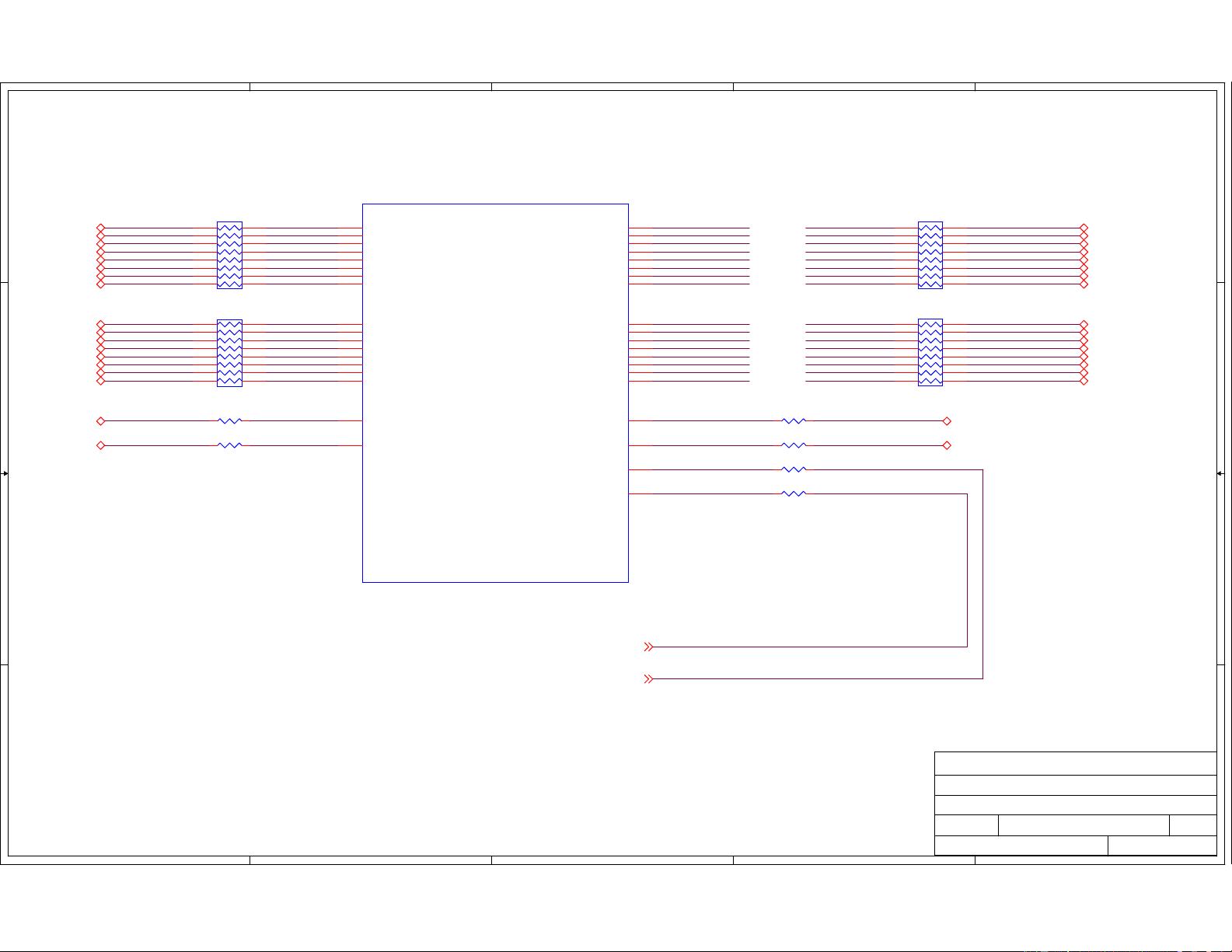

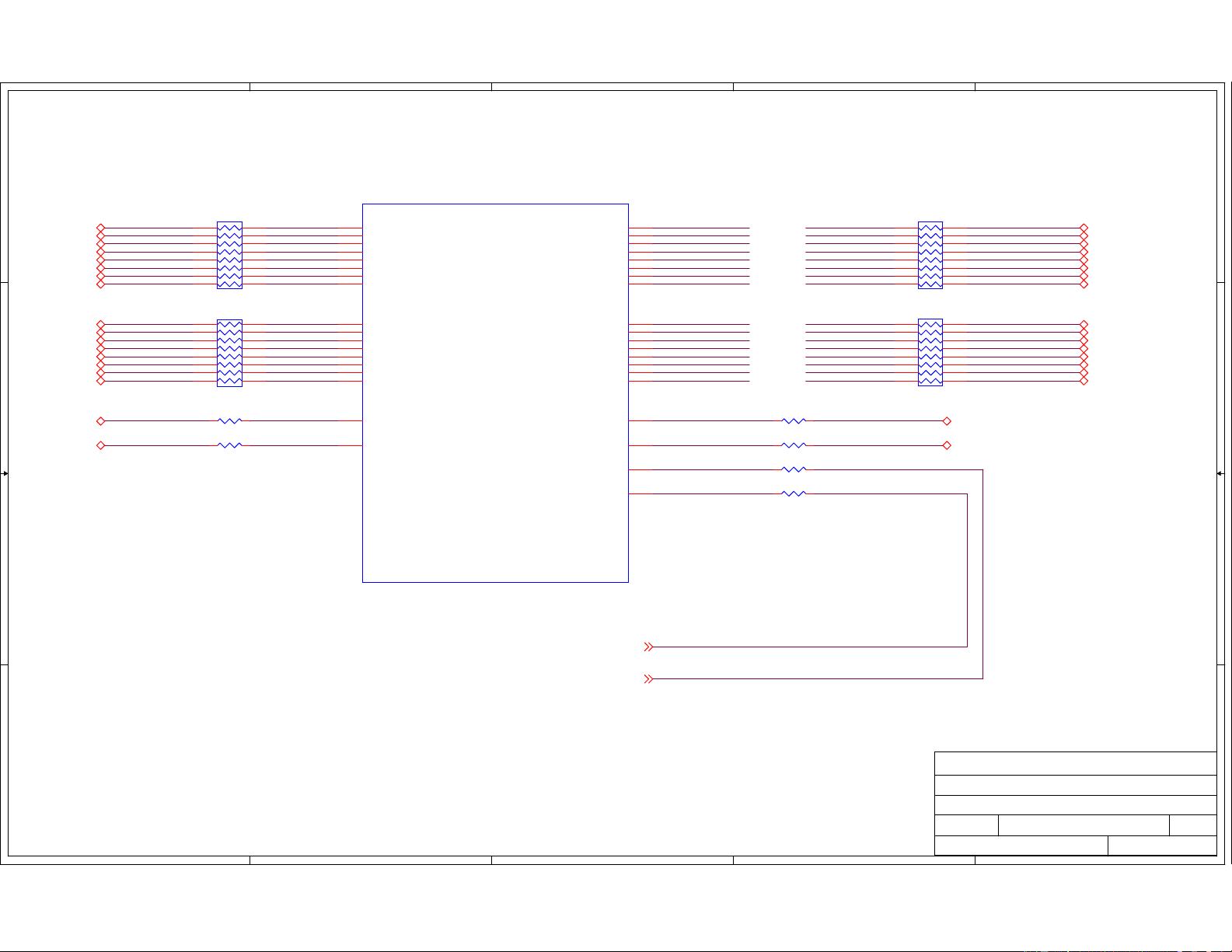

CPU_VPIF_CLKIN1VPIF_CLKIN1

CPU_VPIF_DIN15

CPU_VPIF_DIN13

CPU_VPIF_DIN14

CPU_VPIF_DIN12

CPU_VPIF_DIN9

CPU_VPIF_DIN10

CPU_VPIF_DIN8

CPU_VPIF_DIN11

CPU_VPIF_DIN6

CPU_VPIF_DIN4

CPU_VPIF_DIN7

CPU_VPIF_DIN5

CPU_VPIF_DIN2

CPU_VPIF_DIN3

VPIF_DIN15

VPIF_DIN14

CPU_VPIF_DIN1

CPU_VPIF_DIN0

VPIF_DIN13

VPIF_DIN12

VPIF_DIN11

VPIF_DIN10

VPIF_DIN9

VPIF_DIN8

VPIF_DIN7

VPIF_DIN6

VPIF_DIN5

VPIF_DIN4

VPIF_DIN3

VPIF_DIN2

VPIF_DIN1

VPIF_DIN0

CPU_VPIF_CLKIN0VPIF_CLKIN0

CPU_VPIF_DOUT0

CPU_VPIF_DOUT3

CPU_VPIF_DOUT5

CPU_VPIF_DOUT7

CPU_VPIF_DOUT8

CPU_VPIF_DOUT11

CPU_VPIF_DOUT13

CPU_VPIF_DOUT14

CPU_VPIF_DOUT15

VPIF_CLKIN2CPU_VPIF_CLKIN2

VPIF_CLKIN3CPU_VPIF_CLKIN3

VPIF_CLKOUT2

VPIF_CLKOUT3

VPIF_DOUT0

VPIF_DOUT1

VPIF_DOUT2

VPIF_DOUT7

VPIF_DOUT6

VPIF_DOUT3

VPIF_DOUT5

VPIF_DOUT15

VPIF_DOUT4

VPIF_DOUT12

VPIF_DOUT13

VPIF_DOUT10

VPIF_DOUT8

VPIF_DOUT11

VPIF_DOUT9

VPIF_DOUT14

CPU_VPIF_DOUT0

CPU_VPIF_DOUT1

CPU_VPIF_DOUT2

CPU_VPIF_DOUT3

CPU_VPIF_DOUT4

CPU_VPIF_DOUT5

CPU_VPIF_DOUT6

CPU_VPIF_DOUT7

CPU_VPIF_DOUT8

CPU_VPIF_DOUT9

CPU_VPIF_DOUT10

CPU_VPIF_DOUT11

CPU_VPIF_DOUT12

CPU_VPIF_DOUT13

CPU_VPIF_DOUT14

CPU_VPIF_DOUT15

CPU_VPIF_DOUT9

CPU_VPIF_CLKOUT2

CPU_VPIF_DOUT2

CPU_VPIF_DOUT1

CPU_VPIF_CLKOUT3

CPU_VPIF_DOUT6

CPU_VPIF_DOUT10

CPU_VPIF_DOUT12

CPU_VPIF_DOUT4

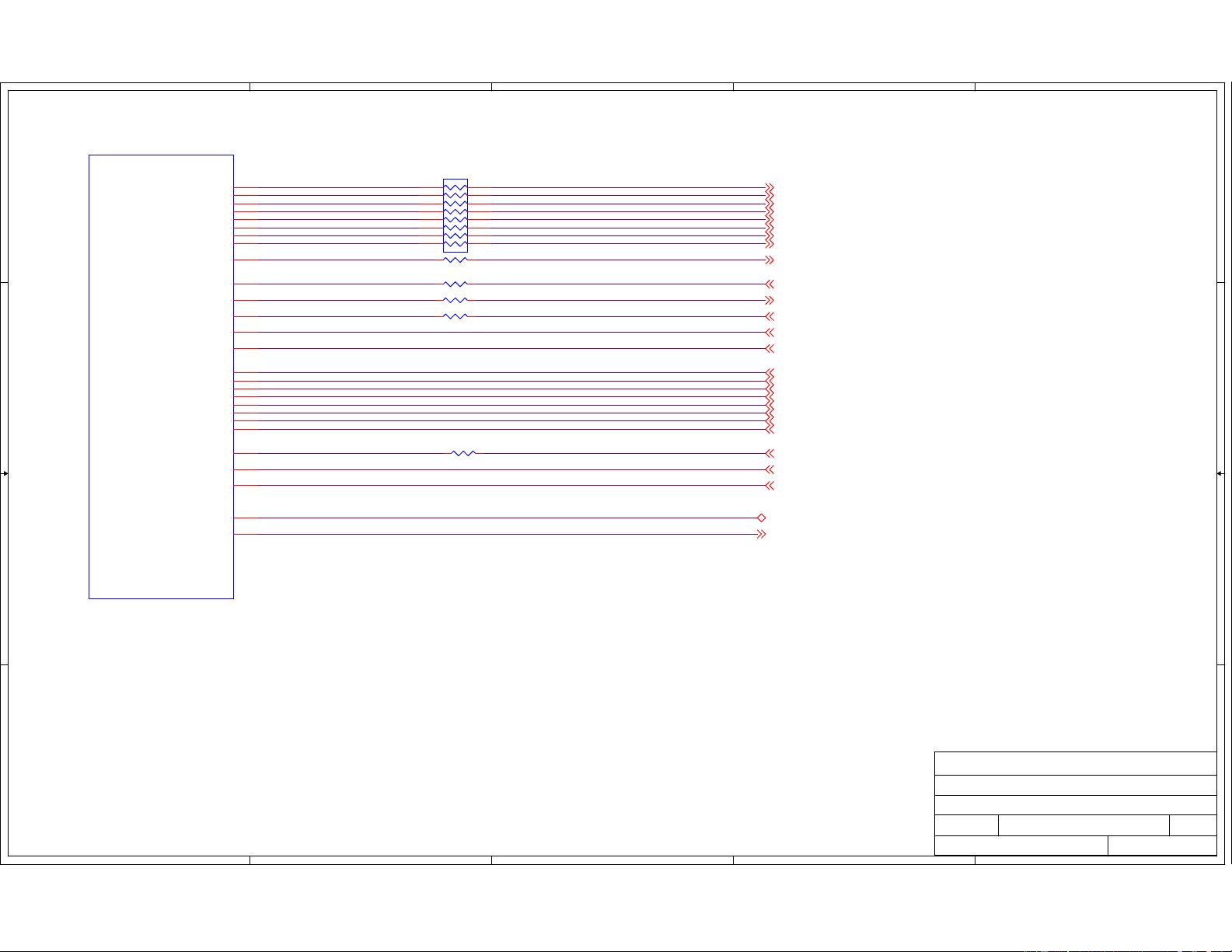

VPIF_DIN1031,39

VPIF_DIN1131,39

VPIF_DIN1231,39

VPIF_DIN1331,39

VPIF_DIN1431,39

VPIF_DIN1531,39

VPIF_CLKIN131,39

VPIF_CLKIN031,39

VPIF_DIN031,39

VPIF_DIN131,39

VPIF_DIN231,39

VPIF_DIN331,39

VPIF_DIN431,39

VPIF_DIN531,39

VPIF_DIN631,39

VPIF_DIN731,39

VPIF_DIN831,39

VPIF_DIN931,39

VPIF_CLKOUT2 35,39

VPIF_CLKOUT3 35,39

VPIF_CLKIN230,39

VPIF_CLKIN339

VPIF_DOUT0_BTM0 12,35,39

VPIF_DOUT1_BTM1 12,35,39

VPIF_DOUT2_BTM2 12,35,39

VPIF_DOUT3_BTM3 12,35,39

VPIF_DOUT4_CS2BW 12,35,39

VPIF_DOUT5_PCIEN 12,35,39

VPIF_DOUT6_DSPBT 12,35,39

VPIF_DOUT7_SMTRFEN 12,35,39

VPIF_DOUT8 35,39

VPIF_DOUT9 35,39

VPIF_DOUT10 35,39

VPIF_DOUT11 35,39

VPIF_DOUT12 35,39

VPIF_DOUT13 35,39

VPIF_DOUT14 35,39

VPIF_DOUT15 35,39

Size:

Date:

DWG NO

Revision:

Sheet of

Title:

Page Contents:

F

SPECTRUM DIGITAL INCORPORATED

509532-0001

Tuesday, June 24, 2008 8 43

B

DAVINCI HD Evaluation Module

DAVINCI HD VIDEO PORTS

R24 33

R28 0

RN23 RPACK8-33

1

2

3

4

5

6

7

89

10

11

12

13

14

15

16

RN22RPACK8-33

1

2

3

4

5

6

7

8 9

10

11

12

13

14

15

16

R30 33

R27 33R25 33

VIDEO IF

U29H DavinciHD

VP_DIN0/ST0_DOUT0

AC15

VP_DIN1/ST0_DOUT1

AB15

VP_DIN2/ST0_DOUT2

AA15

VP_DIN3/ST0_DOUT3

Y15

VP_DIN4/ST0_DOUT4/ST1_ERRIN

AC14

VP_DIN5/ST0_DOUT5/ST1_VALIN

AB14

VP_DIN6/ST0_DOUT6/ST1_PSTIN

AA14

VP_DOUT0/BTMODE0

AB5

VP_DOUT8/DT1_ERRO

AB9

VP_DOUT1/BTMODE1

AC4

VP_DOUT4/CS2BW

AA7

VP_DOUT2/BTMODE2

Y8

VP_DOUT7/VADJEN

AB7

VP_DOUT3/BTMODE3

AB6

VP_DOUT10/ST1_PSTO

AA10

VP_DOUT5/PCIEN

AC6

VP_DOUT6/DSPBOOT

AC5

VP_DOUT9/ST1_VALO

AC8

VP_DOUT11/ST1_DOUT

AB10

VP_DOUT12/ST1_ERRIN

AA8

VP_DOUT13/ST1_VALIN

Y9

VP_DOUT14/ST1_PSTIN

AC7

VP_DOUT15/ST1_DIN

AB8

VP_CLKIN2

Y10

VP_CLKO2

AA9

VP_DIN7/ST0_DOUT7/ST1_DIN

Y14

VP_DIN8/ST0_DIN0

AC16

VP_DIN9/ST0_DIN1

AB16

VP_DIN10/ST0_DIN2

AA16

VP_DIN11/ST0_DIN3

Y16

VP_DIN12/ST0_DIN4

AC17

VP_DIN13_FIELD/ST0_DIN5

AB17

VP_DIN14_HSYNC/ST0_DIN6

AA17

VP_DIN15_VSYNC/ST0_DIN7

AC18

VP_CLKIN1

AB18

VP_CLKIN0

AC13

VP_CLKIN3/ST1_CLKO

AC9

VP_CLKO3/ST0_CLKO

AC10

RN24 RPACK8-33

1

2

3

4

5

6

7

89

10

11

12

13

14

15

16

RN21RPACK8-33

1

2

3

4

5

6

7

8 9

10

11

12

13

14

15

16

R29 0