没有合适的资源?快使用搜索试试~ 我知道了~

首页Intel 845主板电路图.PDF

Intel 845主板电路图.PDF

需积分: 39 9 下载量 126 浏览量

更新于2023-05-16

评论

收藏 882KB PDF 举报

Intel 845主板电路图.PDF Intel 845主板电路图.PDF

资源详情

资源评论

资源推荐

Required BIOS Modifications

BIOS

Sequence

Go to

S1 Sleep

EXIT

Clear Ring Indicator

(Wake-Up Event)

Status Register

Intel

®

SpeedStep

®

Support ?

Ye s

No

Setup S1 State

Enable Ring Indicator

(Wake-Up Event)

Enable SLP in S1 State

of Power Management

Registers

Set ACPI Base Address

and

Enable ACPI I/O Region

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

To CPU pin AD25.

It has a pull-up resistor

to +3.3V_STBY

PLD

Spare Parts

FOR LM3

93

PLD DECOUP

LING

(1.5V Signal)

(3.3V Signal)

(3.3V Signal / 32KHz)

(5V Signal)

(3.3V Signal)

(1.5V Signal)

(3.3V Signal)

from ICH4

Higher Frequency Transition for Mobile Processor

+5V_STBY

+5V_STBY

+5V_STBY

+5V_STBY

+3.3V_STBY

+3.3V_STBY

C2

0.1uF

R8

33

R5

4K

U1

PLD

RESET

CPUSLP

CLK

DSLP

RI

VccGND

R1

10M

R3

10K

-

+

U2B

LM393

5

6

7

84

-

+

U2A

LM393

3

2

1

84

R2

3K

C4

0.1uF

R7

1K

R4

1.21K_1%

C5

30pF

+

C1

4.7uF/10V/20%

+

C3

4.7uF/10V/20%

R6

1.0K_1%

SUSCLK

DPSLP_OUT

+3.3V

H_SLP

ICH4_RI_PU

GHI

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

290KHz per Phase

Optional type-3 compensation

components, not needed for most cases

12V is the filtered input voltage for power

stage.

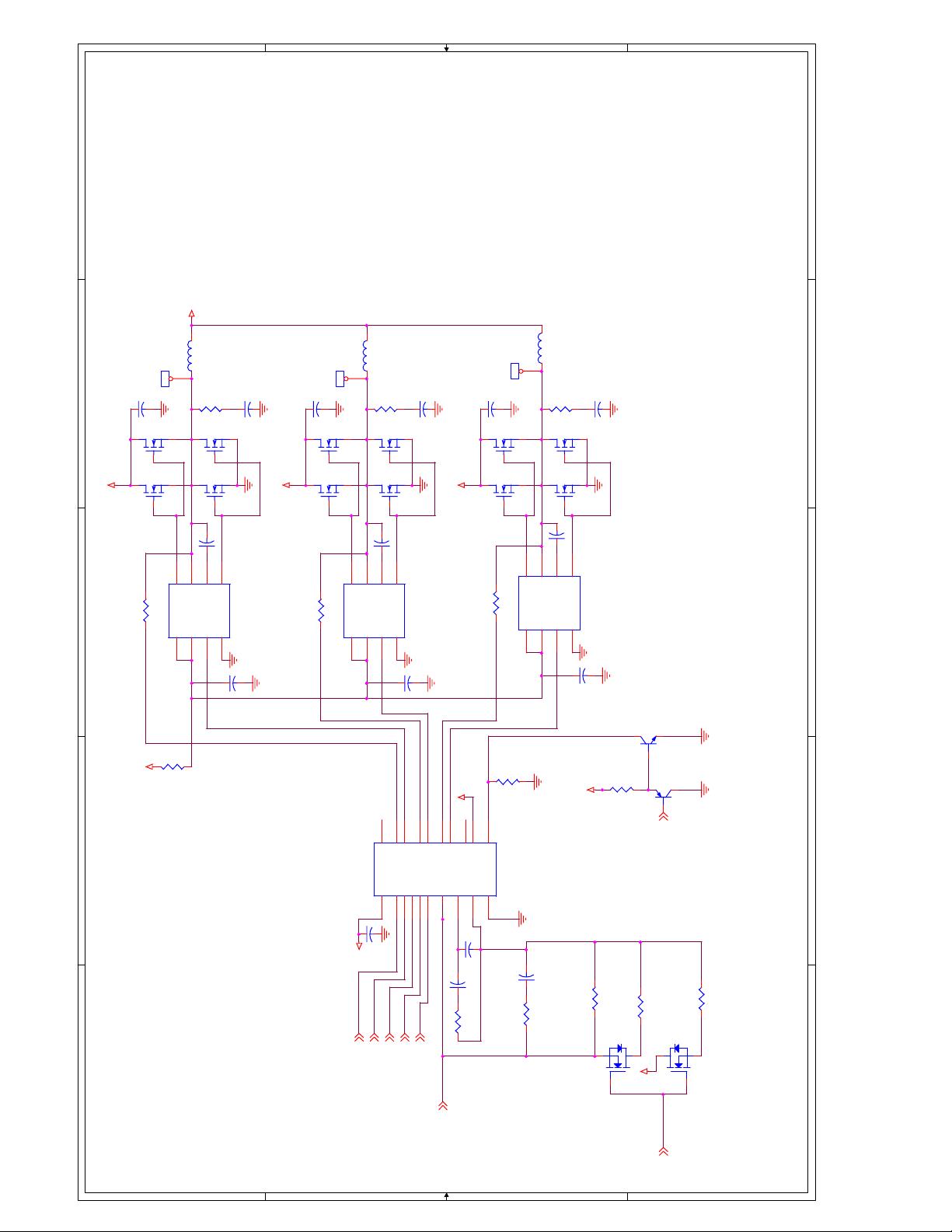

APPENDIX B

PWM Control and Power Stage

VID2

VR_Enable

VID3

VID0

V_CORE+2

VID4

VID1

Desktop_operation

2

V_CORE

+5V

VIN

+12V

+12V

+12V

+5V

+5V

+5V

Q12

1

3 4

U1 HIP6601

1

5

8

7

6

3 2

4

UGATE

LGATE

PHASE

PVCC

VCC

PWM BOOT

GND

L2

300nH

1 2

R11

1.62K

1 2

C23

4.7nF

12

L1

300nH

1 2

C21

4.7nF

12

R25

2.2ohm

C12

0.33uF

1 2

R21

2.2ohm

U2 HIP6601

1

5

8

7

6

3 2

4

UGATE

LGATE

PHASE

PVCC

VCC

PWM BOOT

GND

TP-1

1

C3 680pF

1 2

Q11

1

3 4

R0

100K

R_mobile 3.16k

1 2

Q34

1

3 4

C15

4.7uF

12

C1 1.2nF

1 2

C7

2.2uF

12

C16

0.33uF

1 2

C6

2.2uF

12

C2

56pF

C13

4.7uF

12

Q2

PNP BCE

C14

0.33uF

1 2

C8

2.2uF

12

R_desktop_offset 324k

1 2

R_desktop 6.19k

1 2

Q24

1

3 4

R10

10k

C25

4.7nF

12

U5

HIP6301V

20

1

2

3

4

5

15

14

11

18

16

13

12

17

7

6

10

9

19

8

VCC

VID4

VID3

VID2

VID1

VID0

PWM1

PWM2

PWM3

PWM4

ISEN1

ISEN2

ISEN3

ISEN4

FB

COMP

VSEN

GND

PGOOD

FS/DIS

Q32

1

3 4

Q14

1

3 4

TP-3

1

R13

1.62K

1 2

Q33

1

3 4

Q7

BSS138

3

1

2

Q21

1

3 4

Q13

1

3 4

Q7

BSS138

3

1

2

Q22

1

3 4

Rdriver-1

2.2ohm

R3 750ohm

1 2

TP-2

1

Q3

2N3772

R23

2.2ohm

R1 4.75K

1 2

C11

4.7uF

12

C0

1uF

L3

300nH

1 2

U3 HIP6601

1

5

8

7

6

3 2

4

UGATE

LGATE

PHASE

PVCC

VCC

PWM BOOT

GND

Q23

1

3 4

R12

1.65K

1 2

Q31

1

3 4

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

290KHz per Phase

Optional type-3 compensation

components, not needed for most cases

12V is the filtered input voltage for power

stage.

APPENDIX B

PWM Control and Power Stage

VID2

VR_Enable

VID3

VID0

V_CORE+2

VID4

VID1

Desktop_operation

2

V_CORE

+5V

VIN

+12V

+12V

+12V

+5V

+5V

+5V

Q12

1

3 4

U1 HIP6601

1

5

8

7

6

3 2

4

UGATE

LGATE

PHASE

PVCC

VCC

PWM BOOT

GND

L2

300nH

1 2

R11

1.62K

1 2

C23

4.7nF

12

L1

300nH

1 2

C21

4.7nF

12

R25

2.2ohm

C12

0.33uF

1 2

R21

2.2ohm

U2 HIP6601

1

5

8

7

6

3 2

4

UGATE

LGATE

PHASE

PVCC

VCC

PWM BOOT

GND

TP-1

1

C3 680pF

1 2

Q11

1

3 4

R0

100K

R_mobile 3.16k

1 2

Q34

1

3 4

C15

4.7uF

12

C1 1.2nF

1 2

C7

2.2uF

12

C16

0.33uF

1 2

C6

2.2uF

12

C2

56pF

C13

4.7uF

12

Q2

PNP BCE

C14

0.33uF

1 2

C8

2.2uF

12

R_desktop_offset 324k

1 2

R_desktop 6.19k

1 2

Q24

1

3 4

R10

10k

C25

4.7nF

12

U5

HIP6301V

20

1

2

3

4

5

15

14

11

18

16

13

12

17

7

6

10

9

19

8

VCC

VID4

VID3

VID2

VID1

VID0

PWM1

PWM2

PWM3

PWM4

ISEN1

ISEN2

ISEN3

ISEN4

FB

COMP

VSEN

GND

PGOOD

FS/DIS

Q32

1

3 4

Q14

1

3 4

TP-3

1

R13

1.62K

1 2

Q33

1

3 4

Q7

BSS138

3

1

2

Q21

1

3 4

Q13

1

3 4

Q7

BSS138

3

1

2

Q22

1

3 4

Rdriver-1

2.2ohm

R3 750ohm

1 2

TP-2

1

Q3

2N3772

R23

2.2ohm

R1 4.75K

1 2

C11

4.7uF

12

C0

1uF

L3

300nH

1 2

U3 HIP6601

1

5

8

7

6

3 2

4

UGATE

LGATE

PHASE

PVCC

VCC

PWM BOOT

GND

Q23

1

3 4

R12

1.65K

1 2

Q31

1

3 4

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

BGA385

16 MB int. mem.

Glue Logic

planar

5V PCI-Slot

Intel (R)

82801DB ICH4

I/O panel

max. 2 GB

planar

Pg. 8

Hub Interface 66MHz x4, 8b (266 MB/s)

SERIAL3

SMB

Intel(R) Pentium(R) 4

Processor or Intel(R)

Pentium(R) 4 Processor-M

I/O panel

Pg. 26, 27, 28

FWH

Pg. 12

PARALLEL

Intel (R) 82845E

LPC47N227

Intel (R) 82851 LAN

Controller

(optional

i82551/i82559)

I/O panel

PCI, 33MHz, 32b (132 MB/s)

SERIAL2

FIR

LPC47M107

planar

Intel (R) 82562ET/EM

Pg. 24, 25

I/O panel

8 Mbit

Intel (R)

82802AC

Firmware Hub

PLCC32

DDR-DIMM

LVDS

ATA66/100

planar

Pg. 13

CD-ROM

Pg. 19

1280x1024 @ 18Bit

RJ45

FCPGA478

PHOTO DIODE

planar

LAN

Pg. 25

USB2.0

BGA593

Pg. 31

AC'97

AD1885

Pg. 27

FAN

AGP 1.5V, 66MHz x4, 32b (1.1 GB/s)

PHY

Pg. 20

HEADPHONE

planar

Pg. 33

LINE-OUT

DVI/VGA

I/O panel

IDE1

SMI* SM731

CPU VRM

MOUSE

LM87

Pg. 33

Pg. 30

ITP

Pg. 31, 32

FDD

SYSMON

I/O panel

Pg. 9, 10, 11

IDE0

DVI-I

SERIAL0

USB

SIO

Pg. 23

ICS950201

CK 408B

I/O panel

FSB 133MHz x4, 64b (4.3 GB/s)

Pg. 6, 7

Block Diagram

planar

Pg. 29

Pg. 34

3 * planar

Pg. 15, 16, 17

I/O panel

LPC 3.3V, 33MHz

DDR SDRAM 2.5V, 266MHz, 64b (2.1 GB/s)

Pg. 35

SIO

BGA421

MICRO

- Postcode decoding

- Speedstep logic

- Powerup sequencing

SERIAL1

Clocking

miniPCI-Slot

LINE-IN

planar

I/O panel

Pg. 18

AC'97

I/O panel

DDR VR

TV-OUT

RJ45

K/B

Xilinx *

Coolrunner

Pg. 29

2 * I/O panel

2 * I/O panel, powered

2 * planar

Pg. 14

Pg. 27

Pg. 27

Pg. 31

Pg. 30

Pg. 30

Pg. 21

Pg. 21

Pg. 21

Pg. 22

Pg. 22

Pg. 22

Pg. 22

Pg. 20

Platform LAN Connect

Component

MCH

BLOCK-DIAGRAM

剩余37页未读,继续阅读

drjiachen

- 粉丝: 169

- 资源: 2144

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- zigbee-cluster-library-specification

- JSBSim Reference Manual

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0