没有合适的资源?快使用搜索试试~ 我知道了~

首页RTC-PCF8563TS 实时时钟.pdf

RTC-PCF8563TS 实时时钟.pdf

需积分: 50 15 下载量 115 浏览量

更新于2023-05-18

评论

收藏 492KB PDF 举报

The PCF8563 is a CMOS1 Real-Time Clock (RTC) and calendar optimized for low power consumption. A programmable clock output, interrupt output, and voltage-low detector are also provided. All addresses and data are transferred serially via a two-line bidirectional I2C-bus. Maximum bus speed is 400 kbit/s. The register address is incremented automatically after each written or read data byte.

资源详情

资源评论

资源推荐

1. General description

The PCF8563 is a CMOS

1

Real-Time Clock (RTC) and calendar optimized for low power

consumption. A programmable clock output, interrupt output, and voltage-low detector are

also provided. All addresses and data are transferred serially via a two-line bidirectional

I

2

C-bus. Maximum bus speed is 400 kbit/s. The register address is incremented

automatically after each written or read data byte.

2. Features and benefits

Provides year, month, day, weekday, hours, minutes, and seconds based on a

32.768 kHz quartz crystal

Century flag

Clock operating voltage: 1.0 V to 5.5 V at room temperature

Low backup current; typical 0.25 Aat V

DD

= 3.0 V and T

amb

=25C

400 kHz two-wire I

2

C-bus interface (at V

DD

= 1.8 V to 5.5 V)

Programmable clock output for peripheral devices (32.768 kHz, 1.024 kHz, 32 Hz, and

1Hz)

Alarm and timer functions

Integrated oscillator capacitor

Internal Power-On Reset (POR)

I

2

C-bus slave address: read A3h and write A2h

Open-drain interrupt pin

3. Applications

Mobile telephones

Portable instruments

Electronic metering

Battery powered products

PCF8563

Real-time clock/calendar

Rev. 10 — 3 April 2012 Product data sheet

1. The definition of the abbreviations and acronyms used in this data sheet can be found in Section 18.

PCF8563 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 10 — 3 April 2012 2 of 50

NXP Semiconductors

PCF8563

Real-time clock/calendar

4. Ordering information

[1] Not to be used for new designs. Replacement part is PCF8563T/5.

[2] Not to be used for new designs. Replacement part is PCF8563TS/5.

5. Marking

Table 1. Ordering information

Type number Package

Name Description Version

PCF8563BS/4 HVSON10 plastic thermal enhanced very thin small outline

package; no leads; 10 terminals;

body 3 3 0.85 mm

SOT650-1

PCF8563P/F4 DIP8 plastic dual in-line package; 8 leads (300 mil) SOT97-1

PCF8563T/5 SO8 plastic small outline package; 8 leads;

body width 3.9 mm

SOT96-1

PCF8563T/F4

[1]

SO8 plastic small outline package; 8 leads;

body width 3.9 mm

SOT96-1

PCF8563TS/4

[2]

TSSOP8 plastic thin shrink small outline package; 8 leads;

body width 3 mm

SOT505-1

PCF8563TS/5 TSSOP8 plastic thin shrink small outline package; 8 leads;

body width 3 mm

SOT505-1

Table 2. Marking codes

Type number Marking code

PCF8563BS/4 8563S

PCF8563P/F4 PCF8563P

PCF8563T/5 PCF8563

PCF8563T/F4 8563T

PCF8563TS/4 8563

PCF8563TS/5 P8563

PCF8563 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 10 — 3 April 2012 3 of 50

NXP Semiconductors

PCF8563

Real-time clock/calendar

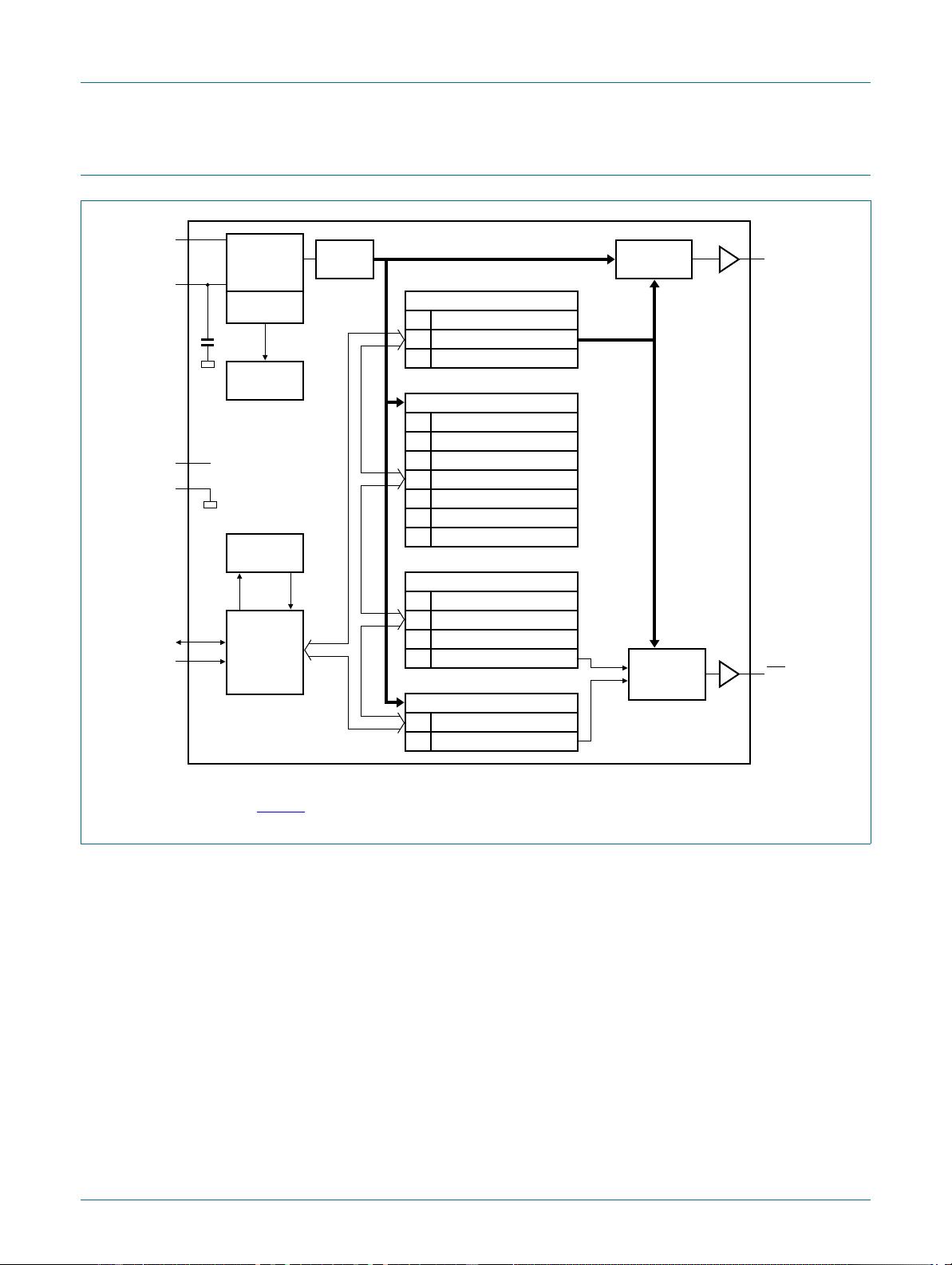

6. Block diagram

(1) C

OSCO

; values see Ta ble 3 0.

Fig 1. Block diagram of PCF8563

001aah658

PCF8563

OSCILLATOR

32.768 kHz

DIVIDER CLOCK OUT

INTERRUPT

CLKOUT

INT

MONITOR

POWER ON

RESET

WATCH

DOG

I

2

C-BUS

INTERFACE

OSCI

SCL

SDA

OSCO

V

DD

V

SS

TIMER FUNCTION

TIMER_CONTROL0E

TIMER0F

CONTROL

CONTROL_STATUS_100

CONTROL_STATUS_201

CLKOUT_CONTROL0D

TIME

VL_SECONDS02

MINUTES03

HOURS04

DAYS05

ALARM FUNCTION

MINUTE_ALARM09

HOUR_ALARM0A

DAY_ALARM0B

WEEKDAY_ALARM0C

WEEKDAYS06

CENTURY_MONTHS07

YEARS08

(1)

PCF8563 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 10 — 3 April 2012 4 of 50

NXP Semiconductors

PCF8563

Real-time clock/calendar

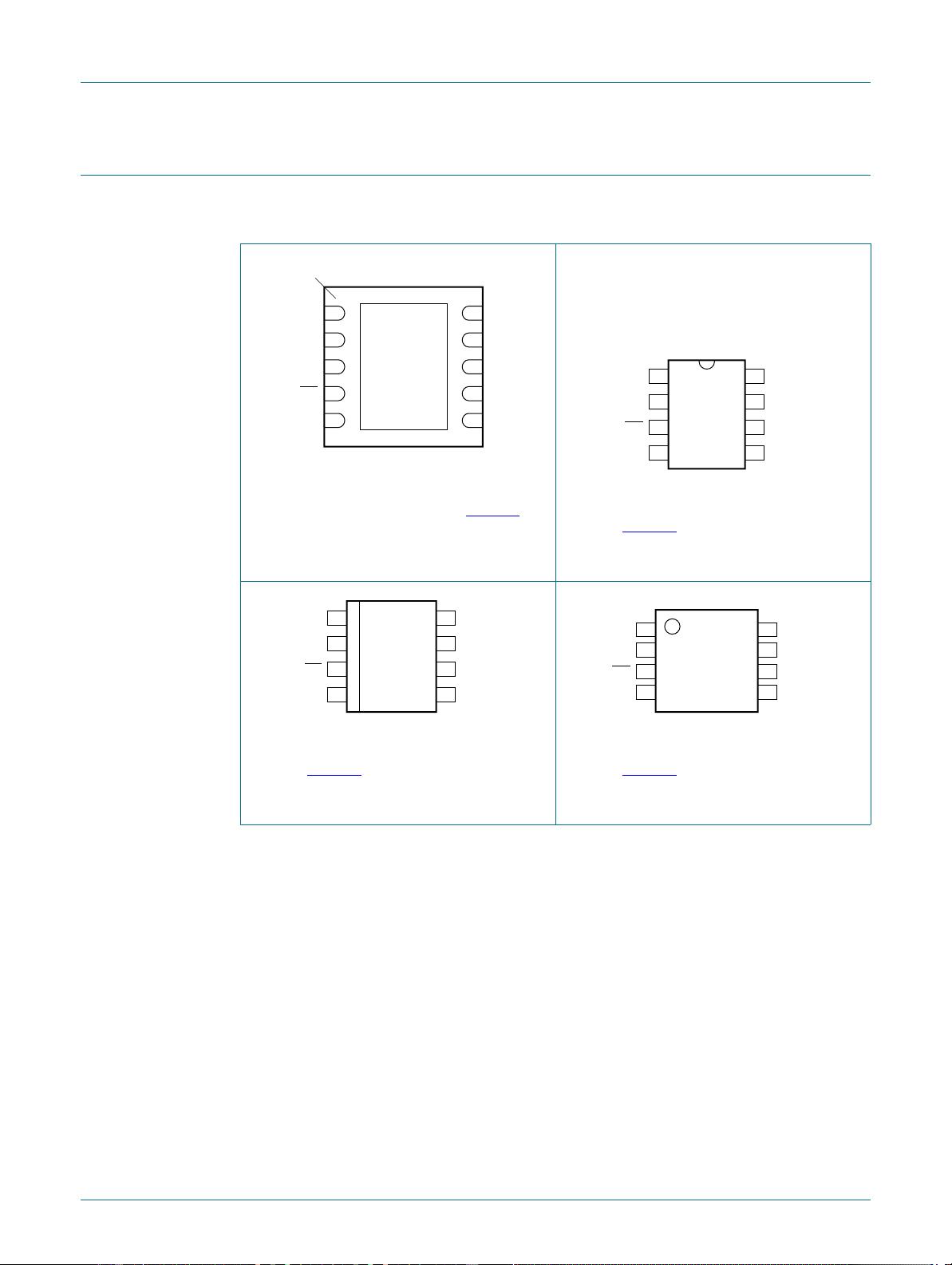

7. Pinning information

7.1 Pinning

For mechanical details, see Figure 30. Top view. For mechanical details, see

Figure 31

.

Fig 2. Pin configuration for HVSON10

(PCF8563BS)

Fig 3. Pin configuration for DIP8

(PCF8563P)

Top view. For mechanical details, see

Figure 32

.

Top view. For mechanical details, see

Figure 33.

Fig 4. Pin configuration for SO8

(PCF8563T)

Fig 5. Pin configuration for TSSOP8

(PCF8563TS)

001aaf981

PCF8563BS

SDA

INT

V

SS

SCL

n.c. CLKOUT

OSCO V

DD

OSCI n.c.

Transparent top view

5

6

4 7

3 8

2 9

1 10

terminal 1

index area

PCF8563P

OSCI

V

DD

OSCO

CLKOUT

INT

SCL

V

SS

SDA

001aaf977

1

2

3

4

6

5

8

7

PCF8563T

OSCI V

DD

OSCO CLKOUT

INT

SCL

V

SS

SDA

001aaf975

1

2

3

4

6

5

8

7

PCF8563TS

OSCI V

DD

OSCO CLKOUT

INT SCL

V

SS

SDA

001aaf976

1

2

3

4

6

5

8

7

PCF8563 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 10 — 3 April 2012 5 of 50

NXP Semiconductors

PCF8563

Real-time clock/calendar

7.2 Pin description

[1] The die paddle (exposed pad) is wired to V

SS

but should not be electrically connected.

Table 3. Pin description

Symbol Pin Description

DIP8, SO8, TSSOP8 HVSON10

OSCI 1 1 oscillator input

OSCO 2 2 oscillator output

INT

3 4 interrupt output (open-drain; active LOW)

V

SS

45

[1]

ground

SDA 5 6 serial data input and output

SCL 6 7 serial clock input

CLKOUT 7 8 clock output, open-drain

V

DD

8 9 supply voltage

n.c. - 3, 10 not connected; do not connect and do not

use as feed through

剩余49页未读,继续阅读

barehua82

- 粉丝: 0

- 资源: 6

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- zigbee-cluster-library-specification

- JSBSim Reference Manual

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0