Verilog设计数字系统入门指南

需积分: 50 137 浏览量

更新于2023-05-20

1

收藏 16.65MB PDF 举报

《数字系统设计使用Verilog》是一本由Charles H. Roth Jr., Lizy Kurian John, 和 ByeongKil Lee合著的优秀教材,专为学习和理解数字系统设计中的Verilog编程语言而编撰。该书针对初学者和进阶工程师,旨在通过深入浅出的方式介绍逻辑设计基础知识,并将这些理论与实际应用中的Verilog编程相结合。

本书的第一章回顾了逻辑设计的基本概念,包括:

1. **组合逻辑**:这部分介绍了基本的逻辑门结构和逻辑函数,帮助读者理解电路如何根据输入信号实时计算输出。

2. **布尔代数与代数简化**:作者详细解释了布尔运算规则,以及如何利用代数方法简化复杂的逻辑表达式,以提高电路效率和设计简洁性。

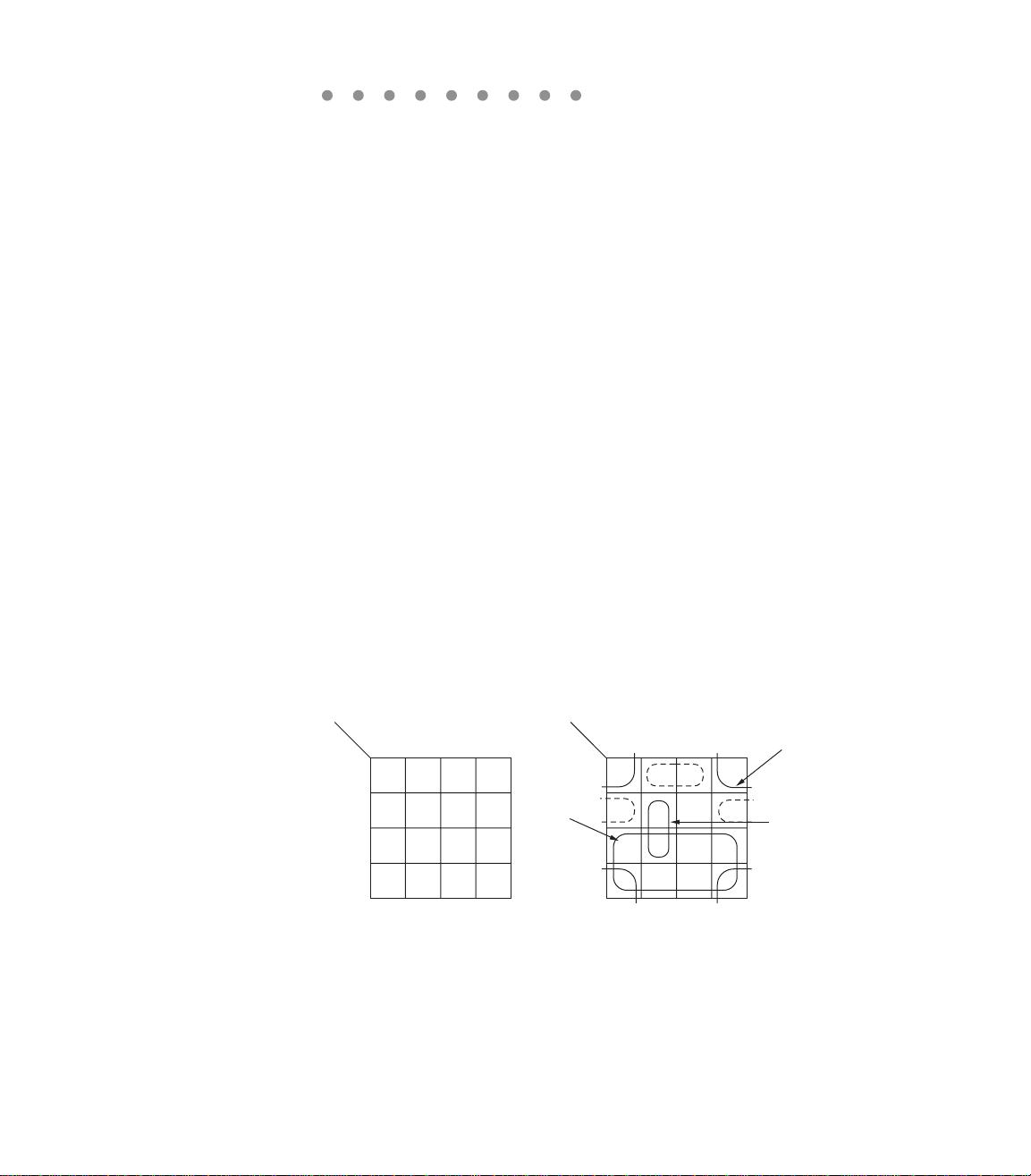

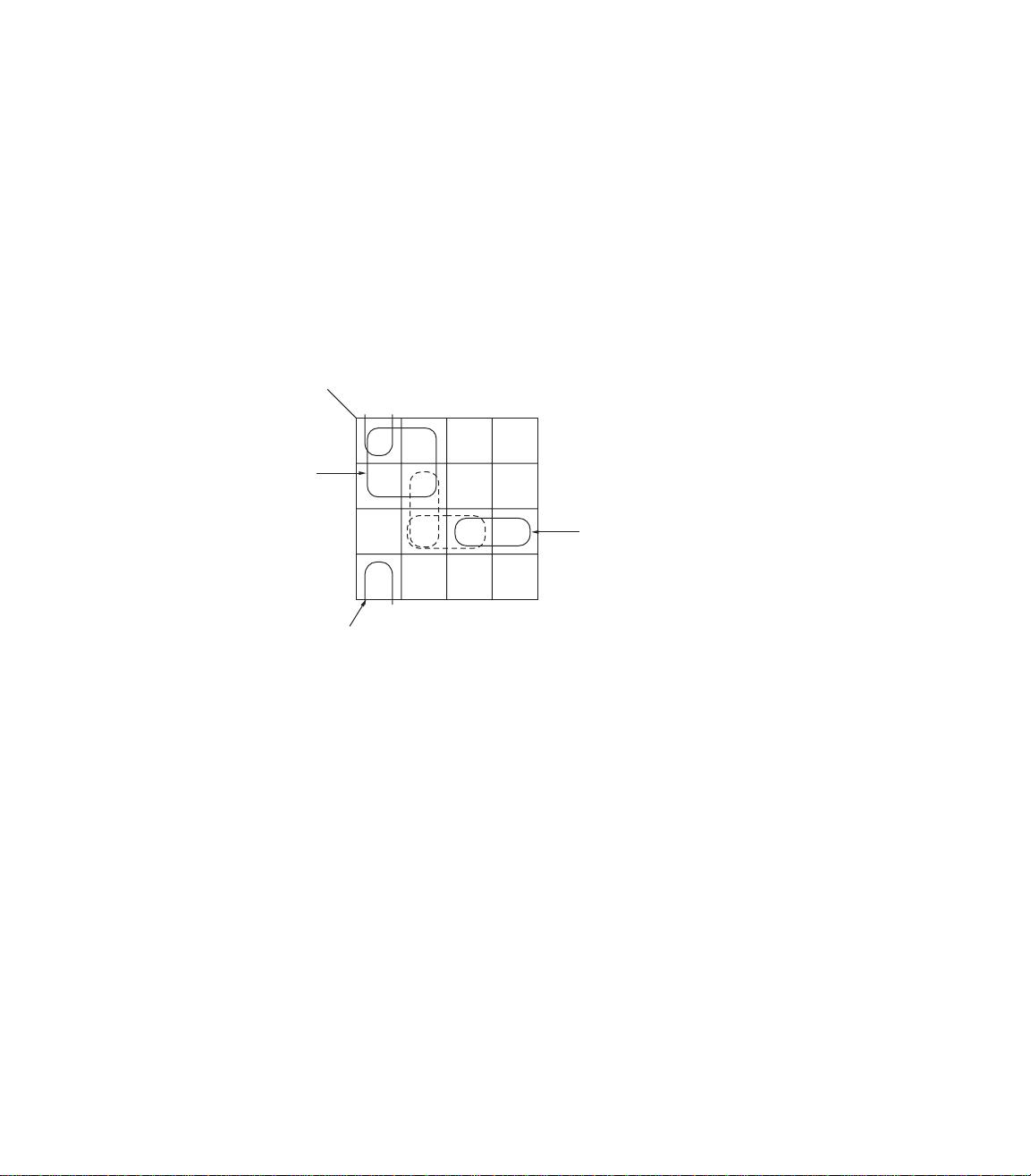

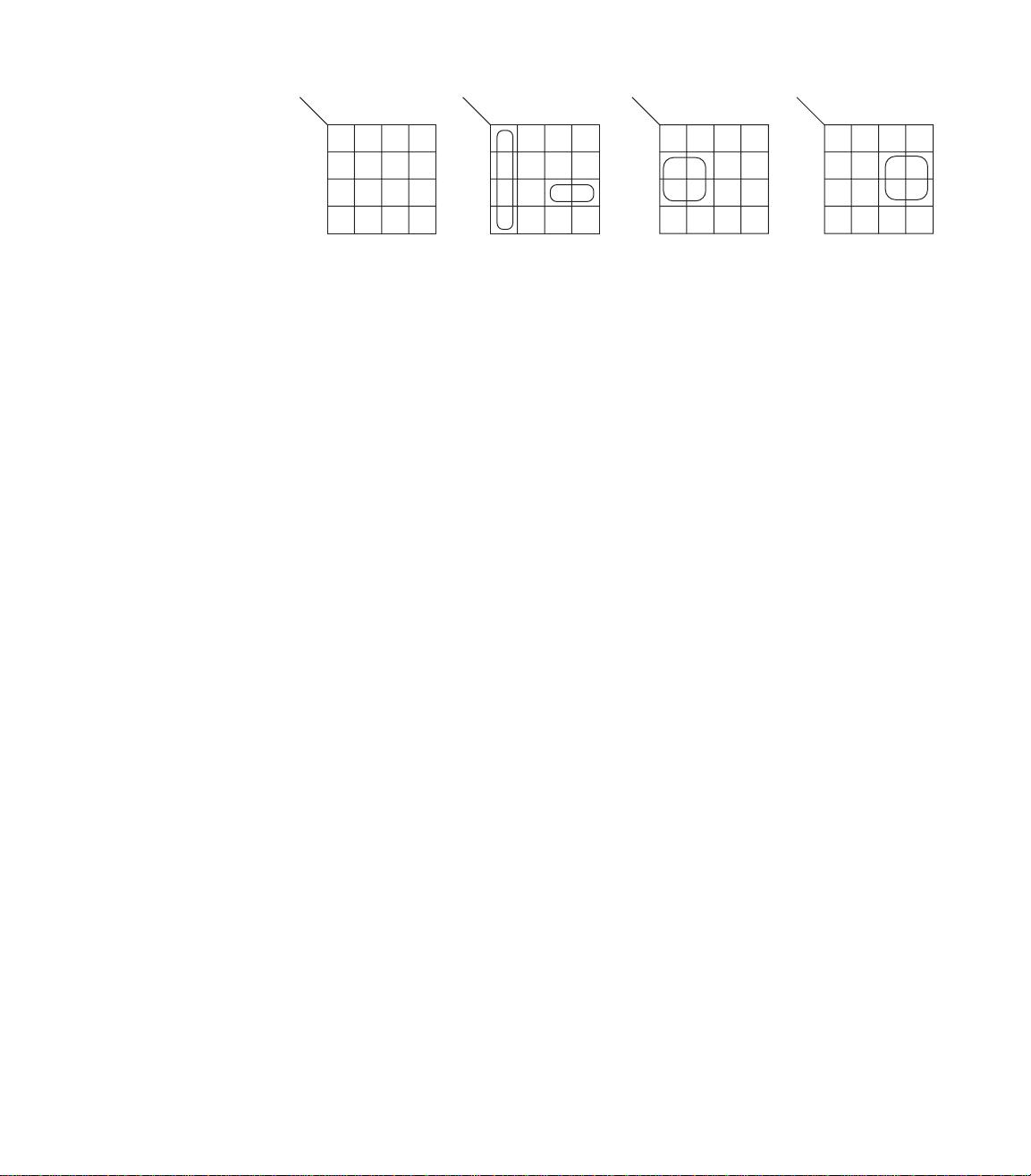

3. **卡诺图(Karnaugh Maps)**:卡诺图是一种可视化工具,用于查找最小项表达式和进行逻辑优化,这对于理解和设计高效电路至关重要。

4. **使用NAND和NOR门的设计**:作者引导读者通过这两种基础门来构建更复杂的逻辑电路,从而掌握基本设计原则。

5. **组合电路中的冲突(Hazards)**:探讨了在时序逻辑中可能出现的同步和异步冒险现象,这对于理解和避免潜在问题非常重要。

6. **触发器与寄存器(Flip-Flops and Latches)**:这一部分深入解释了时序逻辑元件,如D型、JK型和T型触发器,以及它们在存储和传递状态中的作用。

7. **梅耶(Mealy)序列电路设计**:介绍了基于事件驱动的序列电路设计,强调了输入和输出之间的时序关系。

8. **摩尔(Moore)序列电路设计**:讲解了另一种常用的序列电路设计范式,其中输出只依赖于当前状态,而不考虑输入。

9. **等效状态和状态表简化**:探讨了如何分析和简化状态机,以减少设计复杂性和实现精简。

10. **Verilog编程基础**:在理论讲解之后,作者逐步引入Verilog语言,让读者能在实践中应用所学的逻辑设计原理。

整本书通过理论教学和实例演示,为读者提供了一个系统的学习框架,不仅适用于理论学习,也是数字系统设计师必备的实用参考书。对于想要进一步探索数字系统设计和Verilog编程的人来说,这是一本不可多得的指南。

264 浏览量

113 浏览量

176 浏览量

274 浏览量

168 浏览量

372 浏览量

集成电路设计那些事儿

- 粉丝: 912

最新资源

- 英数图像识别库:验证码的通用处理技术

- 全面技术项目源码合集:商业名片设计与整站开发教程

- Android万能下载器:在线下载任意格式文件

- ACAD2008 Express汉化补丁使用指南

- C语言核心概念:指针、活动记录与内存管理

- webCAMotion:网络摄像头模拟鼠标的开源程序

- Axure高效设计模板:导航条与版权页母版

- C语言实现最小生成树算法及路径自动生成

- SPM8数据预处理及分析批处理工具

- 绿色大气个人摄影相册网站模板及全技术领域源码分享

- Android全屏注册界面的设计与实现技巧

- 易通远程屏幕监控系统安装与卸载详细指南

- Ehcache复制机制详解与集群环境演示教程

- Facebook Messenger终端控制:全新Python自动化脚本

- MATLAB动态规划程序包:优化算法实践

- Android ADT-22.0.5版本发布,探索新特性