没有合适的资源?快使用搜索试试~ 我知道了~

首页IT6604_IT6605寄存器

资源详情

资源评论

资源推荐

ITE Confidential

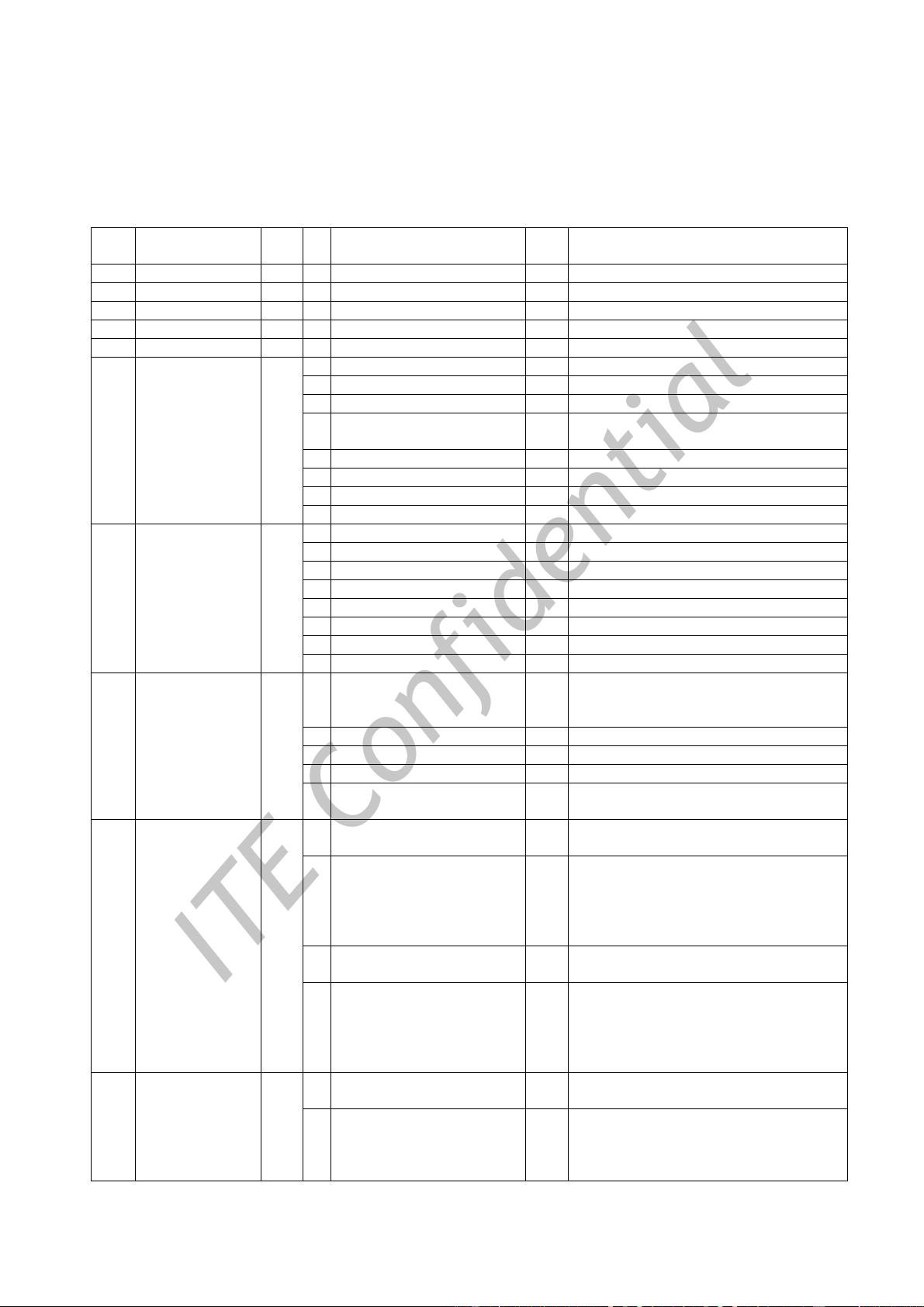

IT6604/IT6605 Register Table V1.03

Term:

RO: Read Only

W/R: Read/Write

Reg

Offset

Reg_Name W/R

Bits

Status Defau

lt

Description

0x00 VID_L RO 7:0 0x00

0x01 Backup_reg2 WR 7:0 Reserved 0x00

0x02 DEVID_L RO 7:0 0x23 Device ID (Low word)

0x03 DEVID_H RO 7:0 0x60 Device ID (High word)

0x04 DevRev RO 7:0 0xa3 Device Revision Number

7 REG_CDR_RST 0 1: reset CDR.

6 Reserved 0

5 REG_AUTO_CDR_RST 0 1: Auto reset CDR

4 REGRST 0 1: Software reset the clock domain include

control registers to default

3 Reserved(not used) 0

2 AUDRST 0 1: Software reset audio logic

1 VDORST 0 1: Software reset video logic

0x05 Rst_Ctrl W/R

0 SWRST 0 1: Software reset all logic

7 PWD_Ch2 0 1: Power down channel2

6 PWD_Ch1 0 1: Power down channel1

5 PWD_Ch0 0 1: Power down channel0

4 PWD_ACLK 0 1: Power down Audio clock domain

3 PWD_PCLK 0 1: Power down Pixel clock domain

2 PWD_APLL 0 1: Power down Audio PLL

1 PWD_RXPLL 0 1: Power down Pixel PLL

0x06 Pwd_Ctrl0 W/R

0 PWD_ALL 0 1: Power down all AFEs and Logic blocks

4 Sel_port 0 Select active port:

0: portA

1: portB (IT6605 only)

3 PWD_AFEall 0 1: Power down all AFEs

2 PWDC_ETC 0 1: Power down certain AFE blocks

1 PWDC_SRV 0 1: Power down AFE equalizer

0x07 Pwd_Ctrl1 W/R

0 EN_AutoPWD 0 1: Auto Power down whole chip when no

clock is detected

7 VIO_Slew

1

Video data Slew rate

Slew rate: 0:Fast ; 1:Slow

6:4 VIO_ST

001

VDATA Driving Strength

000:2mA ; 001:4mA;

010:6mA ; 011:8mA;

100:10mA;101:12mA;

110:14mA;111:16mA;

3 Vclk_Slew

1

VCLK Slew rate

Slew rate: 0:Fast ; 1:Slow

0x08 VIO_Ctrl W/R

2:0 Vclk_ST

011

VCLK Driving Strength

000:2mA ; 001:4mA;

010:6mA ; 011:8mA;

100:10mA;101:12mA;

110:14mA;111:16mA;

7 AIO_Slew 1 Audio data Slew rate

Slew rate: 0:Fast ; 1:Slow

0x09 AIO_Ctrl W/R

6:4 AIO_ST 001

Audio data Driving Strength

000:2mA ; 001:4mA;

010:6mA ; 011:8mA;

100:10mA;101:12mA;

ITE Confidential

110:14mA;111:16mA;

3 Mclk_Slew 1 Audio clock Slew rate

Slew rate: 0:Fast ; 1:Slow

2:0 Mclk_ST 001 Audio Driving Strength

000:2mA ; 001:4mA;

010:6mA ; 011:8mA;

100:10mA;101:12mA;

110:14mA;111:16mA;

0x0A Reserved W/R 0x2A

0x0B Reserved W/R 0xA5

0x0C BIST_Ctrl W/R 0 ARAM_BIST_EN 0 Internal Audio FIFO BIST test circuits

0x0D BIST_Result1 RO 7

6:0

ARAM_bo_faultHQ

ARAM_D6FaulStauHQ

Audio FIFO BIST status

0x0E Reserved

0x0F Block_Sel W/R 0 Block_ID 0

Register block select

0: block 0 is select for Reading and writing

1: block 1 is select for Reading and writing

7 RXPLL_LOCK x 1: RX PLL is lock

6 RXCK_Speed x 1: RX clock is lower than 80Mhz

5 RXCK_VALID x 1: Clock is valid

4 HDMI_MODE x 1: HDMI mode or DVI mode (value:0)

3 P1_PWR5V_DET x 1: Port-1 5V is detect

2 SCDT x 1: Video Sync is stable

1 VCLK_DET x 1: Video clock is detect

0x10 Sys_state RO

0 PWR5V_DET x 1: Port-0 5V is detect

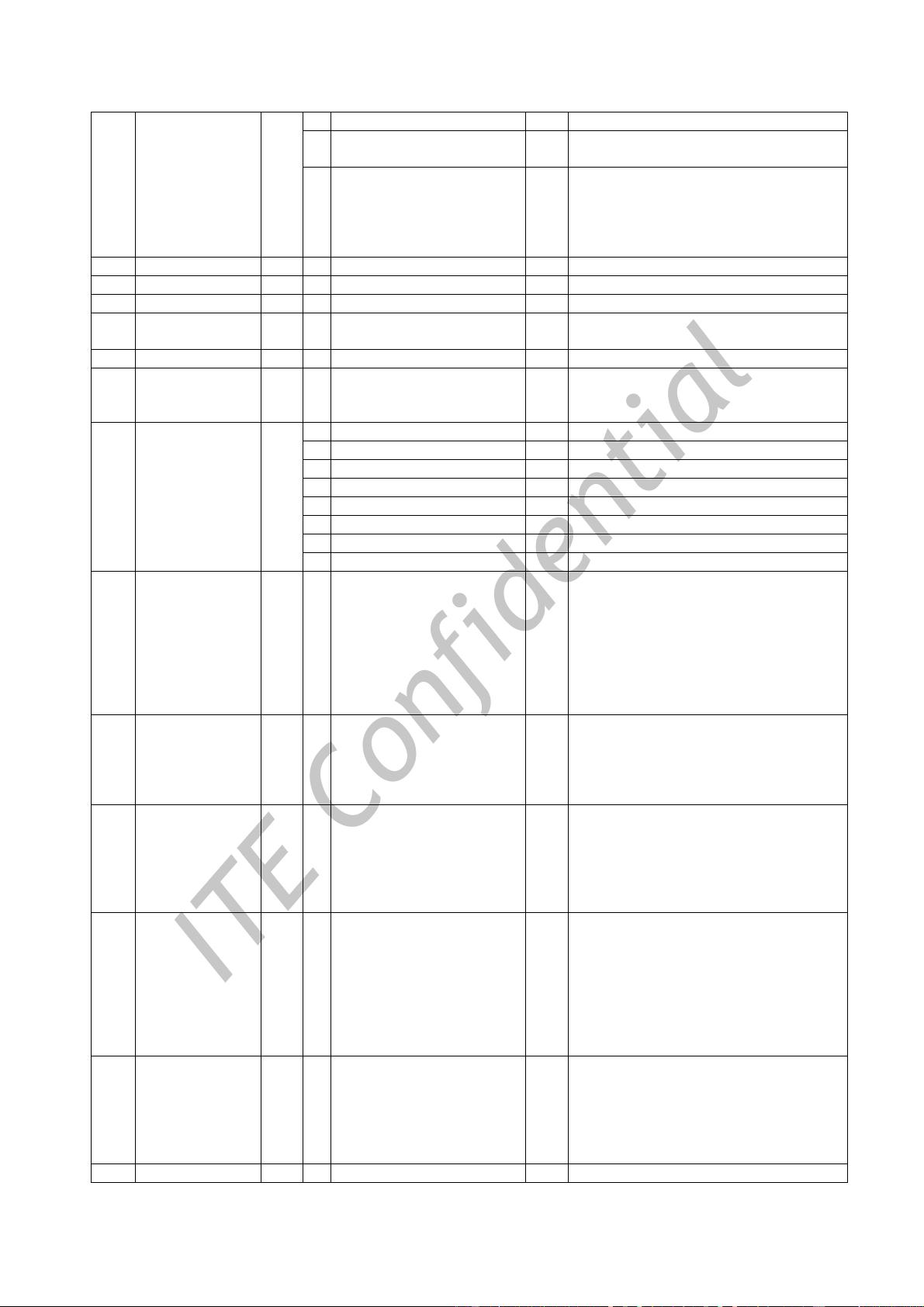

0x11 HDCP_Ctrl W/R 7

6

5

4

3

2

1

0

ExtROM

reserved

reserved

reserved

HDCP_RomDisWr

HDCP_A0

reserved

HDCP_en

0x89 1: select internal OTP as HDCP key ROM

1: Disable external ROM write function

1: Select 0x76 as DDC address.(default is

0x74)

1: Enable HDCP

0x12 HDCP_Status RO 7-4

3

2

1

0

reserved

HDCP_ADVCipher

HDCP_EESS

HDCP_KeyRd_Fail_Flag

Hdcp_on_Flag

Show the HDCP authentication stauts

0x13 Interrupt0 RO 5

4

3

2

1

0

VidMode_Chg

HDMIMode_Chg

SCDTOFF

SCDTON

Pwr5VOff

Pwr5Von

‘1’: Video mode change

‘1’: HDMI/DVI mode swap change

‘1’: Video stable is off

‘1’: Video stable is on

‘1’: Selected port 5V is off

‘1’: Selected port 5V is on

0x14 Interrupt1 RO 7

6

5

4

3

2

1

0

PktLeftMute

NewAudioPkt_Det

NewACPPkt_Det

NewSPDPkt_Det

NewMPEGPkt_Det

NewAVIPkt_Det

NoAVI_Rcv

PktSetMute

‘1’: Left Mute Packet is received

‘1’: New Audio Packet detect

‘1’: New ACP Packet detect

‘1’: New SPD Packet detect

‘1’: New MPEG Packet detect

‘1’: New AVI Packet detect

‘1’: No AVI Packet is received

‘1’: Set Mute Packet is received

0x15 Interrupt2 RO 5

4

3

2

1

0

ROMFault

AutoAudMute

AudFIFOErr

ECCERR

Auth_done

Auth_start

‘1’: ROM access Fault Flag

‘1’: Audio Auto Mute Flag

‘1’: Audio FIFO error Flag

‘1’: EDD error Flag

‘1’: Authentication Done Flag

‘1’: Authentication Start Flag

0x16 Interrupt_MASK0 W/R 5:0 0x3F Mask of interrupts defined in reg0x13

ITE Confidential

1: The Interrupt is effective

0: The Interrupt is ineffective

0x17 Interrupt_MASK1 W/R 7:0 0x00 Mask of interrupts defined in reg0x14

1: The Interrupt is effective

0: The Interrupt is ineffective

0x18 Interrupt_MASK2 W/R 7 Clr_HDCP_int 0 1:Clear interrupts generated by HDCP

authenticate start and done

5:0

0x00 Mask of interrupts defined in reg0x15

1: The Interrupt is effective

0: The Interrupt is ineffective

1:Clear interrupts generated by HDCP

signals

7 Clr_SetMute_int 0 1:Clear interrupts generated by set mute

packet

6 Clr_LeftMute_int 0 1:Clear interrupts generated by left mute

packet

5 IntrOutType 1 Interrupt pin output type

1:open drain

0:push pull

4 IntPol 1 Interrupt pin output polarity

1:low active

0:high active

3 Clr_Audio_int 0 1:Clear interrupts generated by Audio FIFO

error

2 Clr_ECC_int 0 1:Clear interrupts generated by ECC error

1 Clr_Pkt_int 0 1:Clear interrupts generated by Packet

signals

0x19 Interrupt_ctr W/R

0 Clr_Mode_int 0 1:Clear interrupts generated by mode

change

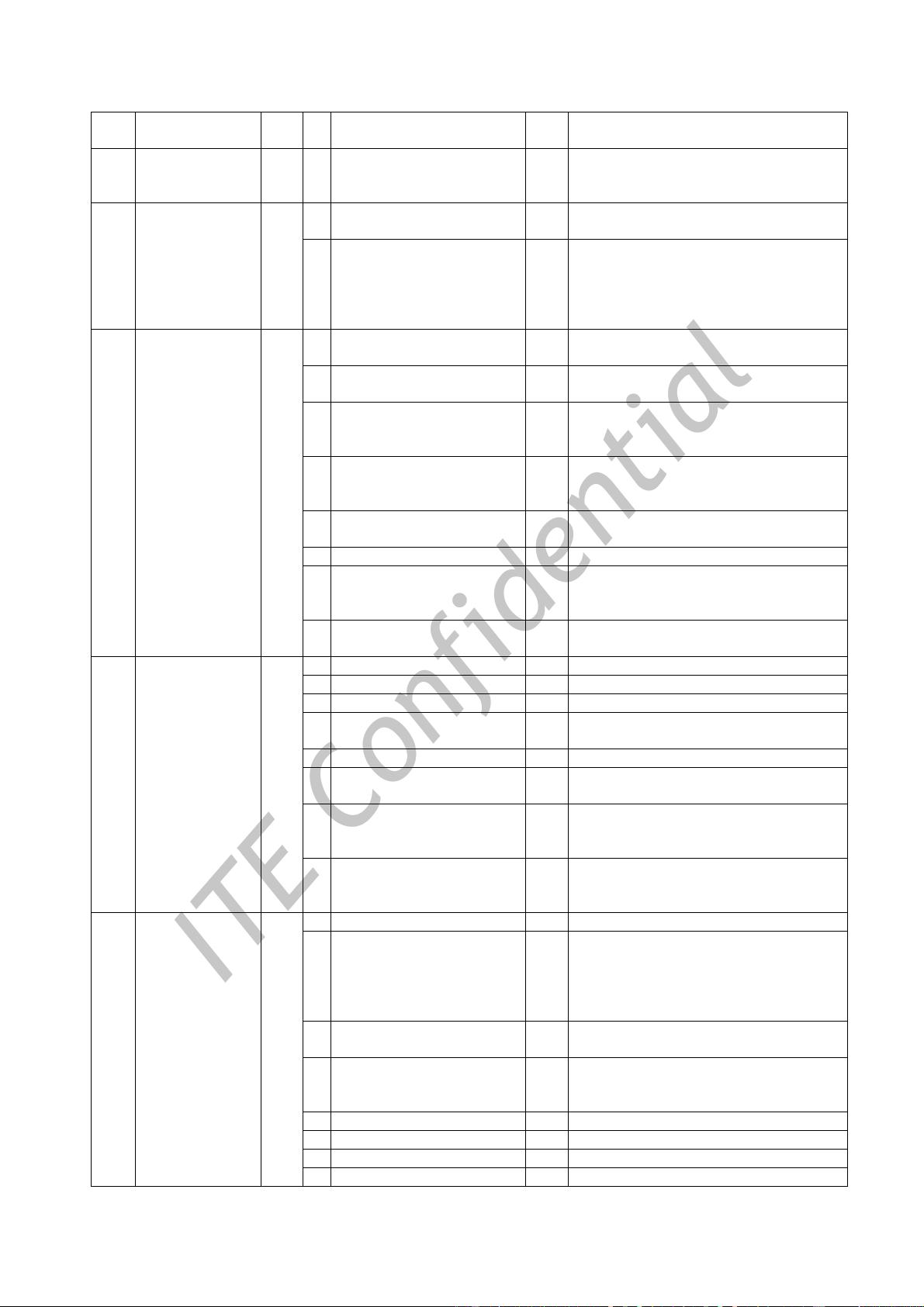

7 reserved 0

6 reserved 0

5 reserved 0

4 Timeout_en

1 1:auto timeout when no DE detected

3 reserved 0

2 SelDebugHL

1 1:For Debug signals selecting

1 Vsync_Out_pol

0 Vsync output polarity

0: Negitave

1: Positive

0x1A Misc_ctrl W/R

0 Hsync_Out_pol

0 Hsync output polarity

0: Negitave

1: Positive

7 Reserve 0 Reserve

6 chSyncpol 0 Video output data configuration, refer the

datasheet and programming guide.

1: output sync signal polarity from

Reg1A[1:0]

0: output sync signal polarity as the input.

5 Swap_O16b

0

1: when output 16-bit video data format, the

other 8 bits will be forced to low

4 Swap_Ch422

0

Channel Swap used in YUV422 mode.

0:Cr/Cb assigned to Data[23:16]

1:Cr/Cb assigned to Data[7:0]

3 Swap_OutRB 0 1: swap output channel 0 and channel 2

2 Swap_ML 0 1: swap output direction(MSB/LSB)

1 Swap_Pol 0 1: swap input data polarity

0x1B Video_map W/R

0 Swap_RB 0 1: swap input channel 0 and channel 2

剩余13页未读,继续阅读

唯周之翰

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0