没有合适的资源?快使用搜索试试~ 我知道了~

首页TM7705_中文数据手册

TM7705_中文数据手册

需积分: 49 29 下载量 18 浏览量

更新于2023-05-25

评论 1

收藏 1.27MB PDF 举报

TM7705_中文数据手册,需要资源的小伙伴可以下载看看。AD7705/7706 是应用于低频测量的2/3 通道的模拟前端。该器件可以接受直接来自传感器的低电平的输入信号,然后产生串行的数字输出。

资源详情

资源评论

资源推荐

©Titan Micro Electronics www.titanmec.com -1-

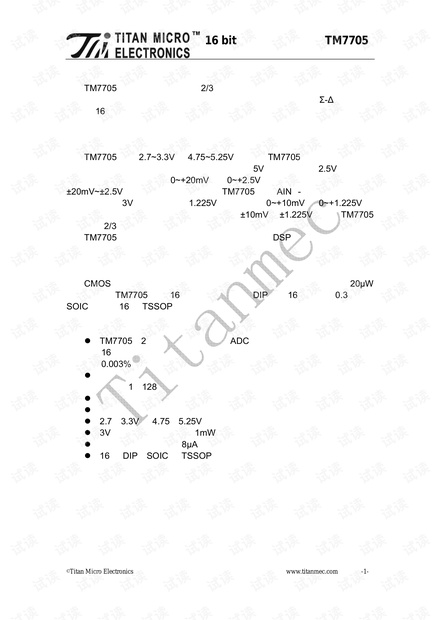

16 bit 模数转换器 TM7705

一、概述

TM7705 是应用于低频测量的 2/3 通道的模拟前端。该器件可以接受直接来

自传感器的低电平的输入信号,然后产生串行的数字输出。利用 Σ-∆ 转换技术

实现了 16 位无丢失代码性能。选定的输入信号被送到一个基于模拟调制器的增

益可编程专用前端。片内数字滤波器处理调制器的输出信号。通过片内控制寄存

器可调节滤波器的截止点和输出更新速率,从而对数字滤波器的第一个陷波进行

编程。

TM7705 只需 2.7~3.3V 或 4.75~5.25V 单电源。TM7705 是双通道全差分模

拟输入,带有一个差分基准输入。当电源电压为 5V、基准电压为 2.5V 时,该器

件都可将输入信号范围从 0~+20mV 到 0~+2.5V 的信号进行处理。还可处理

±20mV~±2.5V 的双极性输入信号,对于 TM7705 是以 AIN(-)输入端为参考点。

当电源电压为 3V、基准电压为 1.225V 时,可处理 0~+10mV 到 0~+1.225V 的

单极性输入信号,它的双极性输入信号范围是±10mV 到±1.225V。因此,TM7705

可以实现 2/3 通道系统所有信号的调理和转换。

TM7705 是用于智能系统、微控制器系统和基于 DSP 系统的理想产品。其

串行接口可配置为三线接口。增益值、信号极性以及更新速率的选择可用串行输

入口由软件来配置。该器件还包括自校准和系统校准选项,以消除器件本身或系

统的增益和偏移误差。

CMOS 结构确保器件具有极低功耗,掉电模式减少等待时的功耗至 20µW

(典型值)。TM7705 采用 16 脚塑料双列直插(DIP)和 16 脚宽体(0.3 英寸)

SOIC 封装和 16 脚 TSSOP 封装。

二、特点

z TM7705:2 个全差分输入通道的 ADC

16 位无丢失代码

0.003%非线性

z 可编程增益前端

增益:1~128

z 三线串行接口

z 有对模拟输入缓冲的能力

z 2.7~3.3V 或 4.75~5.25V 工作电压

z 3V 电压时,最大功耗为 1mW

z 等待电流的最大值为 8µA

z 16 脚 DIP、SOIC 和 TSSOP 封装

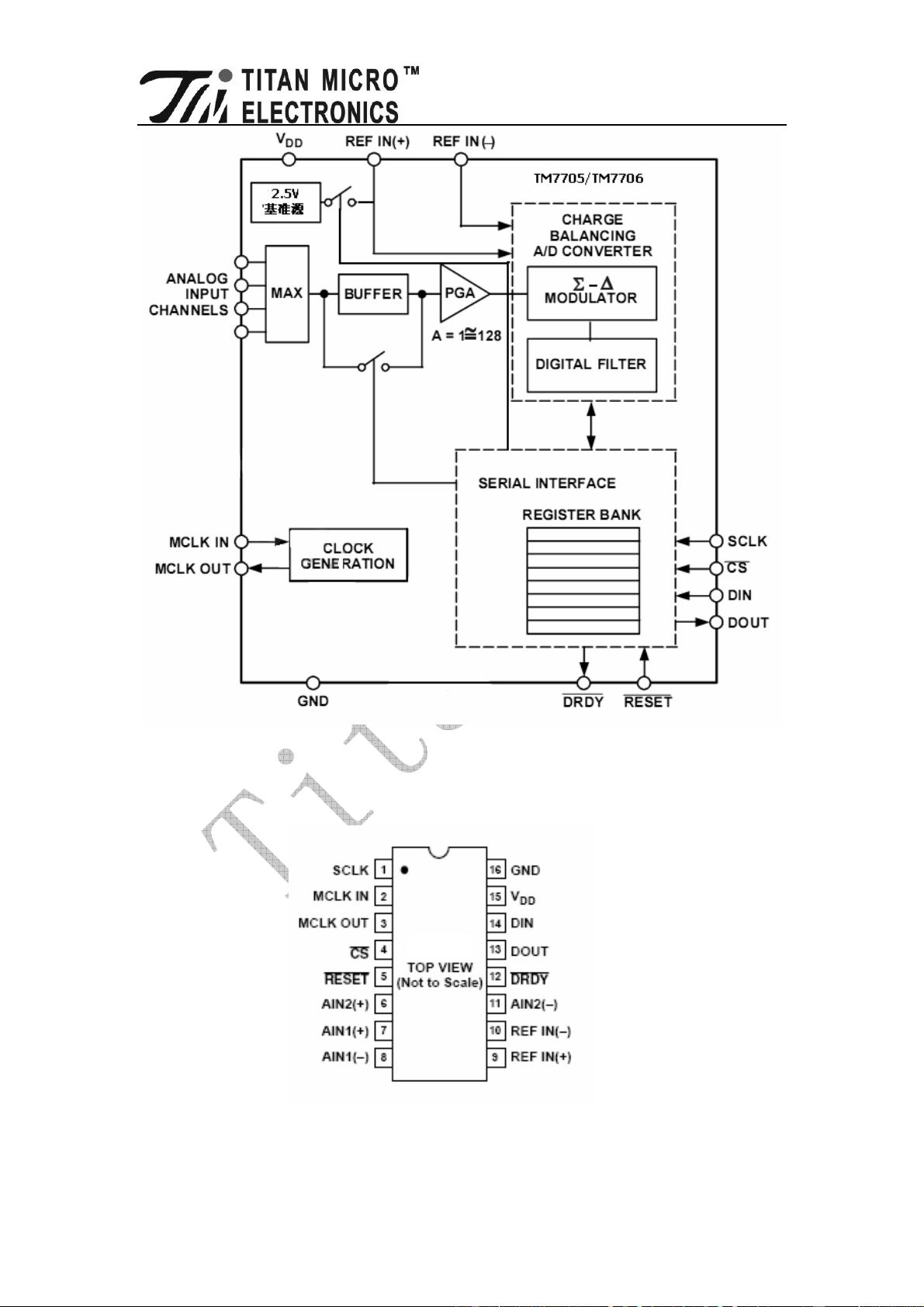

三、功能方框图

©Titan Micro Electronics www.titanmec.com -2-

16 bit 模数转换器 TM7705

四、引脚排列与功能

TM7705 的引脚排列

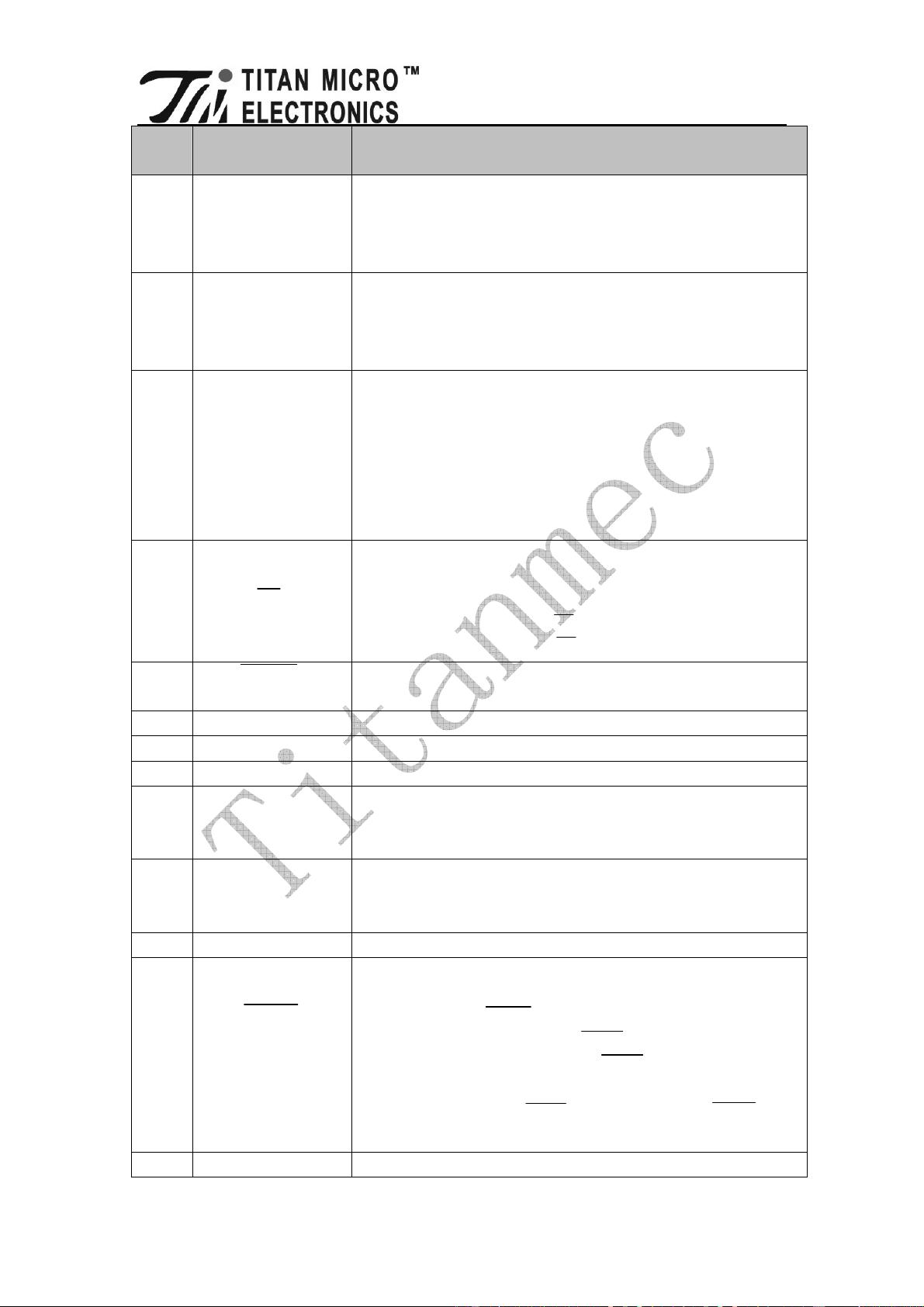

五、引脚功能

TM7705

©Titan Micro Electronics www.titanmec.com -3-

16 bit 模数转换器 TM7705

编号 名 称 功 能

1 SCLK

串行时钟,施密特逻辑输入。将一个外部的串行时钟加于这一

输入端口,以访问 TM7705 的串行数据。该串行时钟可以是连

续时钟以连续的脉冲串传送所有数据 。反之 ,它也可以是非

连续时钟 ,将信息以小批型数据发送给 TM7705

2 MCLK IN

为转换器提供主时钟信号。能以晶体/谐振器或外部时钟的形式

提供。晶体/谐振器可以接在 MCLK IN 和 MCLK OUT 二引

脚之间。此外,MCLK IN 也可用 CMOS 兼容的时钟驱动,

而 MCLK OUT 不连接。时钟频率的范围为 500kHz~5MHz

3 MCLK OUT

当主时钟为晶体/谐振器时,晶体/谐振器被接在 MCLK IN 和

MCLK OUT 之间。如果在 MCLK IN 引脚处接上一个外部时钟,

MCLK OUT 将提供一个反相时钟信号。这个时钟可以用来为外

部电路提供时钟源,且可以驱动一个 CMOS 负载。如果用户

不需要,MCLK OUT 可以通过时钟寄存器中的 CLK DIS 位关

掉。这样,器件不会在 MCLK OUT 脚上驱动电容负载而消耗

不必要的功率

4

CS

片选,低电平有效的逻辑输入,选择 TM7705。将该引脚接为

低电平,TM7705 能以三线接口模式运行 (以 SCLK、DIN 和

DOUT 与器件接口)。在串行总线上带有多个器件的系统中,

可由 CS 对这些器件作出选择,或在与 TM7705 通信时,CS

可用作帧同步信号

5

RESET

复位输入。低电平有效的输入,将器件的控制逻辑、接口逻辑、

校准系数、数字滤波器和模拟调制器复位至上电状态

6 AIN2(+)[AIN1]

对于 TM7705,差分模拟输入通道 2 的正输入端。

7 AIN1(+)[AIN2]

对于 TM7705,差分模拟输入通道 1 的正输入端。

8 AIN1(-)[COMMON]

对于 TM7705,差分模拟输入通道 1 的负输入端;

9

REF IN(+)

基准输入端。TM7705 差分基准输入的正输入端。基准输入是

差分的,并规定 REF IN (+)必须大于 REF IN (-)。REF

IN (+)可以取 V

DD

和 GND 之间的任何值

10

REF IN(-)

基准输入端。TM7705 差分基准输入的负输入端。REF IN(- )

可以取 V

DD

和 GND 之间的任何值,且满足 REF IN(+ )大 于

REF IN (- )

11

AIN2(-)[AIN3] 对于 TM7705,差分模拟输入通道 2 的负输入端。

12

DRDY

逻辑输出。这个输出端上的逻辑低电平表示可从 TM7705 的数

据寄存器获取新的输出字。完成对一个完全的输出字的读操作

后,DRDY 引脚立即回到高电平。如果在两次输出更新之间,

不发生数据读出,DRDY 将在下一次输出更新前 500 ×t

CLKIN

时间返回高电平。当 DRDY 处于高电平时,不能进行读操作,

以免数据寄存器中的数据正在被更新时进行读操作。当数据被

更新后,DRDY 又将返回低电平。DRDY 也用来指示何时

TM7705 已经完成片内的校准序列

13 DOUT

串行数据输出端。从片内的输出移位寄存器读出的串行数据由

©Titan Micro Electronics www.titanmec.com -4-

16 bit 模数转换器 TM7705

此端输出。根据通讯寄存器中的寄存器选择位,移位寄存器可

容纳来自通讯寄存器、时钟寄存器或数据寄存器的信息

14 DIN

串行数据输入端。向片内的输入移位寄存器写入的串行数据由

此输入。根据通讯寄存器中的寄存器选择位,输入移位寄存器

中的数据被传送到设置寄存器、时钟寄存器或通讯寄存器

15 V

DD

电源电压,+2.7V~+5.25V

16 GND

内部电路的地电位基准点

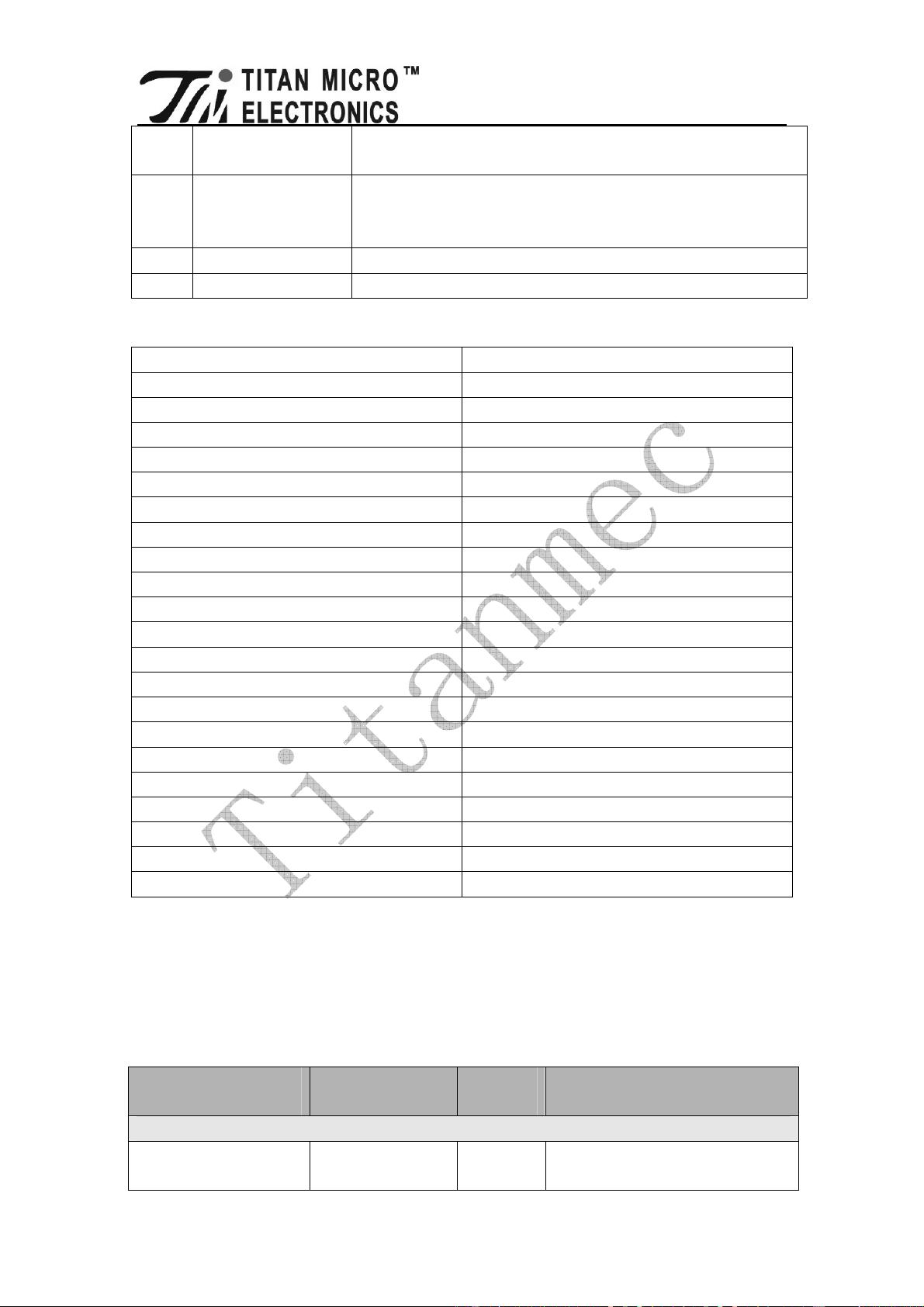

六、极限参数(TA = +25℃,除非另有说明)

V

DD

对 GND -0.3V ~+7V

模拟输入电压对 GND -0.3V ~V

DD

+0.3V

基准输入电压对 GND -0.3V ~V

DD

+0.3V

数字输入电压对 GND -0.3V ~V

DD

+0.3V

数字输出电压对 GND -0.3V ~V

DD

+0.3V

工作温度范围 (商业级,B ) -40℃~+85℃

储存温度范围 -65℃~+150℃

结温 +150℃

功耗 (塑料 DIP 封装)

450mW

θ

JA

热阻 105℃/W

引脚温度 (焊接 ,10 秒) +260℃

功耗(塑料 SOIC 封装)

450mW

θ

JA

热阻 75℃/W

引脚温度 (焊接 )

汽相 (60 秒) +215℃

红外线 (15 秒) +220℃

功耗 (SSOP 封装)

450mW

θ

JA

热阻 139℃/W

引脚温度(焊接)

汽相(60 秒) +215℃

红外线(15 秒) +220℃

抗 ESD

>4000V

注:强度超出所列的极限参数可能导致器件的永久性损坏。这些仅仅是极限参数,

并不意味着在极限条件下或在任何其它超出推荐工作条件所示参数的情况下器

件能有效地工作。延长在极限参数条件下的工作时间会影响器件的可靠性。

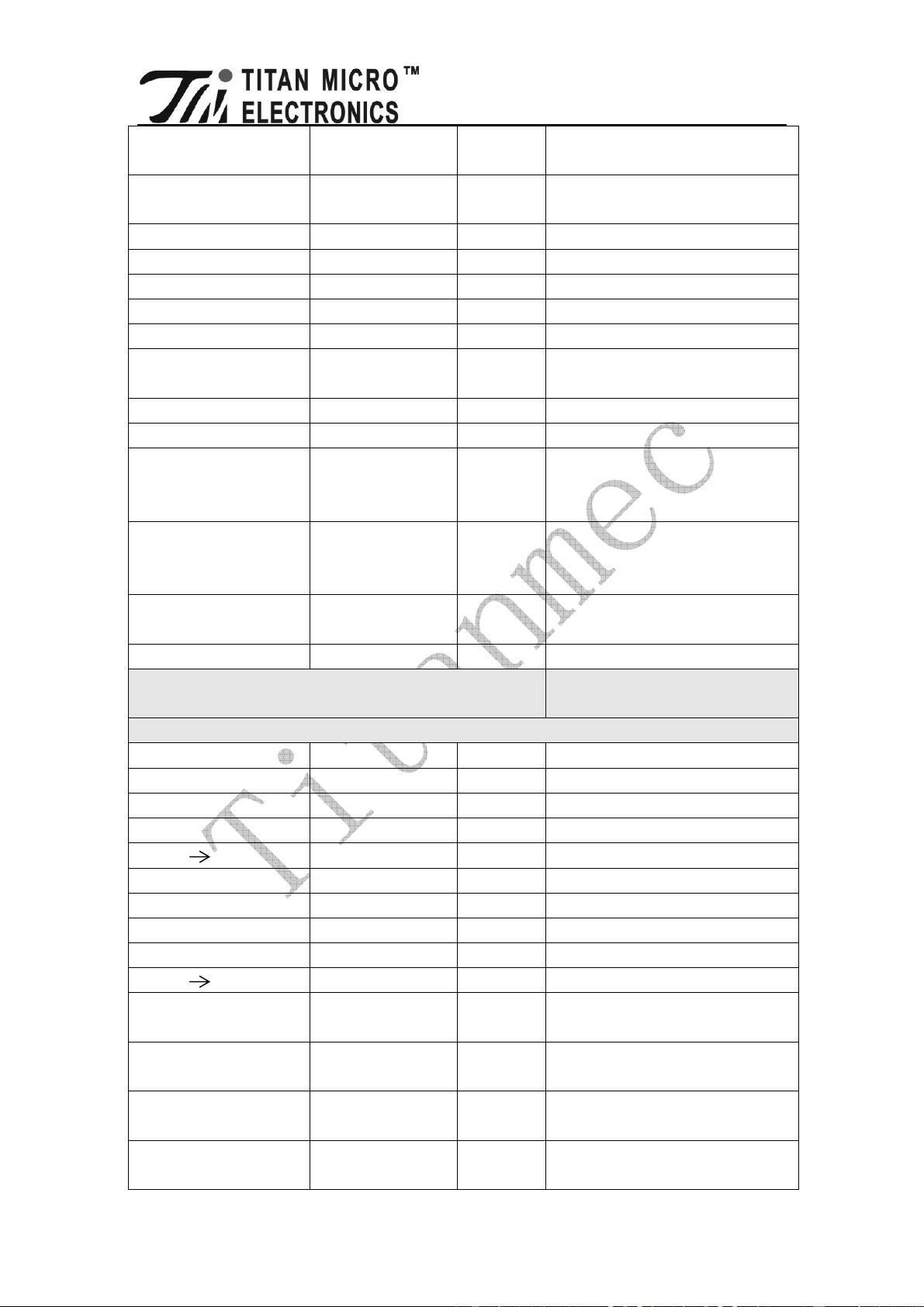

七、电特性

(V

DD

=+3V 或+5V,REF IN(+)=+1.225V;REF IN(-)=GND,MCLK IN

=2.4576MHz,T

A

=T

MIN

~T

MAX

,除非另有说明)。

Parameter B Version

1

Units Conditions/Comments

STATIC PERFORMANCE

No Missing Codes 16 Bits min

Guaranteed by Design. Filter

Notch < 60 Hz

©Titan Micro Electronics www.titanmec.com -5-

16 bit 模数转换器 TM7705

Output Noise

See Tables I and

III

Dependson Filter Cutoffs and

Selected Gain

Integral Nonlinearity

2

±0.003

%of FSR

max

Filter Notch < 60 Hz. Typically

0.0003%

Unipolar Offset Error See Note3

Unipolar Offset Drift

4

0.5

µV/℃ typ

Bipolar Zero Error See Note 3

Bipolar Zero Drift

4

0.5

µV/℃ typ

For Gains1,2and4

0.1

µV/℃ typ

For Gains8,16,32,64and128

Positive Full-Scale

Error

5

See Note3

Full-Scale Drift

4.6

0.5

µV/℃ typ

Gain Error

7

See Note3

Gain Drift

4.8

0.5

ppm of

FSR/ ℃

typ

Bipolar Negative Full

-Scale Error

2

±0.003

%of

FSR/℃

typ

Typically±0.001%

Bipolar Negative Full

-Scale Drift

4

1

µV/℃typ

For Gains of 1 to 4

0.6

µV/℃ typ

For Gains of 8 to 128

ANALOG INPUTS/REFERENCE INPUTS

Specifications for AIN and

REF IN UnlessNoted

Input Common-Mode Rejection(CMR)

2

V

DD

=5V

Gain=1 96 dB typ

Gain=2 105 dB typ

Gain=4 110 dB typ

Gain=8 128 130 dB typ

V

DD

=3V

Gain=1 105 dB typ

Gain=2 110 dB typ

Gain=4 120 dB typ

Gain=8 128 130 dB typ

Normal-Mode50Hz

Rejection

2

98 dB typ

For Filter Notches of

25Hz,50Hz,±0.02×f

NOTCH

Normal-Mode60Hz

Rejection

2

98 dB typ

For Filter Notches of

20Hz,60Hz,±0.02×f

NOTCH

Common-Mode 50Hz

Rejection

2

150 dB typ

For Filter Notches of

25Hz,50Hz,±0.02×f

NOTCH

Common-Mode 60Hz

Rejection

2

150 dB typ

For Filter Notches of

20Hz,60Hz,±0.02×f

NOTCH

剩余40页未读,继续阅读

Levin_Yu

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- zigbee-cluster-library-specification

- JSBSim Reference Manual

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0