南亚 DDR3 4Gb 内存芯片技术规格解析

需积分: 50 123 浏览量

更新于2023-05-25

1

收藏 4.3MB PDF 举报

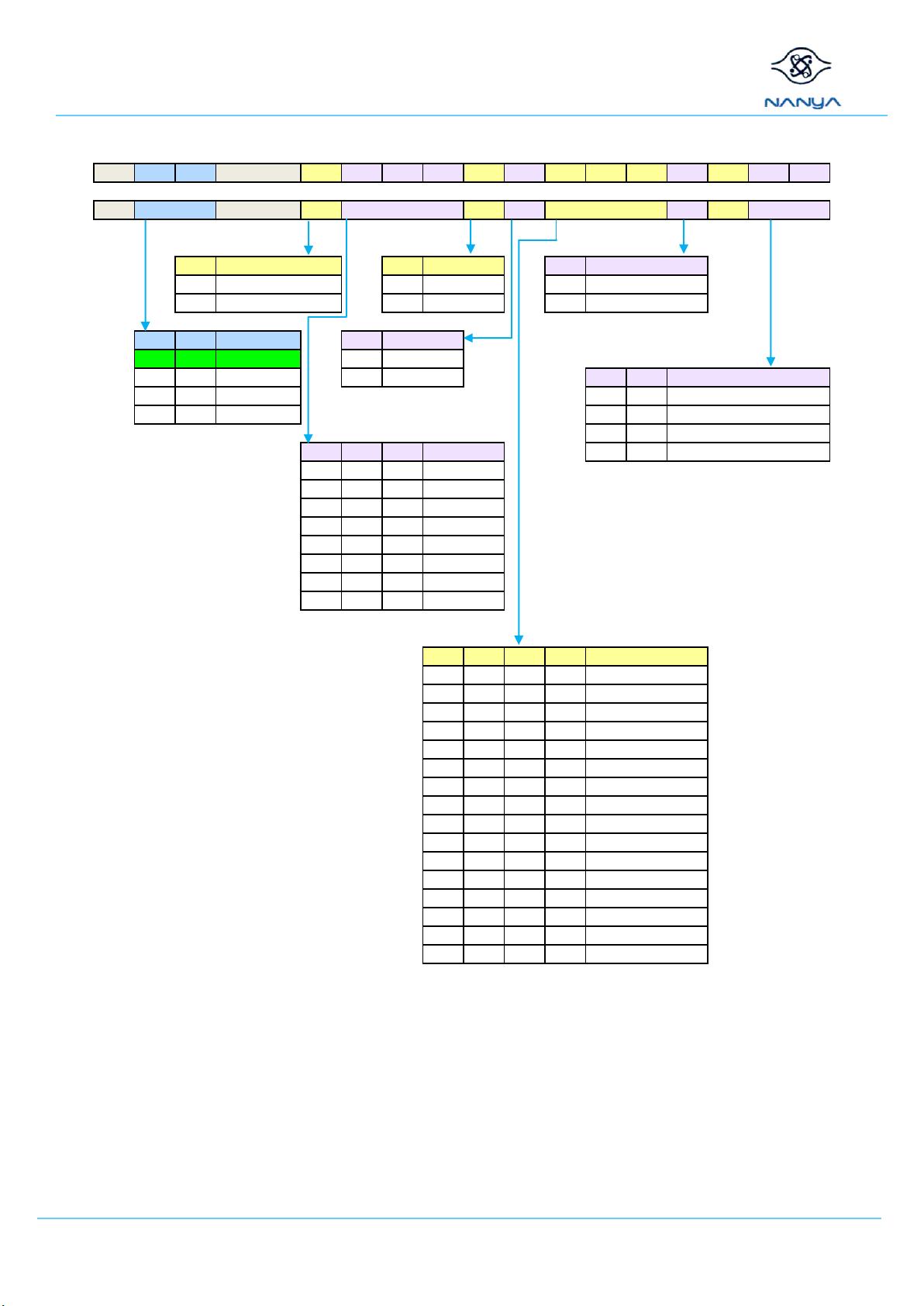

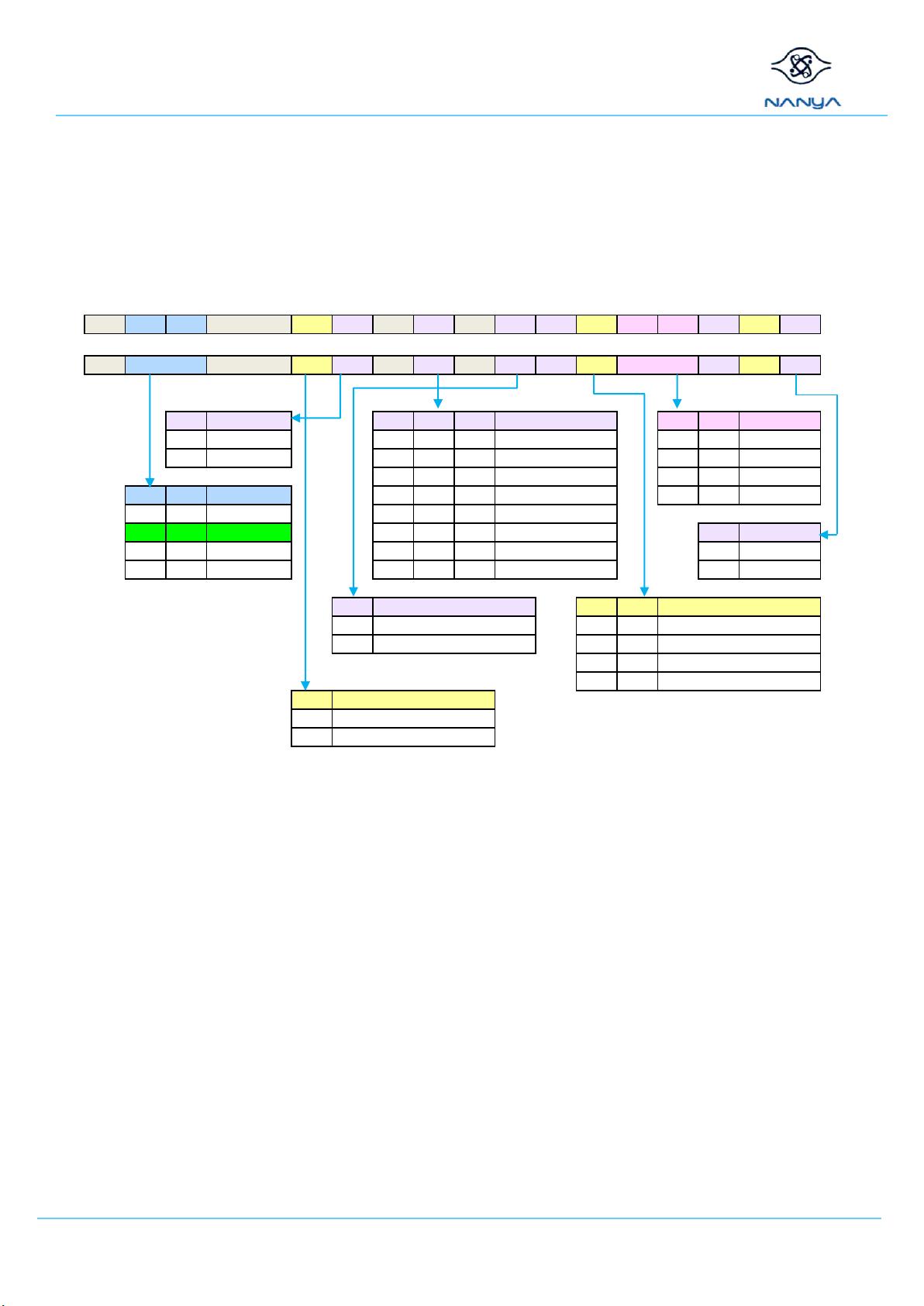

"Nanya南亚DDR3规格书详细介绍了其4Gb DDR3(L)动态随机存取存储器,这是一种高速CMOS SDRAM,包含4,294,967,296位数据。它内部配置为八银行结构。4Gb芯片有两种组织形式:64Mbit x 8 I/O x 8 banks 和 32Mbit x16 I/O x 8 banks。这些同步设备实现了高达2133 Mb/sec/pin的双倍数据速率传输速度,适用于通用应用。芯片设计符合所有关键DDR3(L) DRAM特性,控制和地址输入与外部提供的差分时钟同步,输入在时钟交叉点(CK上升沿和CKneg下降沿)被捕捉。所有I/O与单端DQS或差分DQS对源同步。设备运行时只需1.5V ± 0.075V或1.35V -0.067V/+0.1V的电源,并提供BGA封装。文档还提到了DDR3(L)的特性,如8n预取架构、差分时钟和数据 strobe、双数据速率操作、数据完整性保护、自动自刷新、部分阵列自刷新以及节能模式等。"

DDR3内存是一种先进的存储技术,DDR3L是低功耗版本,兼容于DDR3。此规格书中详细描述了4Gb DDR3L芯片的规格和功能,包括以下要点:

1. **内存容量与组织**:4Gb DDR3 DRAM提供64Mbit x 8 I/O x 8 banks和32Mbit x16 I/O x 8 banks两种组织形式,这意味着它可以提供不同的存储密度和接口宽度。

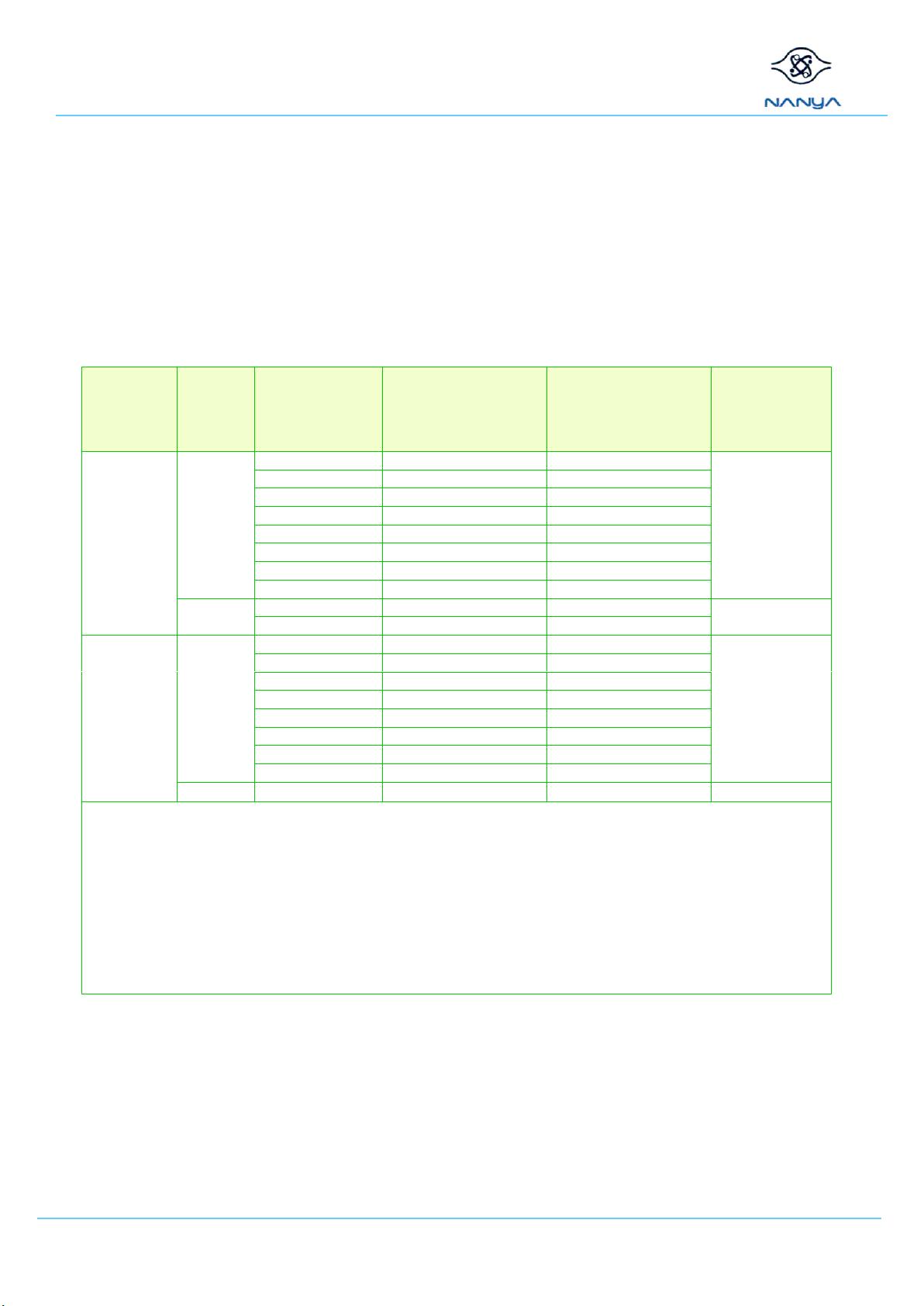

2. **传输速度**:该芯片设计为实现最高2133 Mb/sec/pin的数据传输速率,这是通过双倍数据速率技术在每个时钟周期的上升沿和下降沿传输数据来实现的。

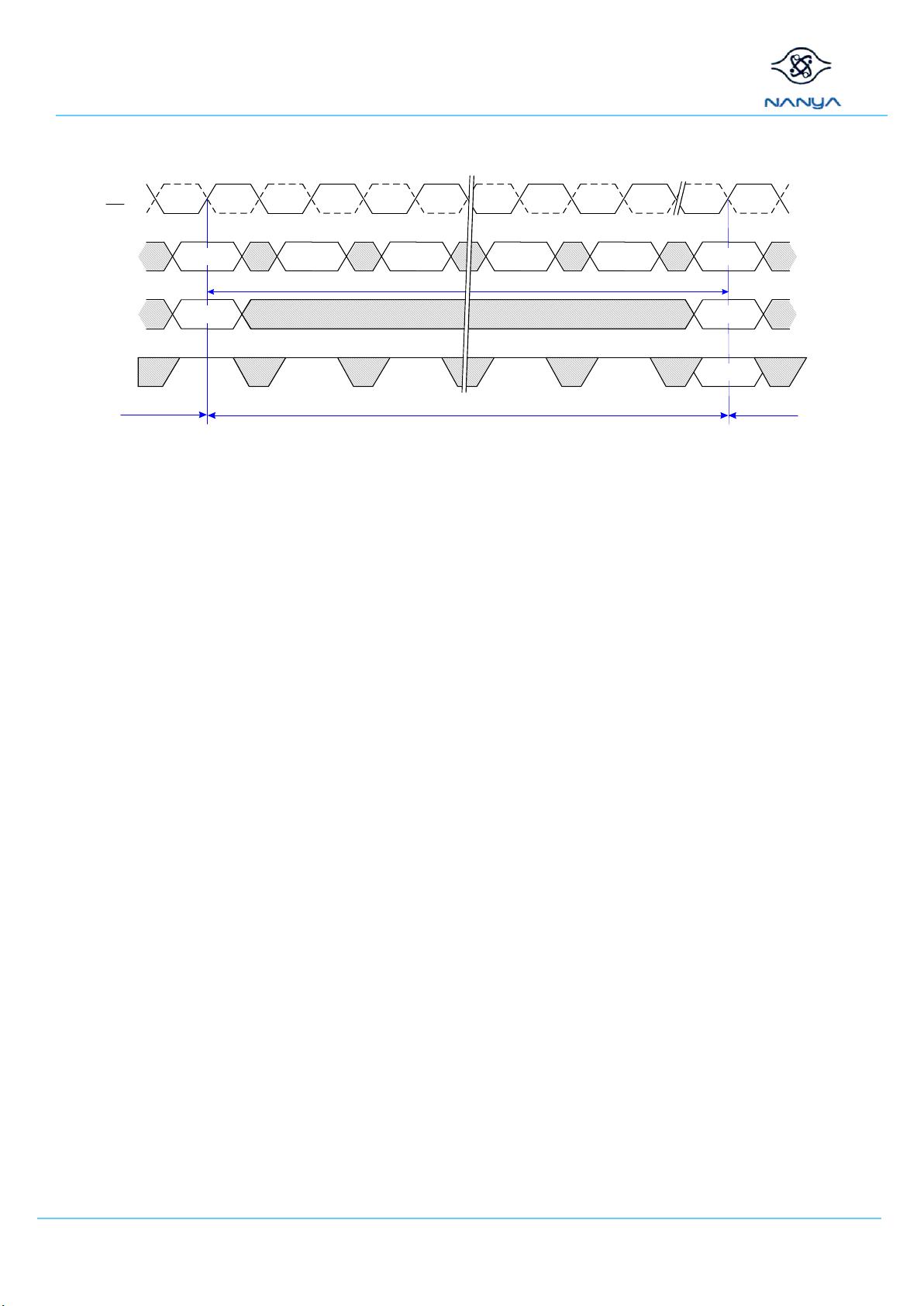

3. **同步与时钟**:所有的输入信号都是与一对外部差分时钟同步的,且在时钟交叉点被采样,确保了高速传输下的精确性。

4. **电源管理**:DDR3L支持1.5V和1.35V两种电源电压,其中1.35V版本是低功耗设计,同时与1.5V DDR3兼容,但1.35V DDR3L-RS例外。

5. **数据完整性**:包括自动自刷新(ASR)和自动刷新模式,通过内置温度传感器保证数据的完整性。此外,当温度超过85°C时,需要外部以2倍刷新率进行刷新。

6. **节能模式**:支持部分数组自刷新(PASR),允许只刷新正在使用的内存部分,从而节省电力。

7. **其他特性**:支持8n预取架构,即每次时钟周期读取或写入8位数据;DQS和DQS差分数据 strobe 用于数据的精确时序控制;DM数据掩码信号用于提高数据传输的可靠性。

这份规格书对于理解DDR3 DRAM的工作原理、性能参数以及如何在系统中正确使用这些内存是非常重要的参考资料。无论是设计电路板、编程还是故障排查,都离不开这些详细的技术指标和功能描述。

2020-05-02 上传

2012-03-07 上传

2012-11-22 上传

2018-05-03 上传

2015-05-10 上传

2022-08-03 上传

2021-08-04 上传

fctheone

- 粉丝: 2

- 资源: 8

最新资源

- CoreOS部署神器:configdrive_creator脚本详解

- 探索CCR-Studio.github.io: JavaScript的前沿实践平台

- RapidMatter:Web企业架构设计即服务应用平台

- 电影数据整合:ETL过程与数据库加载实现

- R语言文本分析工作坊资源库详细介绍

- QML小程序实现风车旋转动画教程

- Magento小部件字段验证扩展功能实现

- Flutter入门项目:my_stock应用程序开发指南

- React项目引导:快速构建、测试与部署

- 利用物联网智能技术提升设备安全

- 软件工程师校招笔试题-编程面试大学完整学习计划

- Node.js跨平台JavaScript运行时环境介绍

- 使用护照js和Google Outh的身份验证器教程

- PHP基础教程:掌握PHP编程语言

- Wheel:Vim/Neovim高效缓冲区管理与导航插件

- 在英特尔NUC5i5RYK上安装并优化Kodi运行环境