没有合适的资源?快使用搜索试试~ 我知道了~

首页AD9910中文数据手册

AD9910中文数据手册

需积分: 50 135 下载量 103 浏览量

更新于2023-05-26

评论 5

收藏 959KB PDF 举报

AD9910是一款内置14位DAC的直接数字频率合成器,支持高达1GPS采样速率。AD9910采用高级DDS专利技术,在不牺牲性能的前提下可极大降低功耗。DDS/DAC组合构成数字可编程的高频模拟输出频率合成器,能够在高达400MHz的频率下生成捷变正弦波形。用户可以访问三个用于控制DDS的信号控制参数,包括:频率、相位与振幅。该DDS利用32位累加器提供快速跳频和频率调谐分辨率。在1GPS采样速率下,调谐分辨率约为0.23Hz。这款DDS还实现了快速相位与幅度切换等许多功能。

资源详情

资源评论

资源推荐

ADIዐ࿔Ӳຕ֩ᆈ࿔Ӳຕ֩ڦᅳ࿔Lj൩ଌᅳዐీ٪ሞڦᇕჾፇኯᅳٱဃLjADIփܔᅳዐ٪ሞڦֶᅴᆯׂُิڦٱဃሴăසႴඓණඪࢆَᇕڦጚඓႠLj൩֖ADI༵ࠃ

ڦፌႎᆈ࿔Ӳຕ֩ă

1 GSPSĂ14࿋Ă3.3 V CMOS

থຕጴೕ୲ࢇׯഗ

AD9910

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113 ©2007–2008 Analog Devices, Inc. All rights reserved.

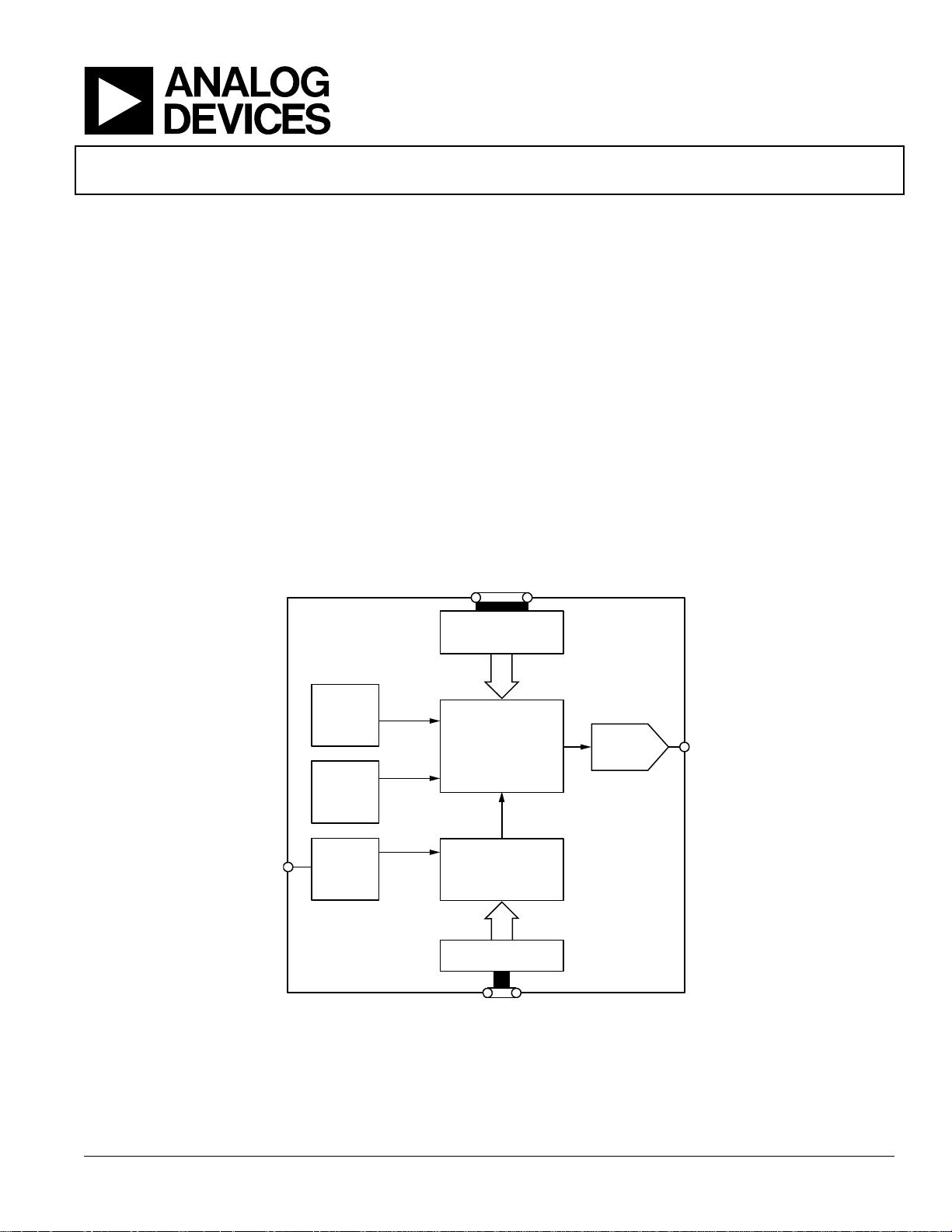

14-BIT DAC

1GSPS DDS CORE

LINEAR

RAMP

GENERATOR

1024-

ELEMENT

RAM

HIGH SPEED PARALLEL

DATA INTERFACE

TIMING AND CONTROL

SERIAL CONTROL

DATA PORT

REFCLK

MULTIPLIER

06479-001

AD9910

༬Ⴀ

1 GSPSాև้ዓ܈(ߛٳ400 MHzఇె)

ాዃ1 GSPSĂ14࿋DAC

ೕ୲ݴՐ୲ǖ0.23 Hzᅜฉ

၎࿋ሯำǖ≤–125 dBc/Hz(1 kHzೋᅎLj400 MHzሜհ)

ጝሁڦۯༀႠీǖ>80 dB ټSFDR

زႜ/(I/O)

ጲۯ၍Ⴀඪᅪೕ୲/၎࿋/ናޗ௮ࠀీ

8ዖೕ୲ࢅ၎࿋ೋᅎႚ๕

Sin(X)/(X)ၯኟ(ݒኟ၀୳հഗ)

֑ᆩ1.8 Vࢅ3.3 Vۉᇸࠃۉ

/ᆘڦูۉࠀీ

100ᆅগTQFP_EPހጎ

ׯ1024ጴ×32࿋ڦRAM

PLL REFCLKױ݆ഗ

ժႜຕୟ০থ

ڇৗ༹ൻۯڦాևናږഗ

ۙ၎ࠀీ

ۙޗࠀీ

ܠഗཞօ

ᆌᆩ

যՎԨና(LO)ೕ୲ࢇׯ

Պײ้ዓ݀ิഗ

ૃٳࢅ௮ဣཥڦFM၍Ⴀۙೕᇸ

֪ᇑ֪ଉยԢ

ำ࠼ยԢൻۯഗ

ࣅۙഗ

ཌೕ

ࠀీ

1.

!ྔևPLL࣍ୟ୳հഗᇮ ................................................... 27

PLLۨኸସ ................................................................................. 27

ናޗ(OSK) .................................................................... 27

!ۯOSK ................................................................................ 27

!ጲۯOSK ................................................................................ 28

ຕጴၽೢ݀ิഗ(DRG) ............................................................... 28

DRG߁ຎ ................................................................................ 28

DRGၽ୲ ....................................................................... 30

DRG၌ኵ ....................................................................... 30

DRGેഗൣଭ .................................................................. 30

! ኟၽೢ݀ิ ....................................................................... 30

! ݥጂାၽೢ݀ิ ................................................................... 32

DROVERᆅগ ....................................................................... 32

RAM ....................................................................................... 33

RAM߁ຎ ............................................................................... 33

RAMሜ/܁ൽ֡ፕ ............................................................ 33

RAMխݣ֡ፕ)հႚ݀ิ* .................................................. 33

RAM_SWP_OVR)RAM௮ྜׯ*ᆅগ ........................... 34

RAMխݣఇ๕߁ຎ .............................................................. 34

RAMথገ࣑ఇ๕ .............................................................. 34

! ଭሁRAM

থገ࣑ఇ๕ ................................................ 35

RAMฉၽೢఇ๕ .................................................................. 35

RAMฉၽೢాևProleఇ๕ ..................................... 36

!ాևProleჄհႚ้Ⴞ ...................................... 38

RAMມၠၽೢఇ๕ .............................................................. 38

RAMჄມၠၽೢఇ๕ ..................................................... 39

RAMჄთ࣍ఇ๕ .............................................................. 41

ഄ༬Ⴀ ........................................................................................ 42

Prole ...................................................................................... 42

I/O_UPDATEĂSYNC_CLKࢅဣཥ้ዓ࠲ဣ ............... 42

!ጲۯI/O߸ႎ .......................................................................... 43

༬Ⴀ ................................................................................................... 1

ᆌᆩ ................................................................................................... 1

ࠀీ ........................................................................................... 1

Ⴊ۩૦๏ ........................................................................................... 4

߁ຎ ................................................................................................... 5

ຍࡀ߭ ........................................................................................... 6

ۉഘࡀ߭ .................................................................................. 6

ܔፌٷܮۨኵ ............................................................................. 9

ڪၳۉୟ .................................................................................. 9

ESDয়ߢ ................................................................................... 9

ᆅগದዃࢅࠀీ௮ຎ

................................................................... 10

ۆ႙߾ፕ༬Ⴀ ................................................................................ 13

ᆌᆩۉୟ ........................................................................................ 16

߾ፕᇱ ........................................................................................ 17

! ڇೕۙఇ๕ ....................................................................... 17

RAMۙఇ๕ ...................................................................... 18

! ຕጴၽೢۙఇ๕ .............................................................. 19

! ժႜຕ܋ۙఇ๕ ...................................................... 20

! !!ժႜຕ้ዓ(PDCLK) ................................................... 20

! !!݀ໃ๑ీ(TxENABLE) .................................................... 21

! ఇ๕ᆫံ ............................................................................ 22

ࠀీၘ ................................................................................ 23

DDSాࢃ ................................................................................ 23

14࿋DAC ....................................................................... 23

! !!ޤዺDAC ............................................................................ 24

!ݒsinc୳հഗ ......................................................................... 24

! ้ዓ(REF_CLK/REF_CLK) ........................................ 24

REF_CLK/REF_CLK ߁ຎ ............................................... 24

! !!ৗ༹ൻۯREF_CLK/REF_CLK ....................................... 25

! !!থൻۯREF_CLK/REF_CLK ....................................... 25

! !!၎࣍(PLL)ױ݆ഗ ......................................................... 25

PLLۉࢁԭ ......................................................................... 26

ణ

AD9910

Rev. B | Page 2 of 64

! !!/ް࿋(I/O_RESET) .......................................... 49

!!!/߸ႎ(I/O_UPDATE) ...................................... 49

!زႜI/O ้Ⴞ ..................................................................... 49

MSB/LSBد ........................................................................ 49

٪ഗࢅ࿋ࠀీ௮ຎ .............................................................. 50

! ٪ഗ࿋ࠀీ௮ຎ .............................................................. 55

! !!ࠀీ٪ഗ1 (CFR1)—ں0x00 .......................... 55

! !!ࠀీ٪ഗ2 (CFR2)—ں0x01 .......................... 57

! !!ࠀీ٪ഗ3 (CFR3)—ں0x02 .......................... 58

!!!ޤዺDAC٪ഗ—ں0x03 ................................. 58

!!!I/O߸ႎ୲٪ഗ—ں0x04 .................................... 59

! !!ೕ୲ۙၿጴ٪ഗ(FTW)— ں0x07 ......................... 59

! !!၎࿋ೋᅎጴ٪ഗ(POW)—ں0x08 ......................... 59

! !!ናޗԲ૩ᅺጱ٪ഗ(ASF)—ں0x09 ....................... 59

! !!ܠႊೌཞօ٪ഗ—ں0x0A ..................................... 60

! !!ຕጴၽೢ၌ኵ٪ഗ—ں0x0B ................................. 60

! !!ຕጴၽೢօ٪ഗ—ں0x0C ................................. 60

! !!ຕጴၽೢ୲٪ഗ—ں0x0D ................................ 60

!!!Prole٪ഗ ..................................................................... 61

ྔႚ٫ ........................................................................................ 62

! ۩ࠔኸళ ................................................................................ 73

! ูۉ ................................................................................ 43

ܠഗཞօ .................................................................................... 44

ۉᇸݴፇ ........................................................................................ 47

3.3 Vۉᇸ ................................................................................ 47

DVDD_I/O (3.3V))ᆅগ11/15/21/28/45/56/66*

........... 47

AVDD (3.3V))ᆅগ7477/83* ...................................... 47

1.8 Vۉᇸ ................................................................................ 47

DVDD (1.8V))ᆅগ17/23/30/47/57/64* ......................... 47

AVDD (1.8V))ᆅগ3* ........................................................ 47

AVDD (1.8V))ᆅগ6* ........................................................ 47

AVDD (1.8V))ᆅগ89/92* ................................................ 47

زႜՊײ ........................................................................................ 48

! থ—زႜI/O ............................................................. 48

! ཚᆩزႜI/O֡ፕ ................................................................. 48

! ኸସጴব ................................................................................ 48

! !!ኸସጴব႑တ࿋ ........................................................... 48

!زႜI/O܋ᆅগࠀీ௮ຎ ............................................... 48

! !!زႜ้ዓ(SCLK) ............................................................... 48

!!!CSႊೌስԀ ................................................................... 48

! !!زႜຕ/(SDIO) ............................................ 48

! !!زႜຕ(SDO) ........................................................ 48

AD9910

Rev. B | Page 3 of 64

Ⴊ߀“DVDD (1.8V)(ᆅগ17/23/30/47/57/64)”ևݴࢅ

“AVDD (1.8V)(ᆅগ89/92)”ևݴ ............................................... 47

Ⴊ߀“থ—زႜI/O”ևݴ ................................................ 48

Ⴊ߀17 ......................................................................................... 50

Ⴊ߀19 ......................................................................................... 57

Ⴊ߀20ࢅ21 ................................................................................ 58

20082ሆ—Ⴊ۩Ӳ0Ⴊ۩ӲA

Ⴊ߀“༬Ⴀ”ևݴ .............................................................................. 1

Ⴊ߀1ዐREFCLKױ݆ഗຍࡀ߭ .......................................... 5

Ⴊ߀SYNC_CLKፌ܌ยዃ้ .................................................... 6

Ⴊ߀I/O Update/Prole[2:0]้Ⴞ༬Ⴀ ........................................ 6

Ⴊ߀TxENABLE/ຕยዃ้(PDCLK)ࢅ

TxENABLE/ຕԍ้(PDCLK) ...................................... 6

Ⴊ߀ഄ้Ⴞ༬Ⴀևݴ ................................................................ 6

Ⴊ߀3 ........................................................................................... 10

Ⴊ߀9

Ă10Ă11Ă12Ă13ࢅ14 .......................... 12

Ⴊ߀30ࢅ7 .............................................................................. 24

Ⴊ߀“ጲۯI/O߸ႎ”ևݴ ............................................................. 41

ሺ16LjዘႎಇႾ ................................................................... 41

Ⴊ߀4953 ........................................................................... 43

ሺ“ۉᇸݴፇ”ևݴ ................................................................... 46

ሺ“ཚᆩزႜI/O֡ፕ”ևݴ .................................................... 47

Ⴊ߀17 ......................................................................................... 49

Ⴊ߀19 ......................................................................................... 56

Ⴊ߀20 ......................................................................................... 57

ሺ32 ......................................................................................... 60

20075ሆ—Ⴊ۩Ӳ0ǖ؛๔Ӳ

200812ሆ—Ⴊ۩ӲAႪ۩ӲB

Ⴊ߀2 ............................................................................................ 5

1ዐڦI/O_UPDATE

ஞ؋܈֖ຕࢅ

Proleፌ܌ൎ࣑ዜ֖ຕ߸߀ .................................................... 7

1ዐሺXTAL_SEL֖ຕ .................................................. 8

Ⴊ߀3 ........................................................................................... 11

Ⴊ߀20 ......................................................................................... 16

Ⴊ߀22 ......................................................................................... 17

Ⴊ߀23 ......................................................................................... 18

Ⴊ߀24 ......................................................................................... 19

Ⴊ߀25 ......................................................................................... 20

Ⴊ߀“REF_CLK/REF_CLK߁ຎ”ևݴ ....................................... 24

Ⴊ߀“ৗናREF_CLK/REF_CLK ”ևݴ ...................................... 25

Ⴊ߀“PLLۨኸସ”ևݴࢅ

“ናޗ(OSK)”ևݴ ........................................................ 27

Ⴊ߀“DRGၽ୲”ևݴࢅ“Քጚၽೢ݀ิ”ևݴ ............... 30

Ⴊ߀“DROVERᆅগ”ևݴ ........................................................... 32

Ⴊ߀43 ......................................................................................... 35

Ⴊ߀“45ࢅాևProleჄհႚ้Ⴞ”

ևݴ ................................................................................................. 38

Ⴊ߀47 ......................................................................................... 40

Ⴊ߀48 ......................................................................................... 41

أ“I/O_UPDATEᆅগ”ևݴ ................................................... 41

Ⴊ߀“Prole”ևݴ ......................................................................... 42

ሺ“I/O_UPDATEĂSYNC_CLKࢅဣཥ้ዓ࠲ဣ”ևݴ ... 42

ሺ“

49ǗዘႎಇႾ” ............................................................... 42

Ⴊ߀“ܠഗཞօ”ևݴ ............................................................... 44

AD9910

Rev. B | Page 4 of 64

Ⴊ۩૦๏

AD9910

Rev. B | Page 5 of 64

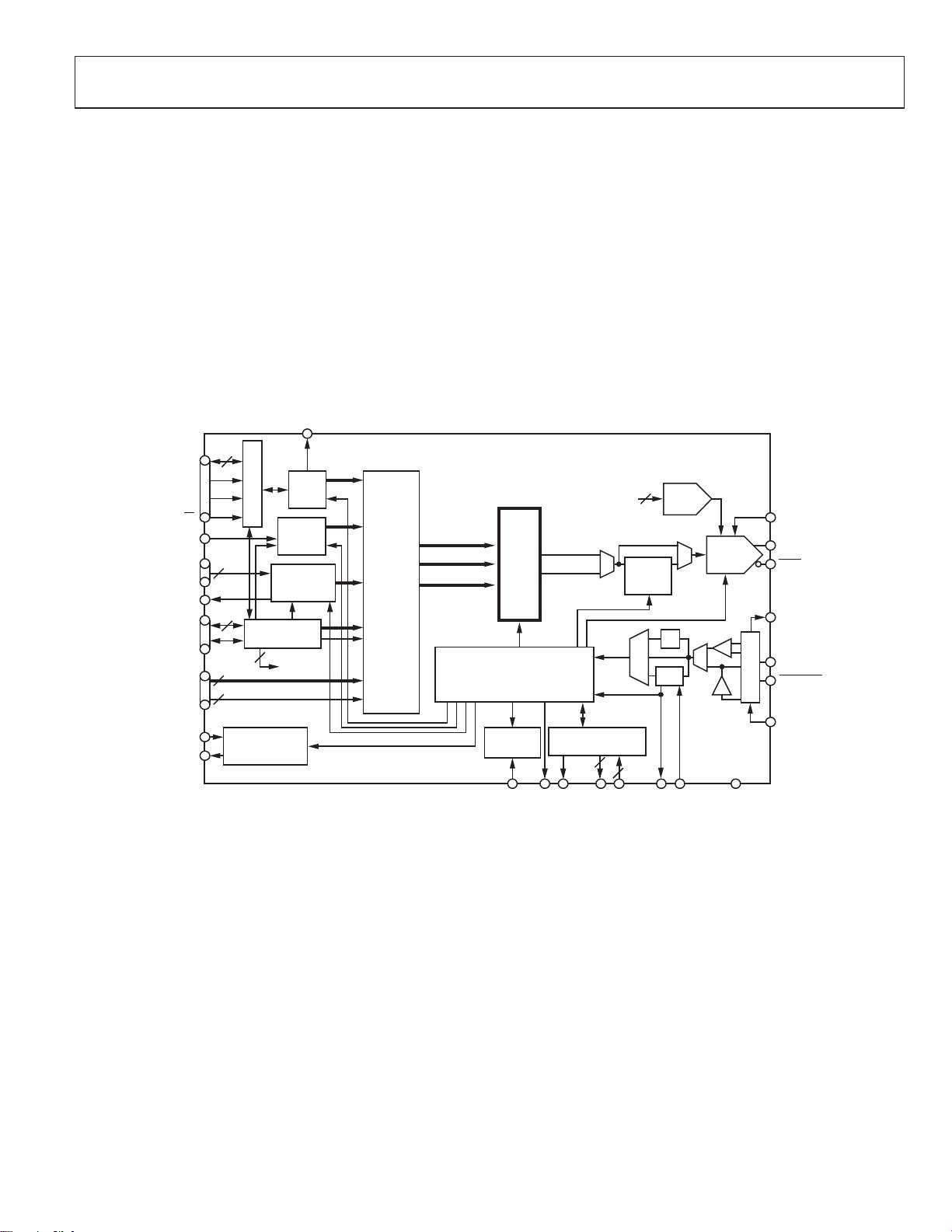

߁ຎ

06479-002

16

PARALLEL

INPUT

PDCLK

SCLK

SDIO

I/O_RESET

PROFILE[2:0]

I/O_UPDATE

RAM

POWER-

DOWN

CONTROL

EXT_PWR_DWN

DAC_RSET

IOUT

IOUT

CS

TxENABLE

DAC FSC

OSK

RAM_SWP_OVR

A

θ

INVERSE

SINC

FILTER

CLOCK

AMPLITUDE (A)

FREQUENCY (ω )

PHASE (θ)

DIGITAL

RAMP

GENERATOR

8

DAC FSC

8

2

DRCTL

DRHOLD

DROVER

2

MULTICHIP

SYNCHRONIZATION

SYSCLK

PLL

÷2

CLOCK MODE

REF_CLK

REF_CLK

REFCLK_OUT

XTAL_SEL

PARALLEL DATA

TIMING AND

CONTROL

SERIAL I/O PORT

2

AD9910

PROGRAMMING

REGISTERS

OUTPUT

SHIFT

KEYING

DATA

ROUTE

AND

PARTITION

CONTROL

3

INTERNAL CLOCK TIMING

AND CONTROL

ω

Acos (ω t + θ)

Asin (ω t + θ)

SYNC_SMP_ERR

SYNC_CLK

SYNC_OUT

SYNC_IN

PLL_LOCK

PLL_LOOP_FILTER

MASTER_RESET

2

2

DAC

14-BIT

DDS

AUX

DAC

8-BIT

AD9910ᅃాዃ14࿋ DACڦথຕጴೕ୲ࢇׯഗ

(DDS)Ljኧߛٳ1 GSPS֑ᄣ୲ăAD9910֑ᆩߛDDS

ጆ૧ຍLjሞփဎึႠీڦമ༵ူٷইگࠀࡼă

DDS/DACፇࢇࠓׯຕጴՊײڦߛೕఇెೕ୲ࢇׯ

ഗLjీࠕሞߛٳ400 MHzڦೕ୲ူิׯೕ୲যՎኟ၀հႚă

ᆩࢽᅜݡ࿚ෙ߲ᆩᇀDDSڦ႑ࡽ֖ຕLjԈઔǖ

ೕ୲Ă၎࿋ᇑናޗăDDS૧ᆩ32࿋ેഗ༵ࠃཌೕ

ࢅೕ୲ۙၿݴՐ୲ăሞ1 GSPS֑ᄣ୲ူLjۙၿݴՐ୲ሀ

ྺ0.23 HzăኄDDS࣏ํ၄କ၎࿋ᇑޗ܈ൎ࣑ࠀీă

ᆩࢽཚࡗزႜI/O܋ܔAD9910ڦాև٪ഗႜ

ՊײLjᅜํ၄ܔAD9910ڦăAD9910ׯକৢༀ

RAMLjኧೕ୲Ă၎࿋ࢅ/ናޗۙڦܠዖፇࢇă

AD9910࣏ኧᆩࢽۨᅭڦຕຕጴၽೢ߾ፕఇ๕ăሞఇ

๕ူLjೕ୲Ă၎࿋ናޗໜ้װ၍ႠՎࣅăAD9910ాዃ

ڦߛժႜຕ܋ీํ၄থೕ୲Ă၎࿋Ăናޗ

ࣅۙLjᅜኧ߸ߛڦۙࠀీă

AD9910ሞકቛڦ߾ᄽ࿒܈ݔྷా߾ፕ(ᇡକ߸ܠ႑

တLj൩֖ຕ֩ڦ“ܔፌٷܮۨኵ”ևݴ)ă

2. ၘဦ

剩余63页未读,继续阅读

Kevinjqk

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- zigbee-cluster-library-specification

- JSBSim Reference Manual

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0